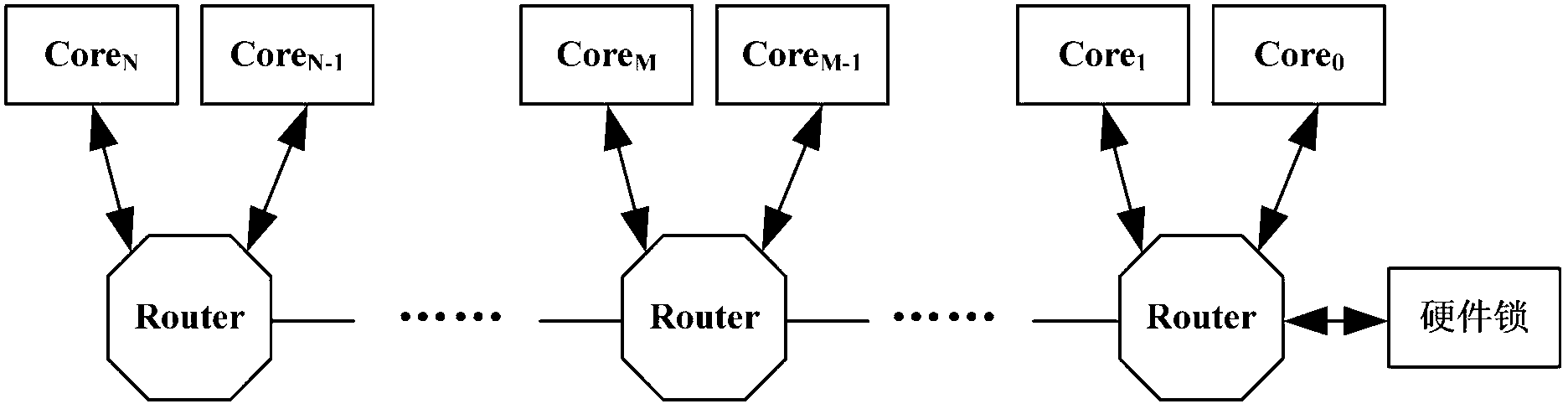

Hardware lock implementation method and device for multi-core processor

A technology of a multi-core processor and an implementation method, which is applied in the directions of multi-programming devices and resource allocation, etc., can solve the problems of unbalanced absolute delay in accessing hardware locks, reducing the application performance of hardware locks, increasing the time of lock synchronization, etc., and achieving improvement Lock synchronization efficiency, good scalability characteristics, and the effect of opportunity balance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

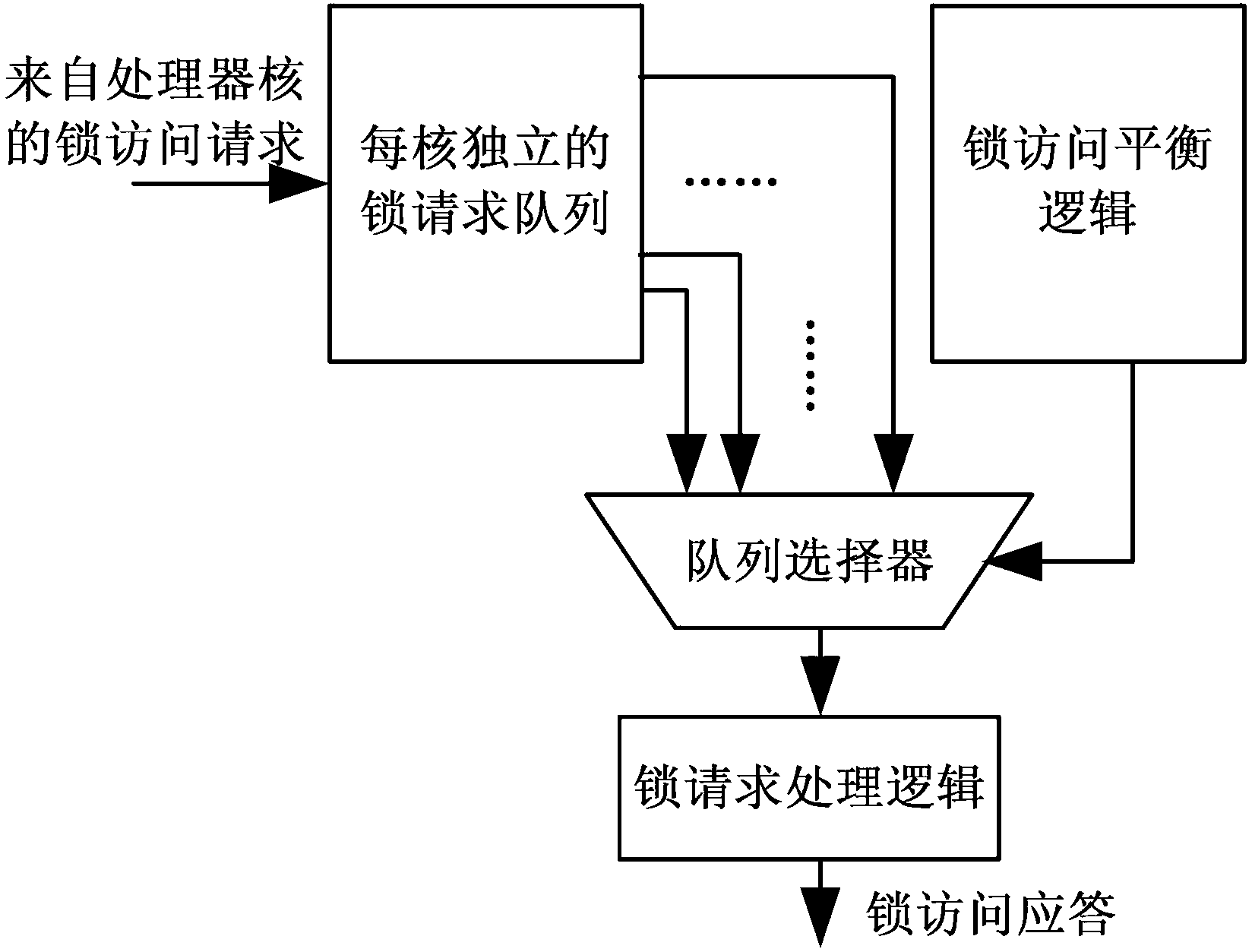

[0040] Such as figure 2 As shown, the implementation steps of the hardware lock implementation method for multi-core processors in this embodiment are as follows:

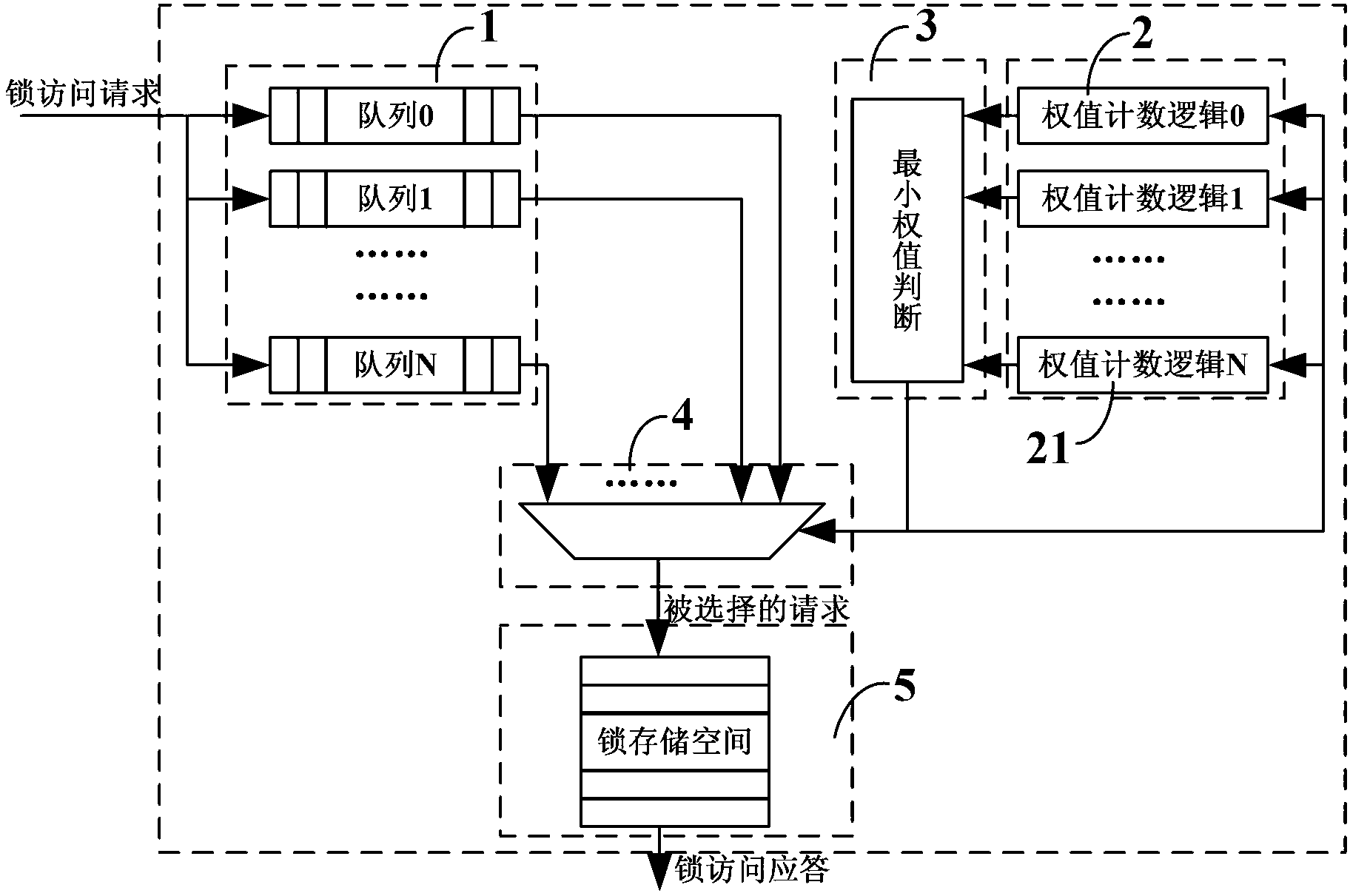

[0041]1) Establish a lock request queue corresponding to the processor core one by one, initialize and set the weight of each lock request queue, and cache the hardware lock access requests sent by each processor core through the lock request queue according to the principle of first-in-first-out;

[0042] 2) Obtain the minimum weight of the lock request queue, select the lock request queue corresponding to the minimum weight to obtain the service, increase the weight of the lock request queue after obtaining the service, and select the first entry from the lock request queue to obtain the service The hardware lock access request executes the lock storage space access operation and returns a response message.

[0043] In this embodiment, the detailed steps for initializing and setting the weights of each lock req...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More