On-chip communication method and device of integrated circuit based on asynchronous structure

An integrated circuit, asynchronous structure technology, applied in the direction of electrical digital data processing, instruments, etc., can solve the problems of not supporting information transmission, increasing the chip area and physical implementation difficulty, occupying wiring resources, etc., to achieve strong scalability, reduce physical Realization difficulty and the effect of reducing the occupancy of hardware resources

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

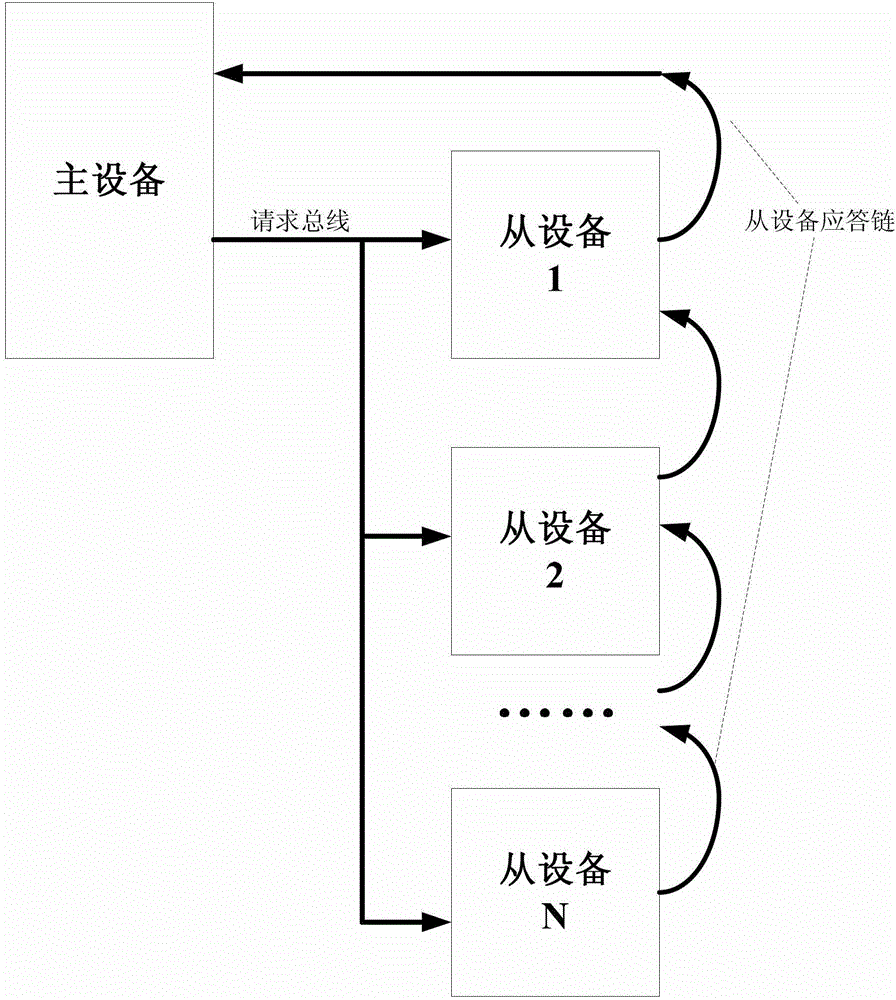

[0030] Such as figure 2 As shown, the implementation steps of the integrated circuit on-chip communication method based on the asynchronous structure in the embodiment of the present invention are as follows:

[0031]1) The master device is directly connected to the request interface of each slave device through the request bus in advance, and multiple slave device response interfaces are connected in series in advance to form a slave device response chain, and the slave device response interface located at the head of the slave device response chain is connected to the The master device is connected to the response interface, the slave device receives the request message composed of micropackets from the master device through the request bus, and the slave device sends the response message composed of micropackets to the master device through the slave device response chain;

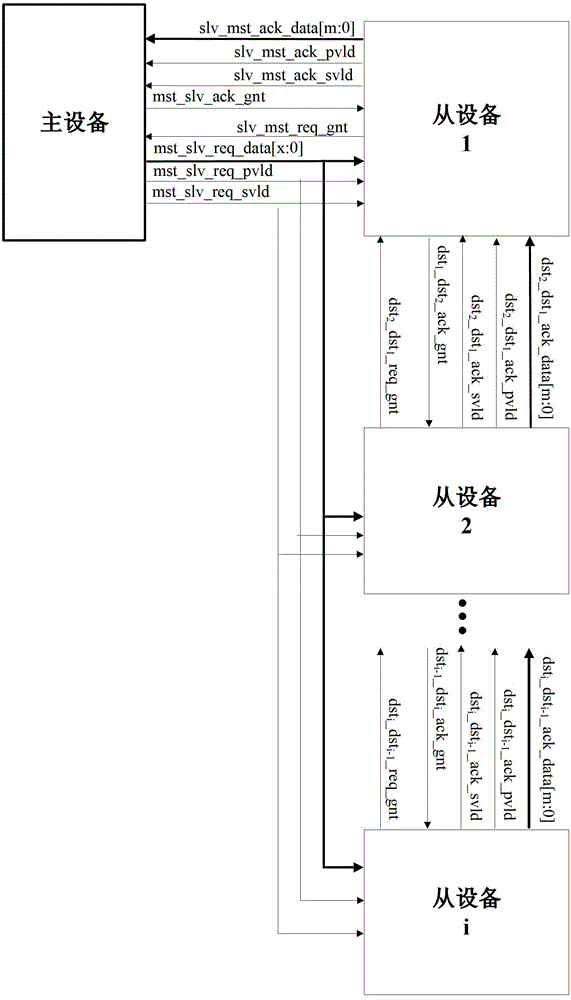

[0032] 2) When the master device sends a message to the slave device, the master device first divid...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More