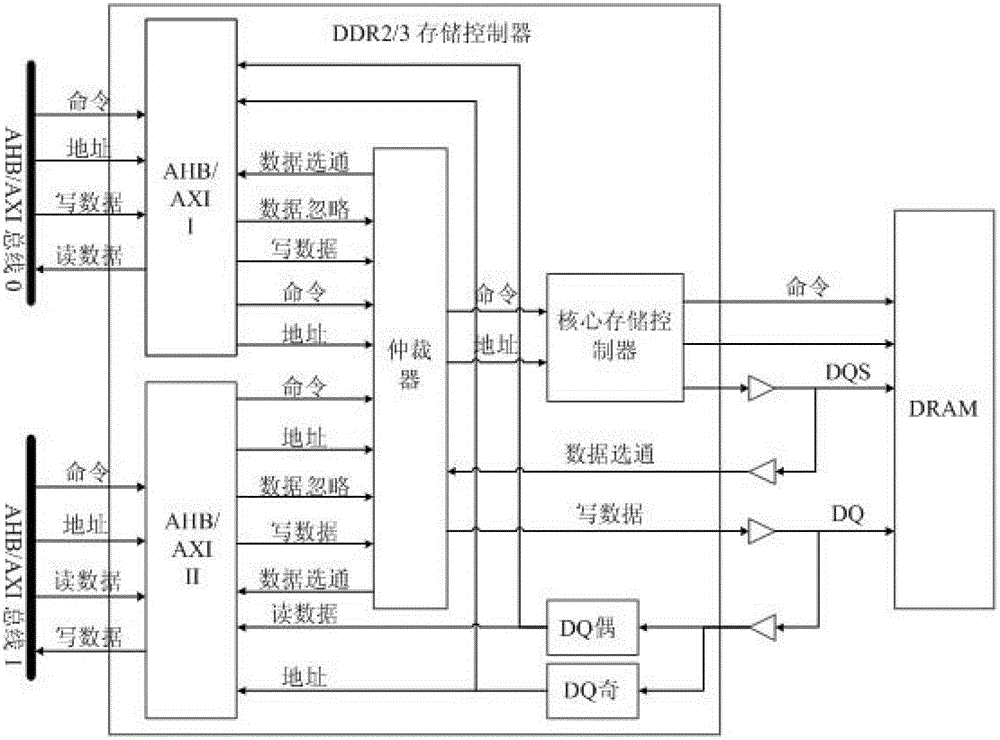

A kind of soc integrated multi-port ddr2/3 scheduler and scheduling method

A scheduler and multi-port technology, applied in the SoC storage field, can solve problems such as low effective bandwidth utilization and poor QoS, and achieve the effect of improving effective bandwidth utilization, improving QoS, and reducing average response time

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0025] Below in conjunction with accompanying drawing and specific embodiment, further illustrate the present invention, should be understood that these embodiments are only for illustrating the present invention and are not intended to limit the scope of the present invention, after having read the present invention, those skilled in the art will understand various aspects of the present invention Modifications in equivalent forms all fall within the scope defined by the appended claims of this application.

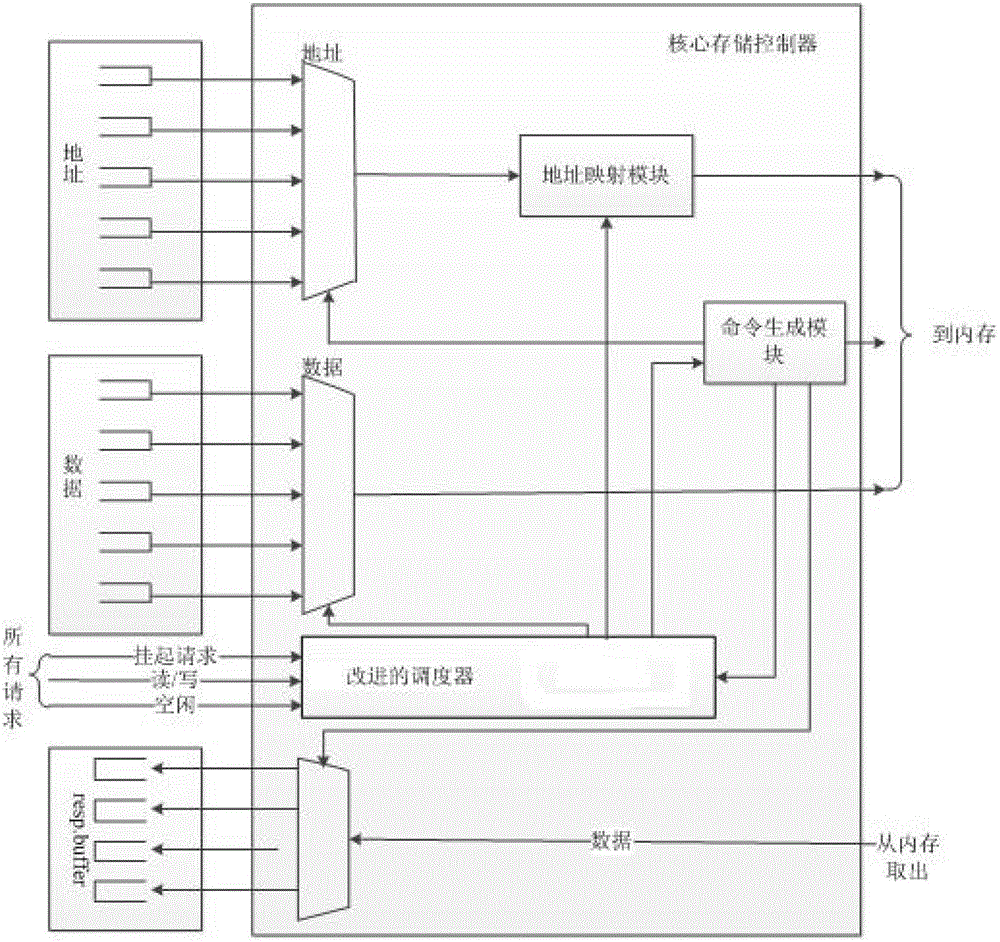

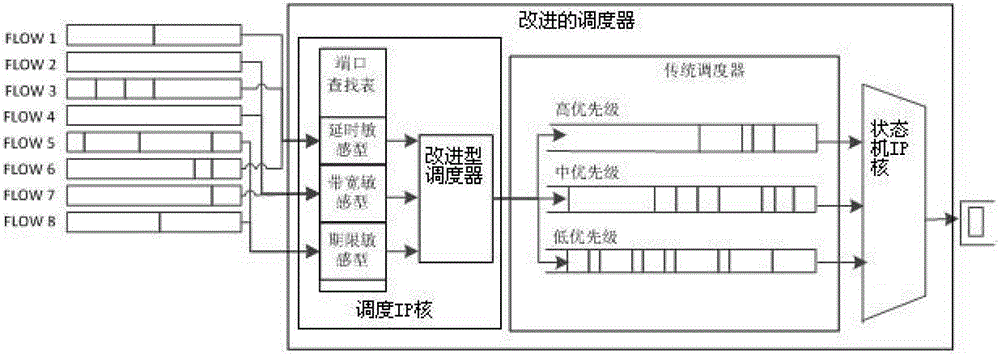

[0026] Such as figure 2 Shown is a block diagram of the core storage controller structure. In the core memory controller, the existing scheduler is replaced by an improved scheduler. Such as image 3 As shown, the improved scheduler is a scheduling IP core connected in series at the input end of the traditional scheduler, and a state machine IP core connected in series at the output end of the traditional scheduler.

[0027] Such as image 3 As shown, the scheduling...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More