Data buffering method in multi-core processor

A multi-core processor and data buffering technology, which is applied in the direction of electrical digital data processing, instruments, memory systems, etc., can solve the problems of long hit time, high algorithm complexity, false sharing, etc., and achieve reduced hit time and low algorithm complexity , the effect of improving the overall efficiency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

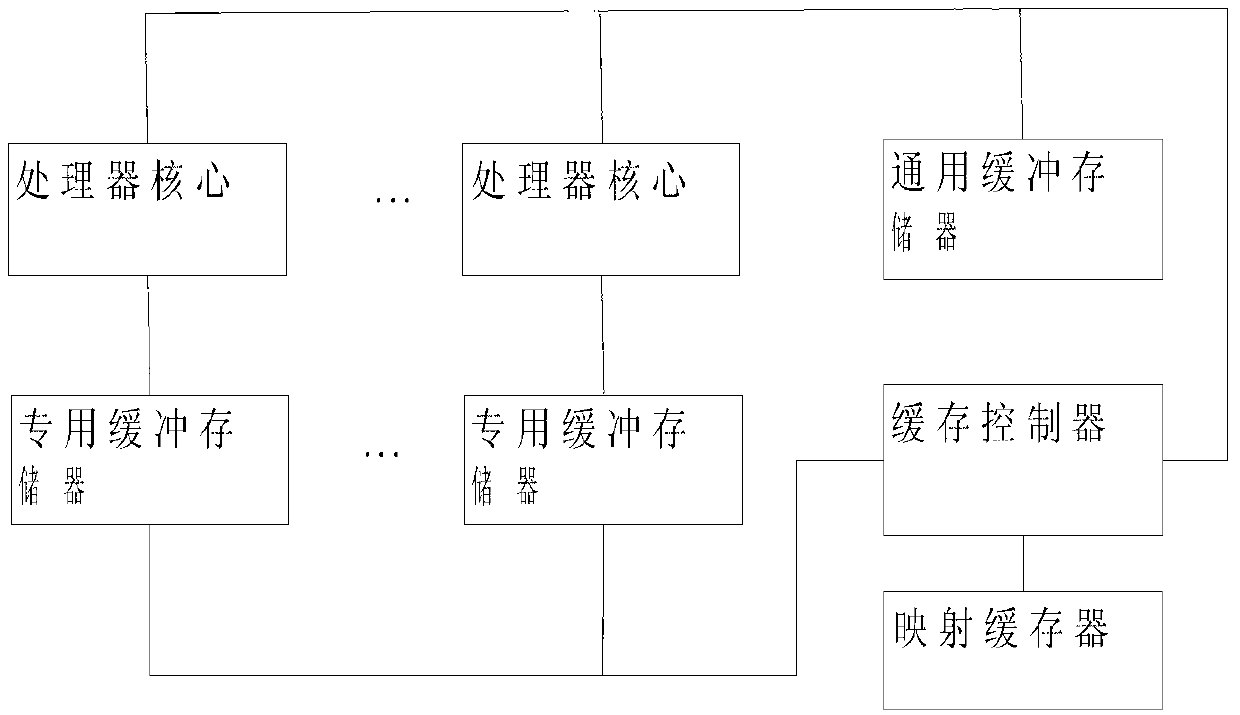

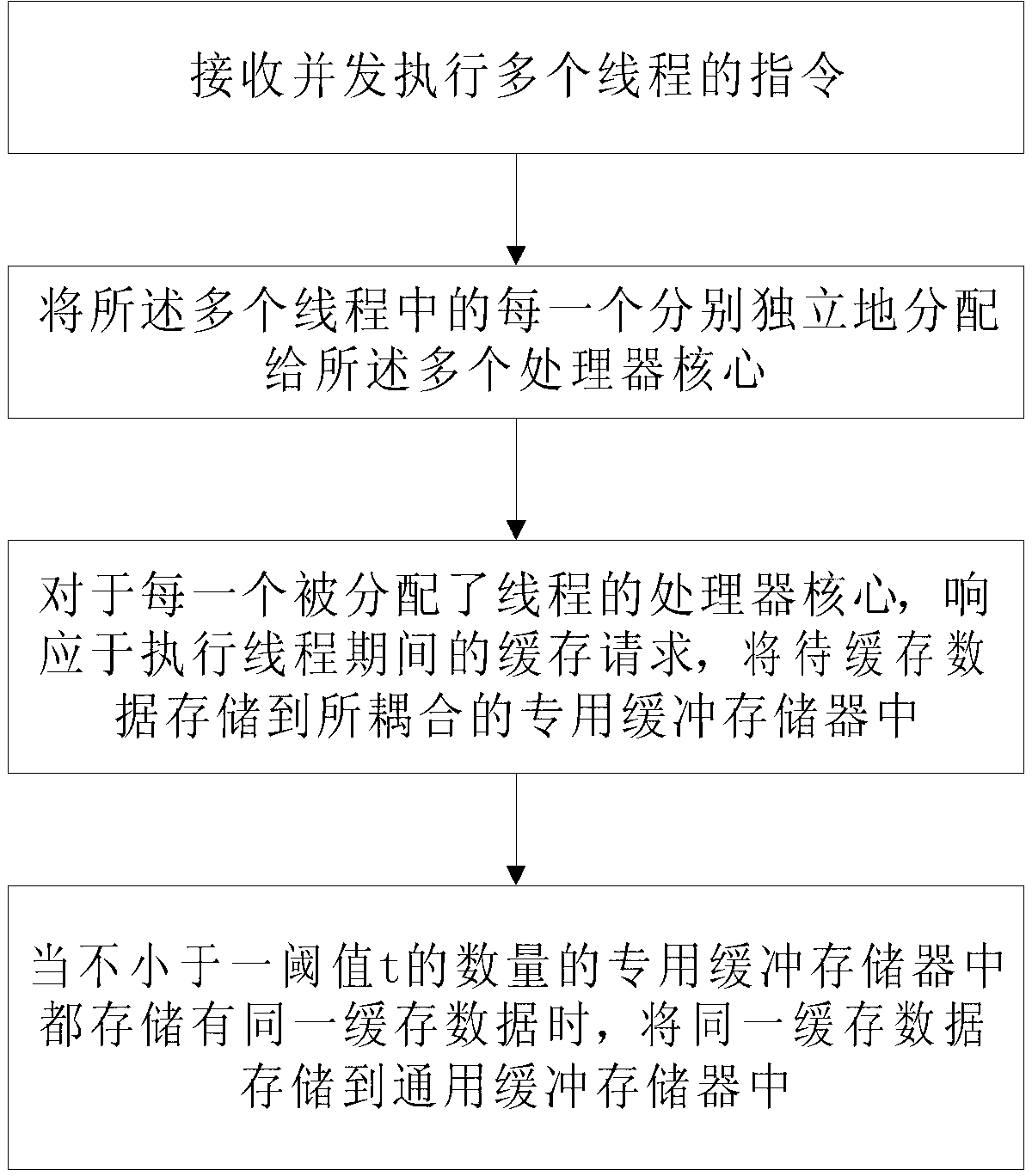

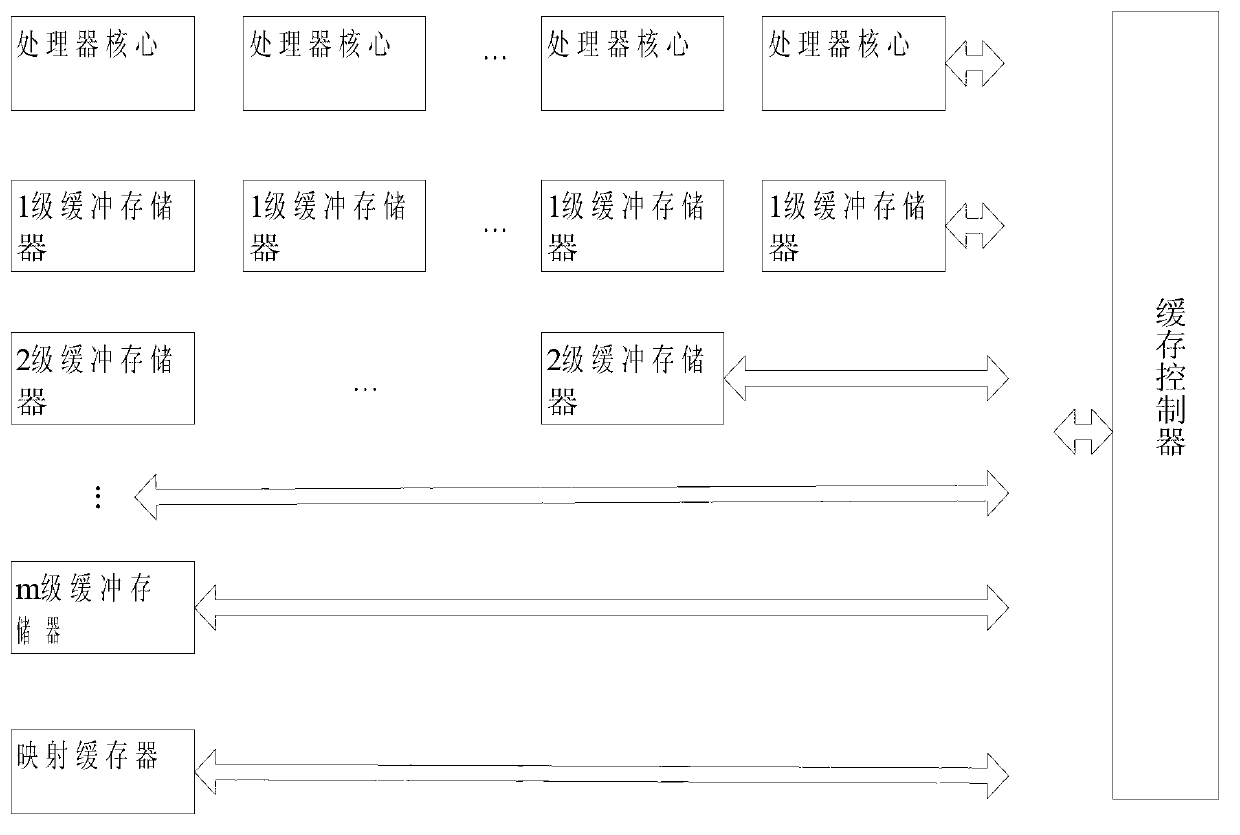

[0026] figure 1 Shows the structure block diagram of the multi-core processor involved in the present invention, such as figure 1 As shown, the multi-core processor in the present invention includes a plurality of processor cores, a plurality of dedicated buffer memories that form a one-to-one coupling relationship with the plurality of processor cores, and a plurality of dedicated buffer memories respectively coupled to the plurality of processor cores. A general-purpose buffer memory, wherein the plurality of dedicated buffer memories are only used to store cache data related to threads executed by a processor core coupled with the plurality of dedicated buffer memories, and the one general-purpose buffer memory is used for storing and Cache data related to threads executed by each processor core. The multi-core processor also includes a mapping buffer for storing a cache mapping table. The cache mapping table stores at least the storage relationship between the cache data a...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More