A multi-level gating device

A gating device and a technology for stage selection, applied in the field of memory, can solve the problem of low gating efficiency of a gating control signal

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

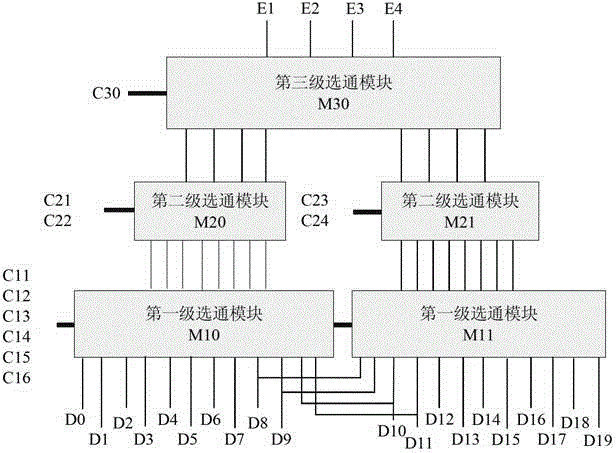

[0033] This embodiment is further described in detail based on the above solution.

[0034] One of the first-level gating modules is connected to twelve consecutive bit lines, and two of the first-level gating modules are connected by sharing four continuous bit lines; one of the first-level gating modules is connected through eight consecutive bit lines. The secondary bit line is connected to one of the second-level gating modules; one of the second-level gating modules is connected to the third-level gating module through four main bit lines.

[0035] Each of the first-level gating modules includes six gating control signal application terminals, and multiple first-level gating modules multiplex the six gating control signal application terminals;

[0036] Each of the second-level gating modules includes two gating control signal application terminals;

[0037] Each of the third-level gating modules is controlled by one of the third-level gating control signal application t...

Embodiment 2

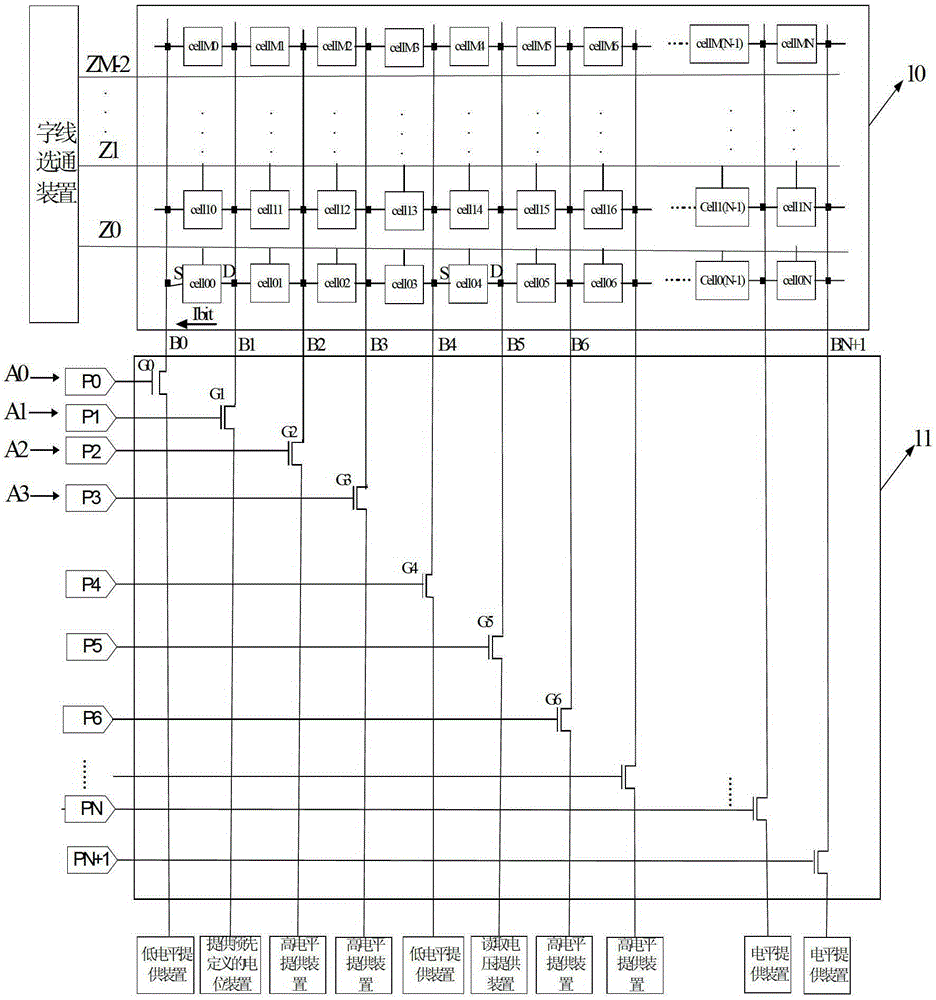

[0045] As a specific embodiment, this embodiment is based on the above-mentioned solution, specifically as follows: the first-level gating module includes eight tube units, each tube unit includes two to three gating tubes, and each tube unit The control signal connection ports of the strobe tubes are connected to the continuous odd bit lines or continuous even bit lines in the continuous bit lines, and each bit line is connected to the strobe tubes in a plurality of tube units; each of the first-stage strobe The module is controlled by six control signal application ends, and each control signal application end controls at least one gating tube. When multiple gating tubes can be controlled, the multiple gating tubes belong to different tube units ; The operation signal connection ports of the gate tubes in each tube unit are connected to the same secondary bit line; multiple first-level gate modules multiplex six control signal application ends, and among the multiple first-le...

Embodiment 3

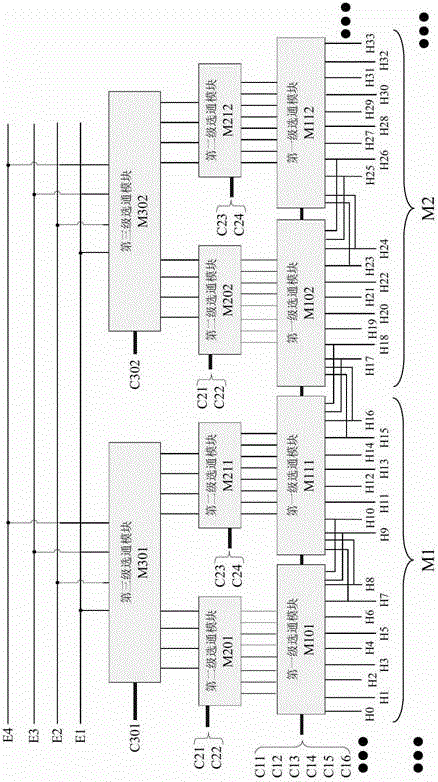

[0080] see Figure 4 , the embodiment shown is an extended multi-level bit line gating device, only two minimum expansion units are shown in the figure, and the remaining minimum expansion units are represented by ellipsis, including:

[0081] Multiple minimum expansion units: M1, M2..., each minimum expansion unit includes two first-level gating modules, two second-level gating modules, one third-level gating module, and one third-level control signal An application terminal, eight main bit lines and sixteen consecutive sub-bit lines; wherein, the third-level control signal application terminal is used to apply a gate control signal to the third-level gating module;

[0082] Ten control signal application terminals C11 to C16, C21 to C24 are used to apply bit line gating control signals generated by the decoder, among which six first-level control signal application terminals are used to apply to the first-level gating module The bit line gate control signals are respectivel...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More