High frequency clock duty ratio test circuit

A technology for testing circuits and high-frequency clocks, applied in the monitoring pulse chain mode and other directions, which can solve problems such as clock duty cycle testing, interference, and affecting the accuracy of test results.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

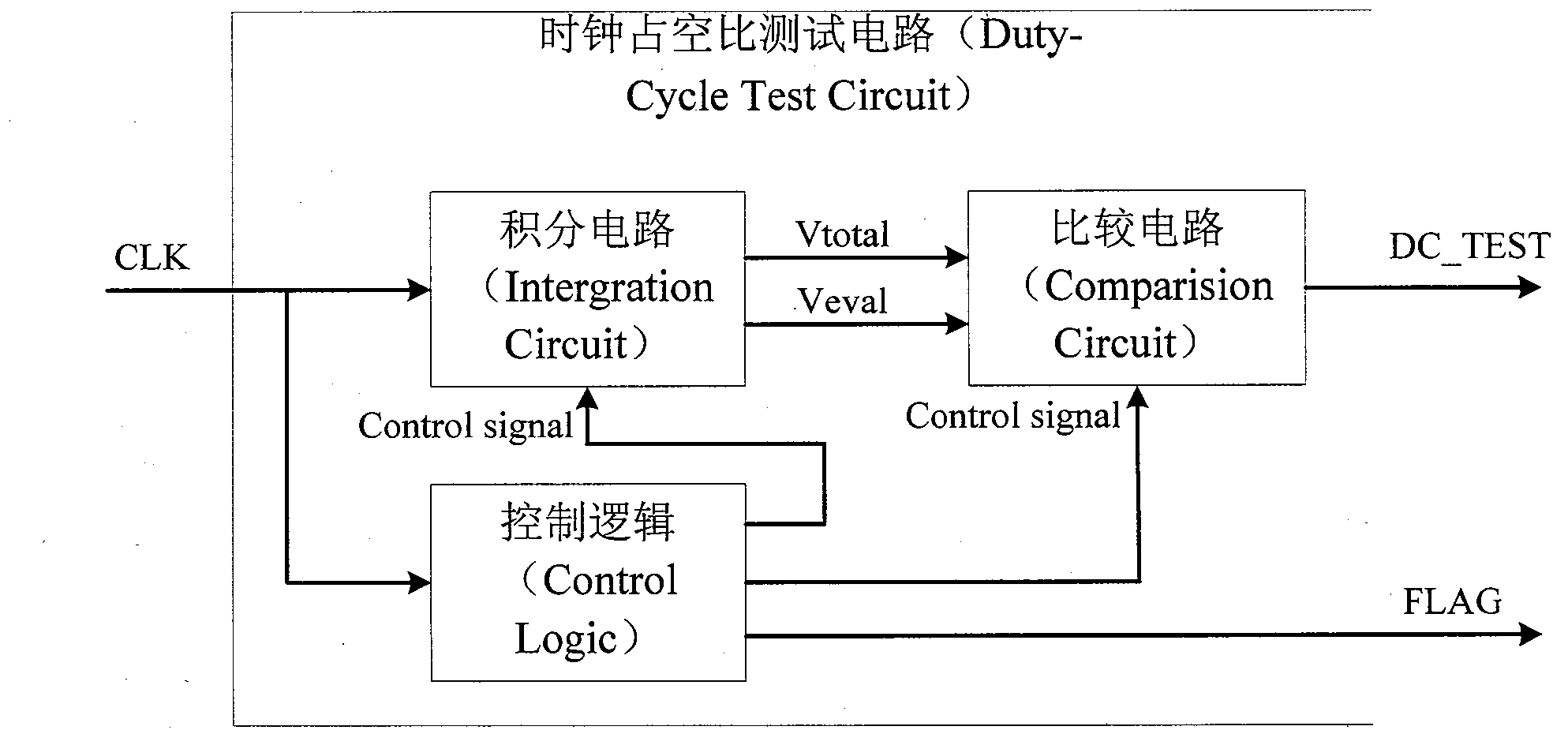

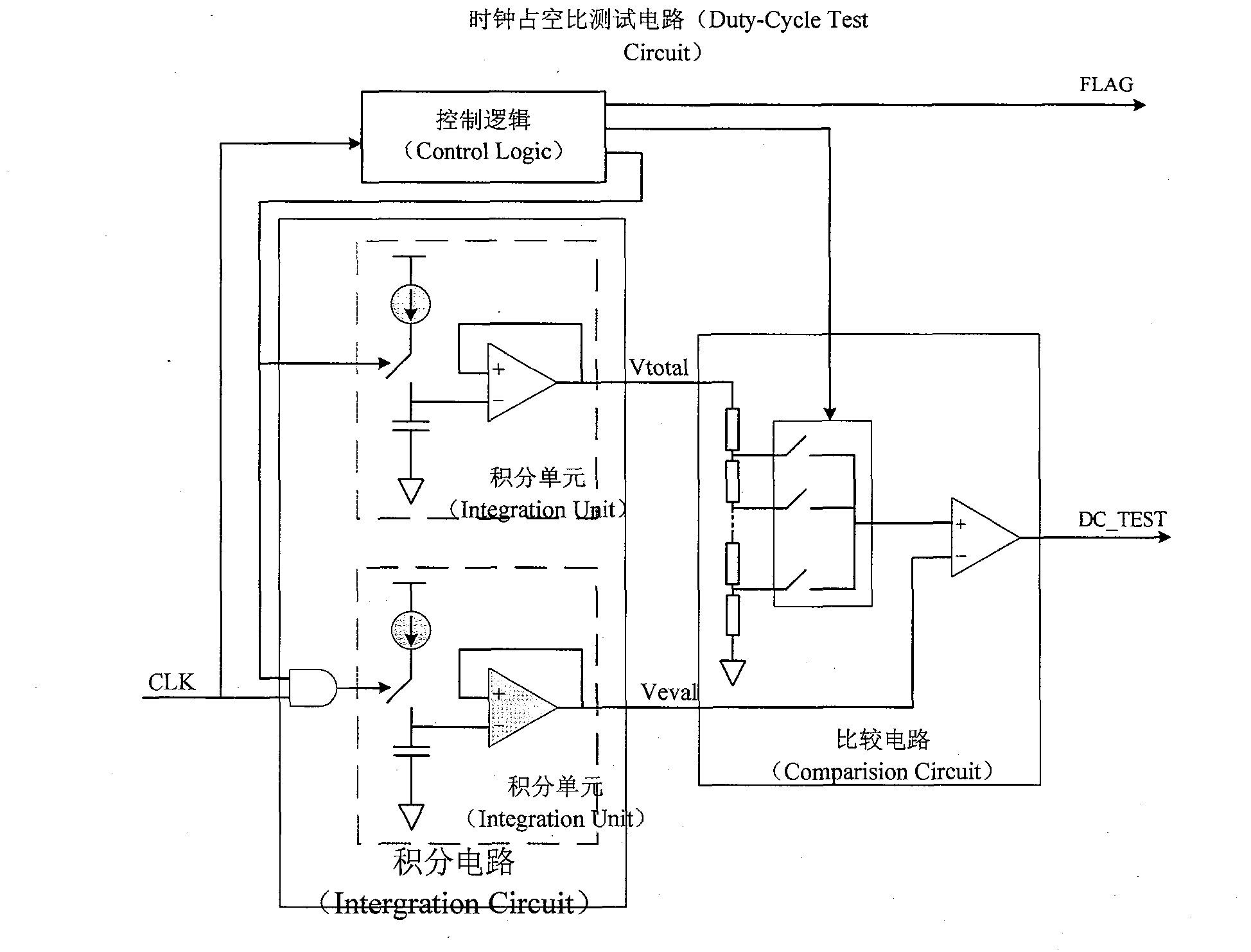

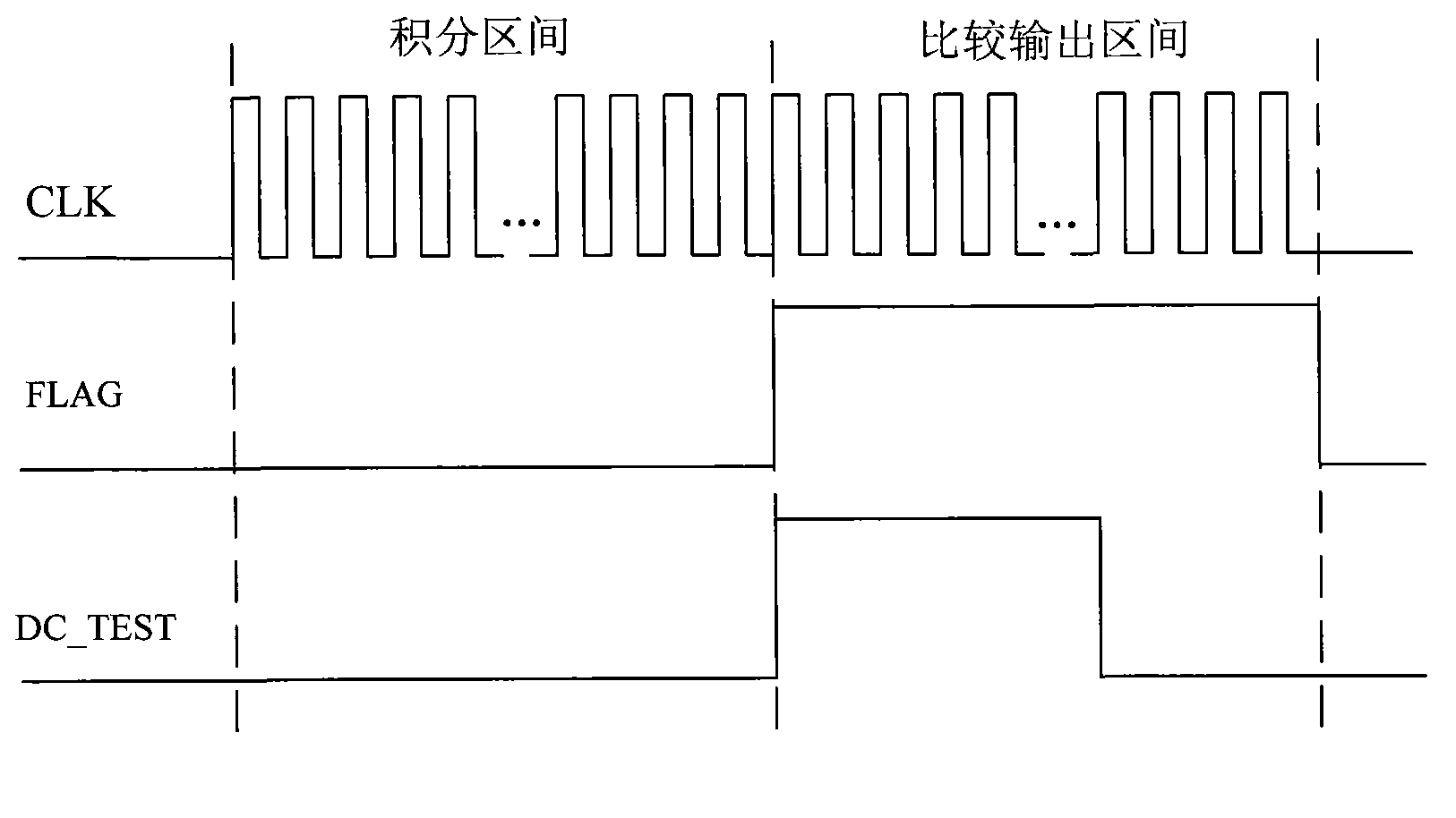

[0016] The circuit implementation structure is specifically introduced below in conjunction with the accompanying drawings, such as image 3 shown. The waveform diagram of each node inside the circuit, such as Figure 4 shown.

[0017] The integral circuit is controlled by the counter inside the control logic, and integrates within N clock cycles. The integral unit is composed of a switched capacitor charge and discharge circuit and a source follower circuit. The source follower circuit makes the integral output voltage have a certain current drive capability to divide the voltage. Generate the reference voltage required by the comparison circuit. The control circuit outputs a signal CON representing the integration interval, and CON is used as an input of an integration unit to generate a reference voltage Vtotal. The AND of the integration interval signal CON and the clock signal CLK is used as an input of another integration unit to generate an evaluation voltage Veval. ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More