A Multi-property Prediction Method for Semiconductor Manufacturing Processes

A manufacturing process and performance prediction technology, which is applied in the field of multi-performance prediction of semiconductor manufacturing process using Bayesian neural network, can solve problems such as inability to accurately and timely obtain the optimal scheduling plan, difficulty in control, complex structure of the prediction model, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0069] In order to better understand the technical solutions of the present invention, the implementation manners of the present invention will be further introduced below.

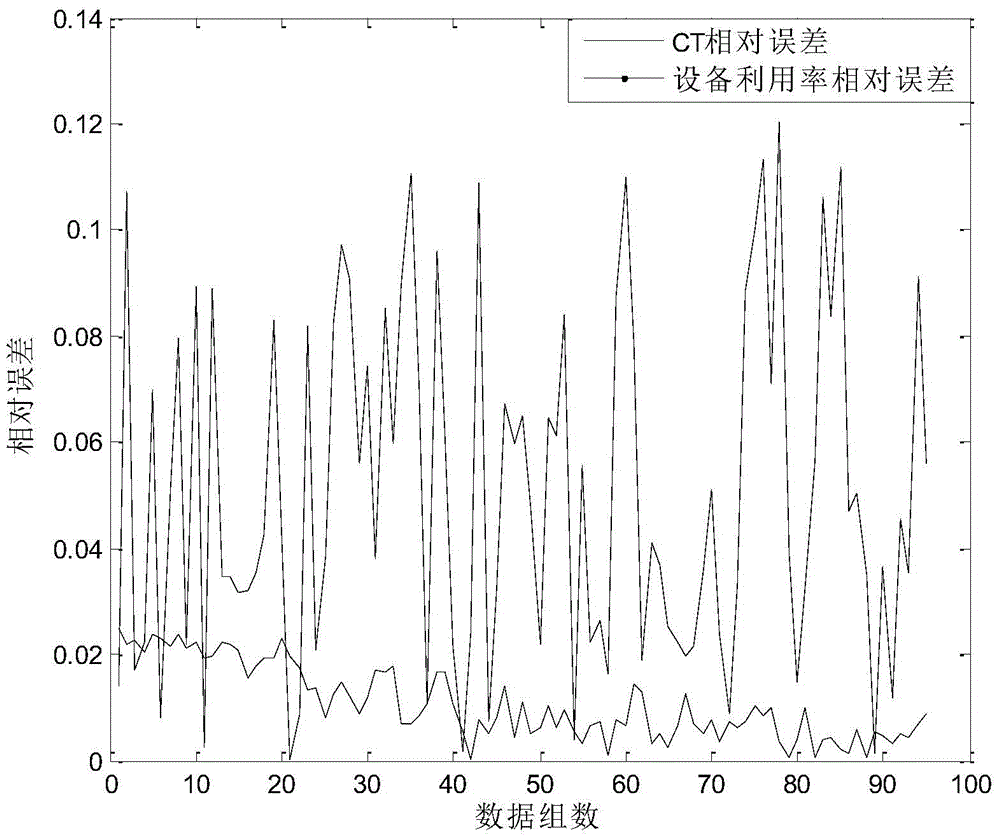

[0070] Take the semiconductor production scheduling standard model HP24 as an example for specific implementation. The model consists of 24 machining centers, with a total of 72 equipment, and the detailed parameters of some equipment are shown in Table 1.

[0071] Table 1 Some equipment parameters in the standard model HP24

[0072]

[0073]

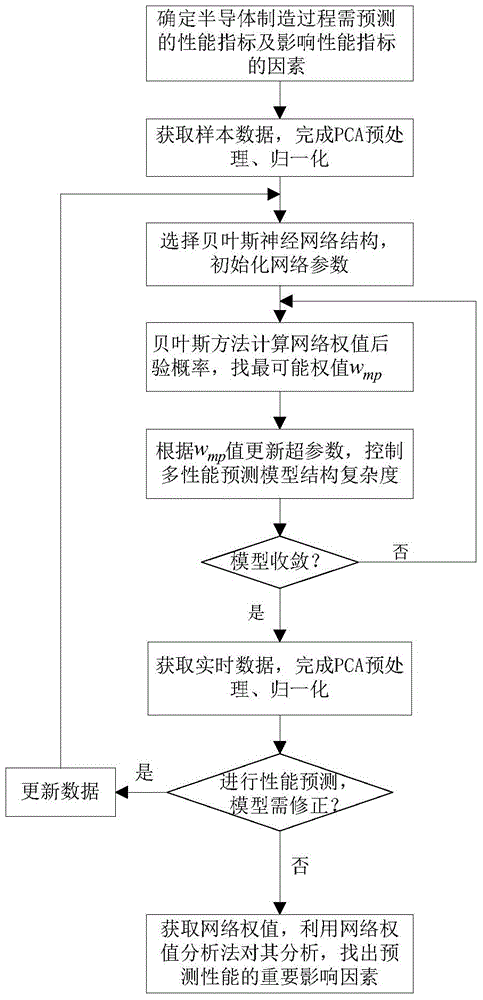

[0074] The HP24 standard model is used for simulation on the Plant Simulation simulation platform. The dispatching rule adopts FIFO (First In First Out), the feeding strategy adopts CONWIP, the simulation time is set to 2 years (17280 hours), and the pre-simulation time is set to half a year (4320 hours). Hour). figure 1 It is a flow chart of the prediction method, including the following steps:

[0075] Step 1, determine the performance index to be predic...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More