Method for measuring electric leakage of PMOS device

A measurement method and device technology, applied in semiconductor/solid-state device testing/measurement, circuits, electrical components, etc., can solve problems such as increase and inaccurate test data

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0016] In order to make the content of the present invention clearer and easier to understand, the content of the present invention will be described in detail below in conjunction with specific embodiments and accompanying drawings.

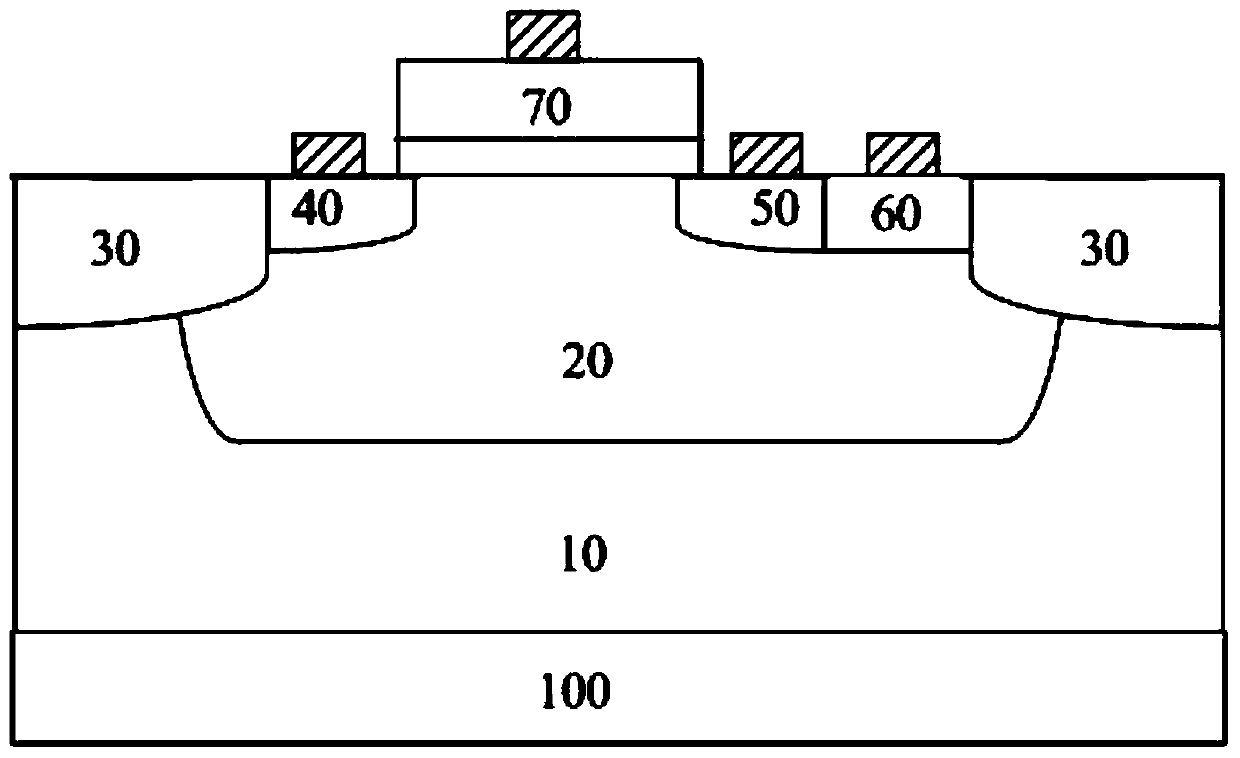

[0017] image 3 It schematically shows a leakage measurement structure of a PMOS device according to a preferred embodiment of the present invention.

[0018] Such as image 3 As shown, the PMOS device leakage measurement method according to a preferred embodiment of the present invention includes:

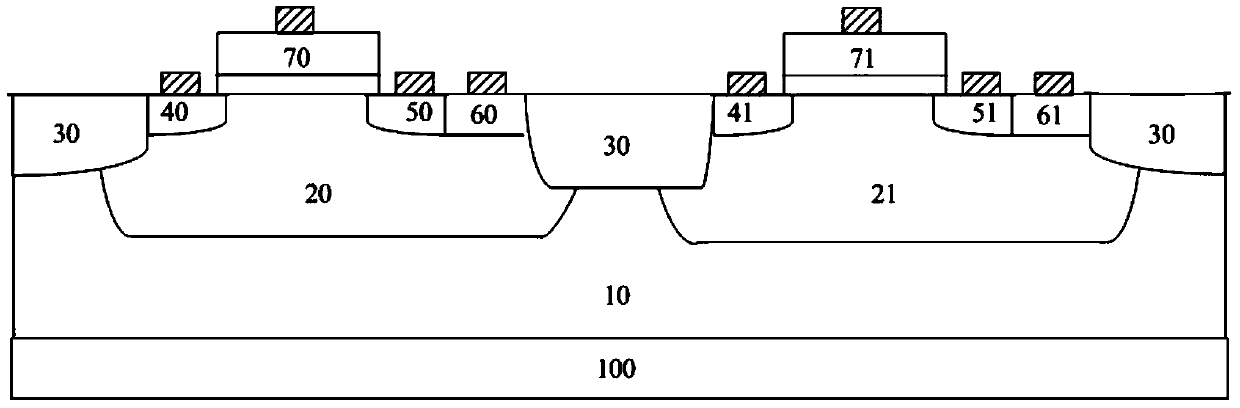

[0019] A wafer formed with a CMOS device is placed on a test tray 100, wherein the CMOS device includes a paired PMOS device and an NMOS device formed on the same substrate 10; and the PMOS device includes an N well formed in the substrate 10 20 in the P-type drain 40, P-type source 50 and N-type body contact region 60, the PMOS device also includes a base 70 formed on the substrate 10; the NMOS device includes a P well formed in the substrate 10 ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More