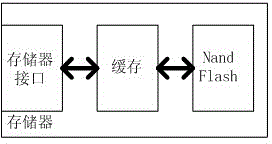

Flash error detection method and device for reducing influence on performance of interface of storage

A memory interface and error detection technology, which is applied in the direction of redundant code error detection and response error generation, can solve problems such as ECC unit data failure, and achieve the effect of improving efficiency and having little impact on performance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

specific Embodiment 1

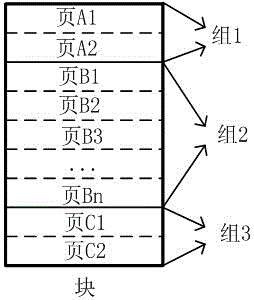

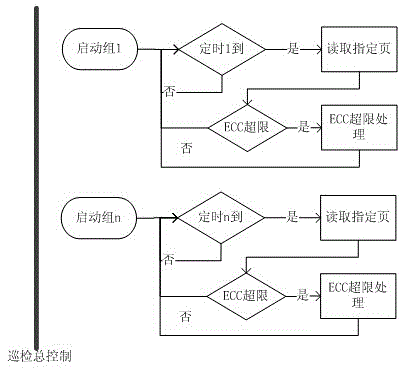

[0030] In this specific embodiment, based on the actual situation of the granule, according to the physical characteristics of each page of the flash memory, the pages in a block are divided into different groups according to the difference in the speed of ECC growth, and the pages in the group are more likely to have Bit flips In the case of , the higher the corresponding weight, the shorter the corresponding total cycle time. In the actual inspection operation, different inspection cycles are allocated according to different groups. The page with faster ECC growth has a shorter inspection cycle, and vice versa. According to the actual differences of each page, the ECC inspection cycle is set separately, and the interface performance pressure of Nand Flash flash memory will be smaller than that of the existing solution, which means that the performance impact on the external interface of the memory is small.

[0031] The product of the single timing time in a group and all th...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More