Memory architecture with wiring structure enabling different access patterns in multiple dimensions

A technology of multiplexers and functional circuits, applied in static memory, instruments, measuring devices, etc., can solve problems such as cycle delay growth

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

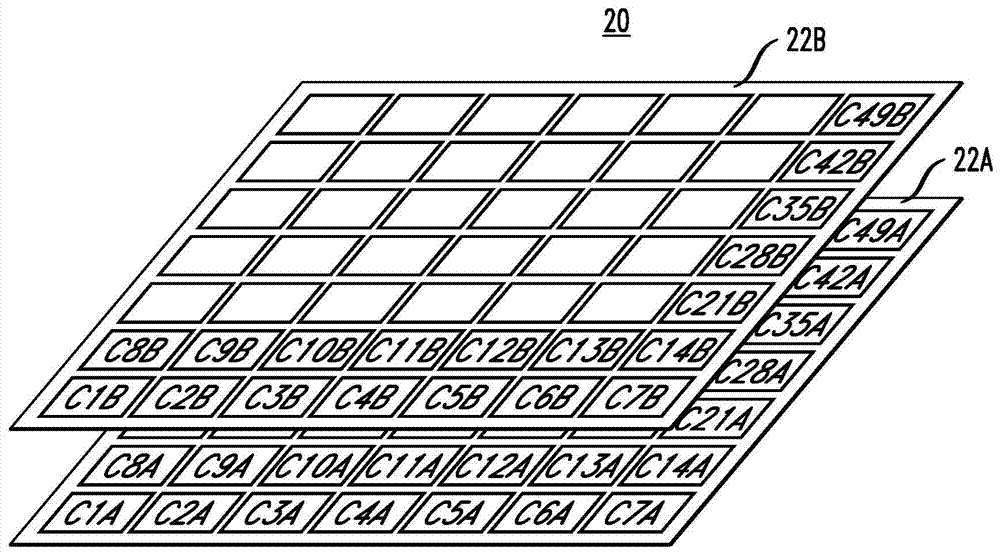

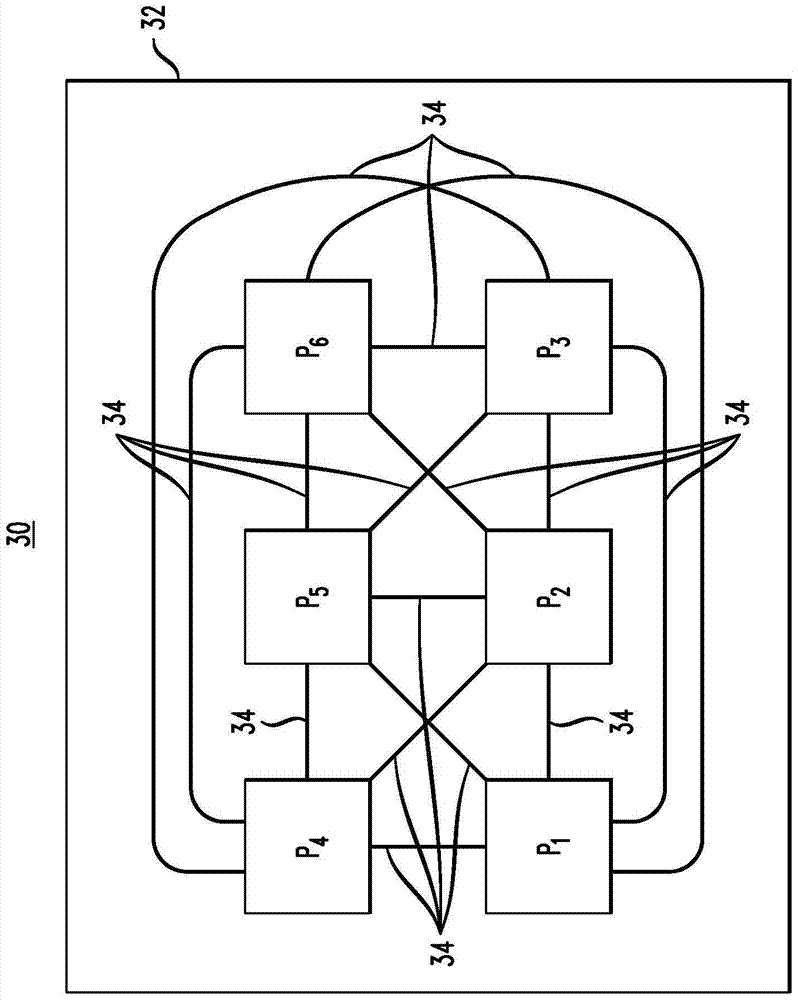

[0058] Concerning 3-D multiprocessor devices formed by connecting multiple processors in a stacked configuration, and for controlling 3-D stacked multiprocessor devices to operate selectively in one of multiple resource pooling and sharing modes The method, the exemplary embodiment of the present invention will be described in further detail.

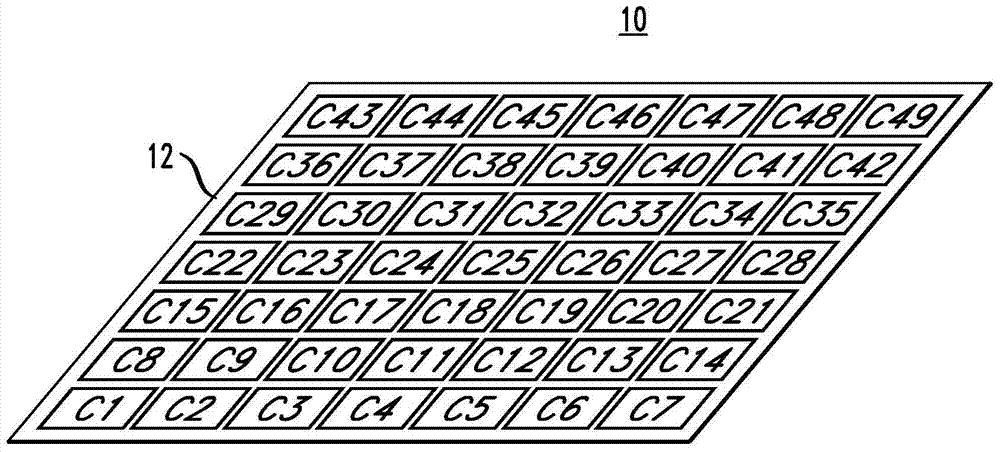

[0059] figure 1 is a schematic diagram of a multiprocessor chip to which the principles of the present invention may be applied. specifically, figure 1 A multiprocessor chip 10 is schematically depicted, comprising a semiconductor die 12 with a plurality of processors C1, C2, . . . , C49 (generally denoted Cn) on a die 12 . The processors Cn are arranged in a "planar" system, where each processor Cn has its own dedicated footprint in 2-D space. As already understood by those skilled in the art, in a 2-D plane, using horizontal wiring and electrical connections formed as part of the BEOL (back end of line) structure of the chip 10, th...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More