A kind of shift register, its driving method and gate driving circuit

A shift register and gate technology, which is applied in the field of shift registers and gate drive circuits, can solve problems such as the design of narrow borders that are unfavorable for display panels.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

example 1

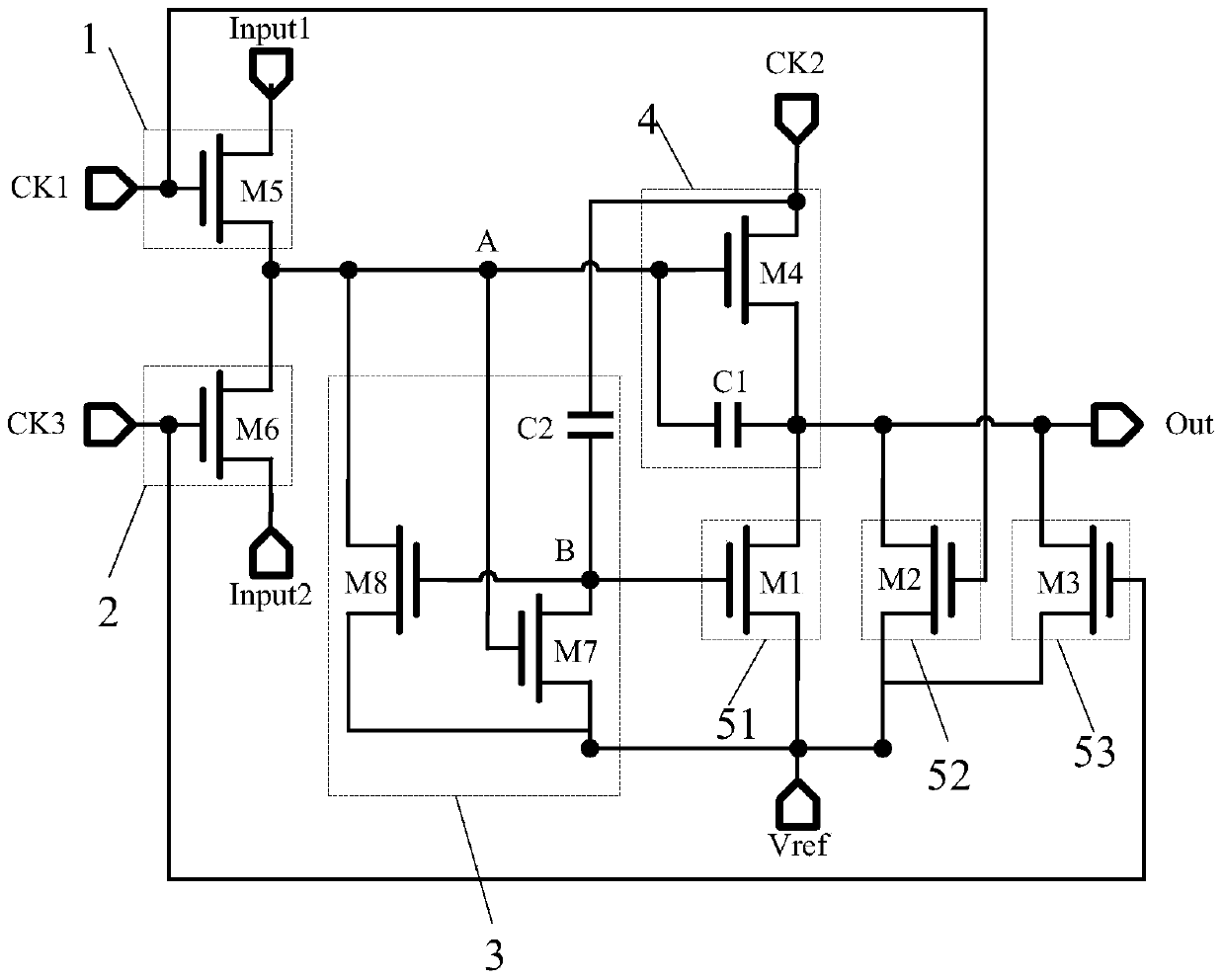

[0107] by Figure 5 The input-output timing diagram shown is an example for image 3 The working process of the shift register shown is described, specifically, select as Figure 5 The six stages of T1 ~ T6 in the input and output sequence diagram shown.

[0108] In the T1 stage, Input1=1, Input2=0, CK1=1, CK2=0, CK3=0.

[0109] Since CK1=1, the second switch transistor M2 and the fifth switch transistor M5 are turned on, and the turned-on fifth switch transistor M5 provides the high potential signal of the first input signal terminal Input1 to the first node A, so the first node A The potential of the second node B is the high potential, the fourth switch transistor M4 and the seventh switch transistor M7 are turned on, and the turned-on seventh switch transistor M7 provides the low potential signal of the reference signal terminal Vref to the second node B, and the potential of the second node B The turned-on fourth switch transistor M4 supplies the low-potential signal o...

example 2

[0122] by Figure 6 The input-output timing diagram shown is an example for Figure 4 The working process of the shift register shown is described, specifically, select as Figure 6 The six stages of T1 ~ T6 in the input and output sequence diagram shown.

[0123] In the T1 stage, Input1=0, Input2=1, CK1=0, CK2=1, CK3=1.

[0124]Since CK1=1, the second switch transistor M2 and the fifth switch transistor M5 are turned on, and the turned-on fifth switch transistor M5 provides the low potential signal of the first input signal terminal Input1 to the first node A, so the first node A The potential of the second node B is low, the fourth switch transistor M4 and the seventh switch transistor M7 are turned on, and the turned-on seventh switch transistor M7 provides the high potential signal of the reference signal terminal Vref to the second node B, and the potential of the second node B The turned-on fourth switching transistor M4 supplies the high-potential signal of the secon...

PUM

Login to view more

Login to view more Abstract

Description

Claims

Application Information

Login to view more

Login to view more - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap