Low warping coreless substrate and semiconductor assembly using the same

A coreless substrate and semiconductor technology, applied in semiconductor devices, semiconductor/solid-state device parts, electric solid-state devices, etc., can solve problems that cannot be widely adopted, coreless substrates are warped, and cannot be solved. The effect of overall rigidity and local warping

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

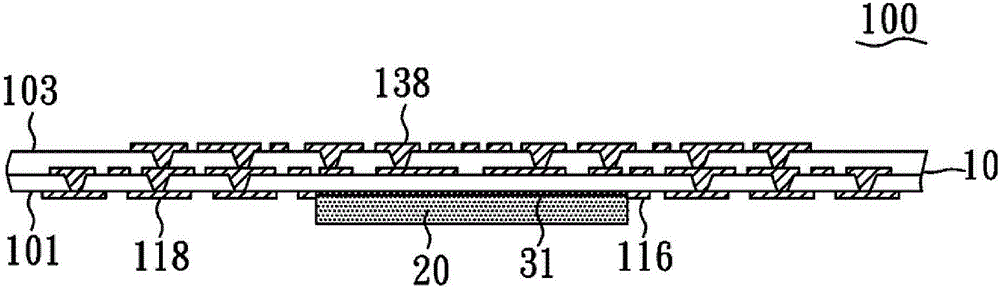

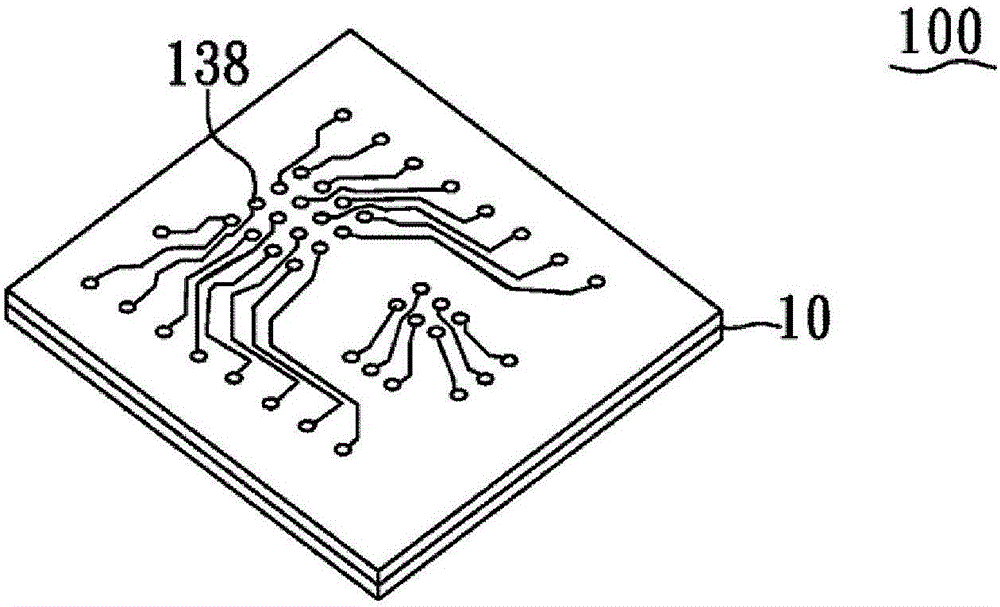

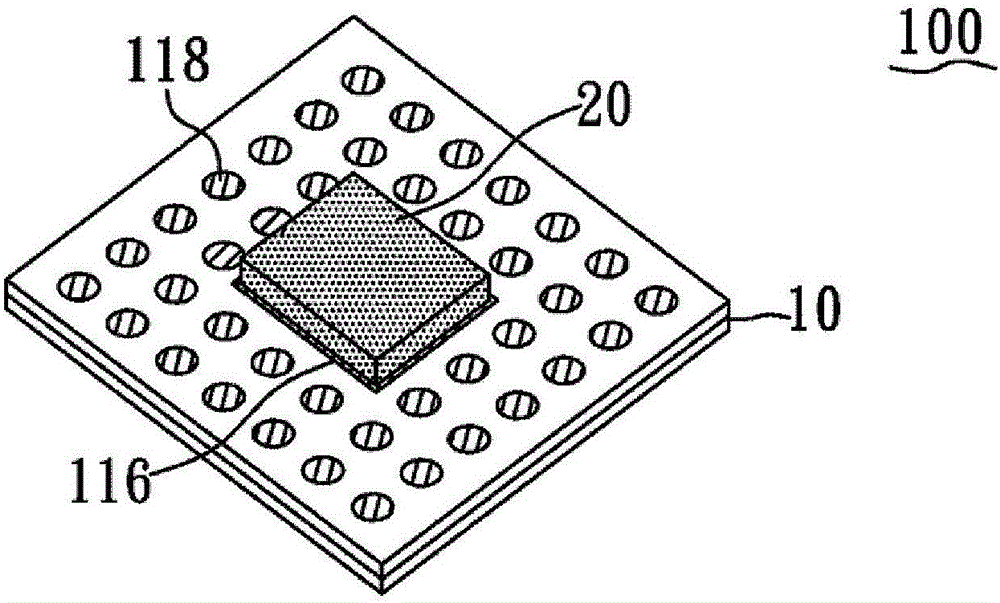

[0041] figure 1 , 2 and 3 are respectively a cross-sectional view, top and bottom perspective views of a low warpage coreless substrate 100 in an embodiment of the present invention, which includes a build-up circuit 10 and a bending resistance control member 20 .

[0042] Build-up circuit 10 has a bottom side 101 , an opposite top side 103 , contact pads 118 at bottom side 101 , and bond pads 138 at top side 103 . The contact pads 118 are formed outside the central area of the bottom side 101 and are electrically coupled to the bonding pads 138 through vertical and lateral routing. In this figure, the pad pitch and pad size of the contact pads 118 are larger than the pad pitch and pad size of the bonding pads 138 , and the pad pitch and pad size of the bonding pads 138 are consistent with the I / O pads of the semiconductor device subsequently placed thereon. Thus, the semiconductor device with fine pads can be electrically coupled to the top side 103 of the build-up circui...

Embodiment 2

[0056] Figure 14 and 15 They are respectively a cross-sectional view and a top perspective view of another low warpage coreless substrate 200 in another embodiment of the present invention, which further includes a reinforcement layer.

[0057] In this embodiment, the low-warpage coreless substrate 200 is similar to that described in Embodiment 1, but the difference lies in that a reinforcement layer 40 is further provided on the top side 103 of the build-up circuit 10 . The reinforcement layer 40 has a through opening 405 extending through the reinforcement layer 40 between the top side and the bottom side, and is attached to the top side 103 of the build-up circuit 10 by the adhesive 33 . The reinforcement layer 40 covers the peripheral edge at the top side 103 of the build-up circuit 10, and the bonding pads 138 of the build-up circuit 10 are aligned with the through opening 405 of the reinforcement layer 40, and are exposed from above at the through opening 405 of the re...

PUM

Login to view more

Login to view more Abstract

Description

Claims

Application Information

Login to view more

Login to view more - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap