High-speed vertical channel three-dimensional NAND memory device

A memory and storage unit technology, applied in read-only memory, static memory, information storage, etc., can solve problems such as increased power consumption, increased number of string selection lines, and slow down component operations

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0050] The following descriptions can provide any person of ordinary skill in the technical field with tools to use and make the present invention. The contents of this description are only provided for specific application and demand backgrounds. Modifications to the disclosed embodiments can be made by persons of ordinary skill in the art, and the general principles disclosed herein will be applicable to other embodiments and applications without departing from the spirit and scope of the invention. Therefore, the embodiments are presented only to illustrate the technical features of the present invention, not to limit the claims of the present invention.

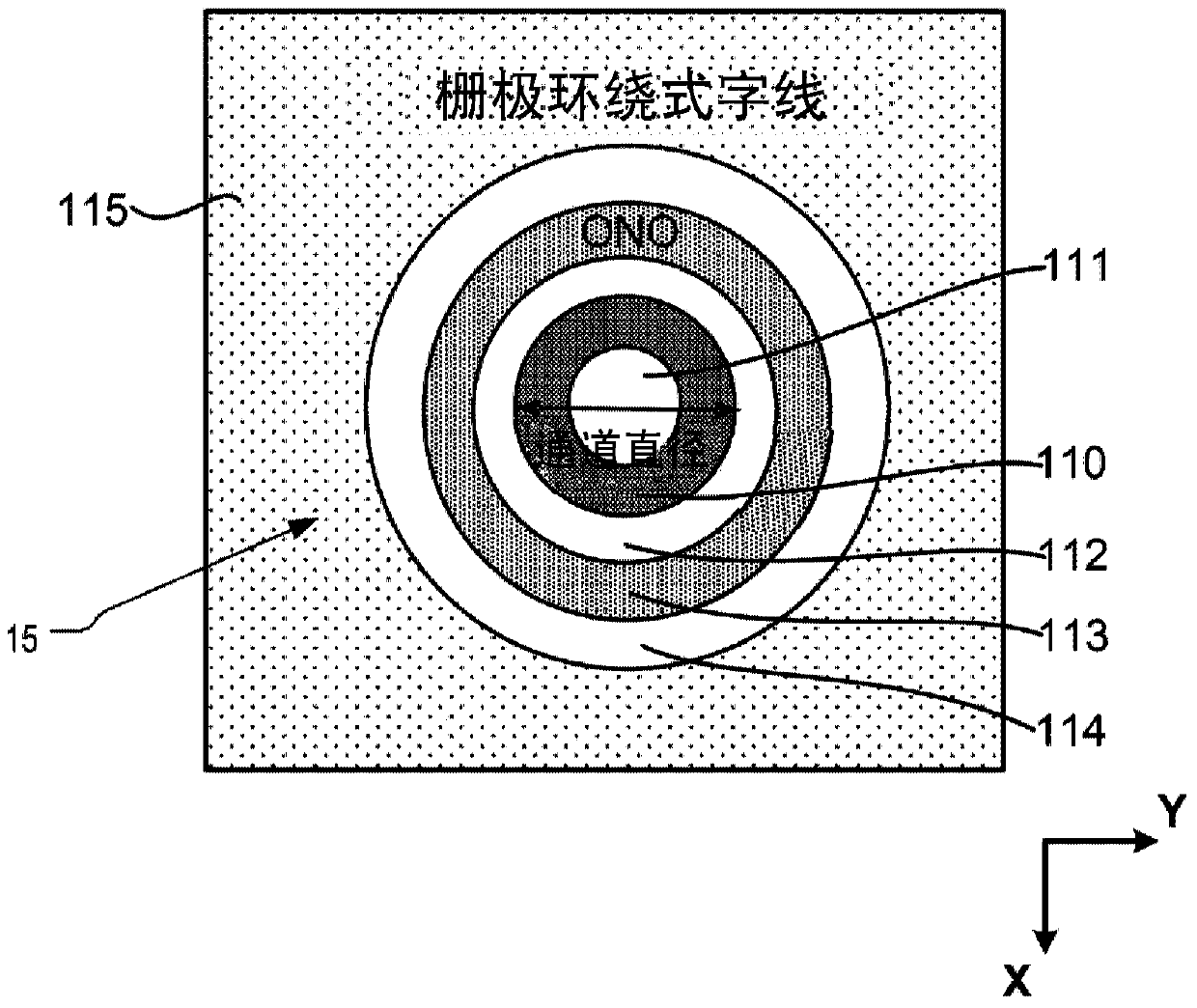

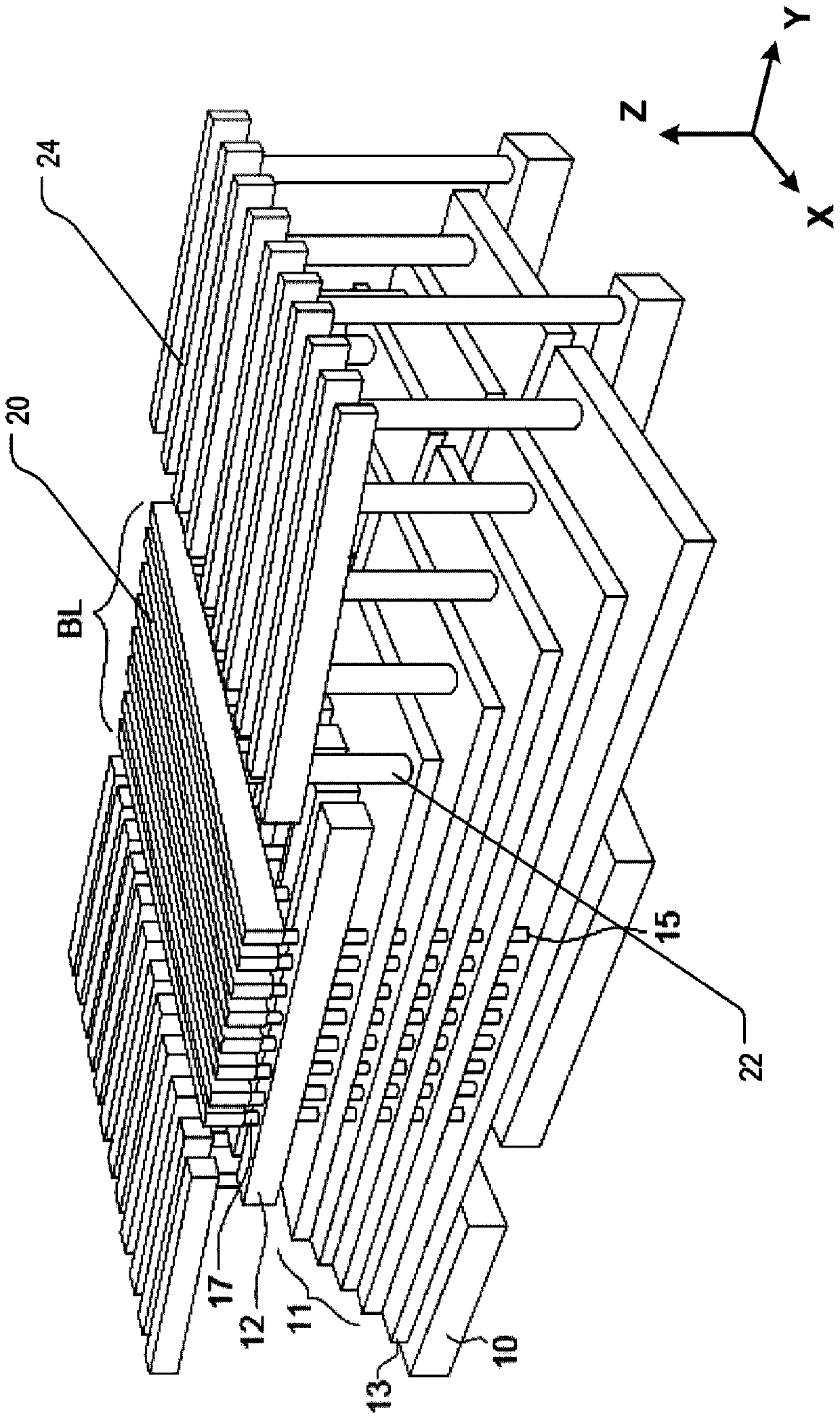

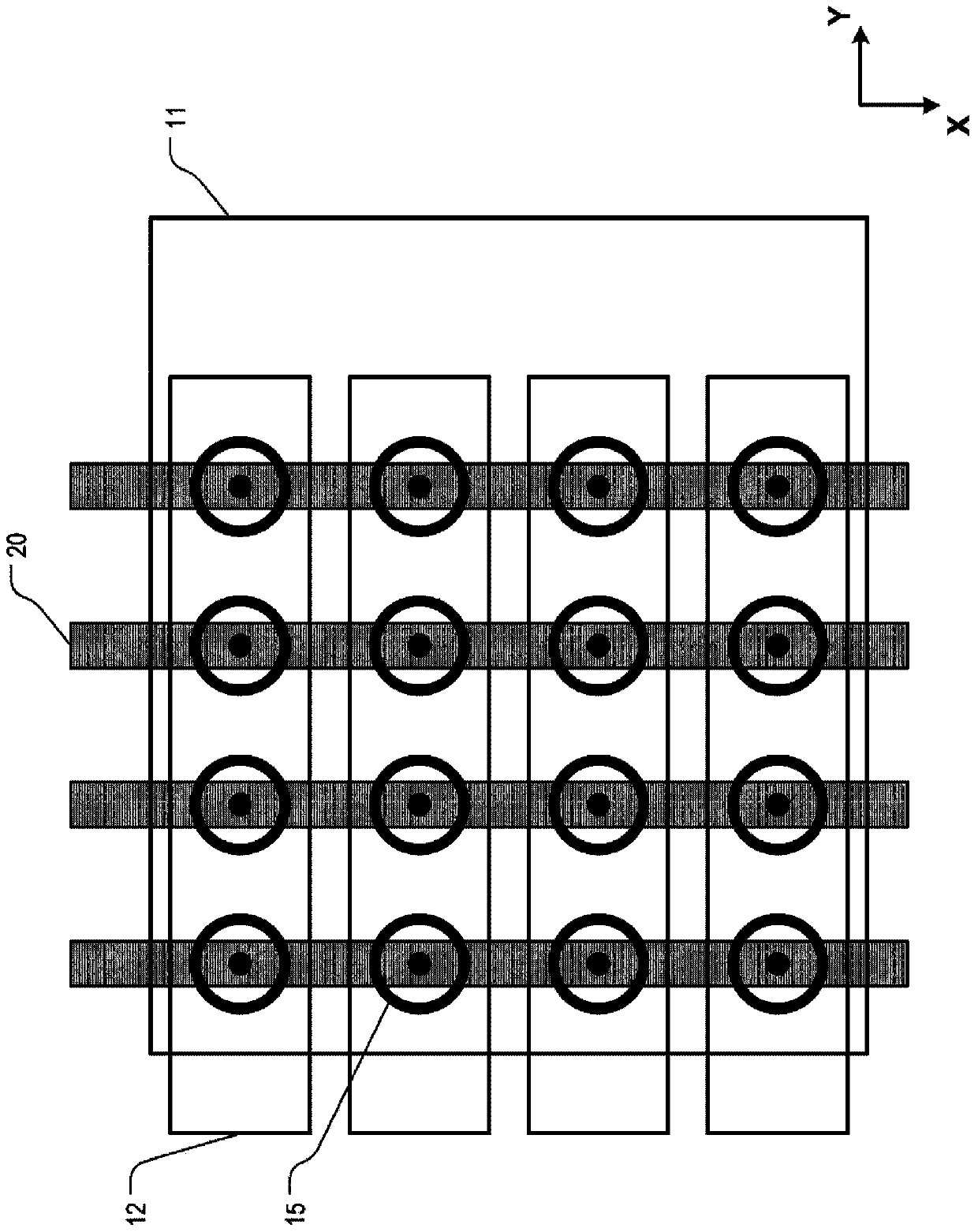

[0051] Figure 5 is instantiated at such as figure 2 with Figure 4 Top view of the columnar array in the depicted conventional 3D structure. Figure 5 Each dot (dot) in represents the lateral position of the corresponding columnar body 515 . As used herein, the "lateral" spatial dimension refers to the structural s...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com