Memory test system and test method thereof

A memory test and memory cell technology, applied in static memory, instruments, etc., can solve the problems of large displacement error range, memory test failure, shortening the valid period of the data window, etc., and achieve the effect of reducing delay time and displacement error.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

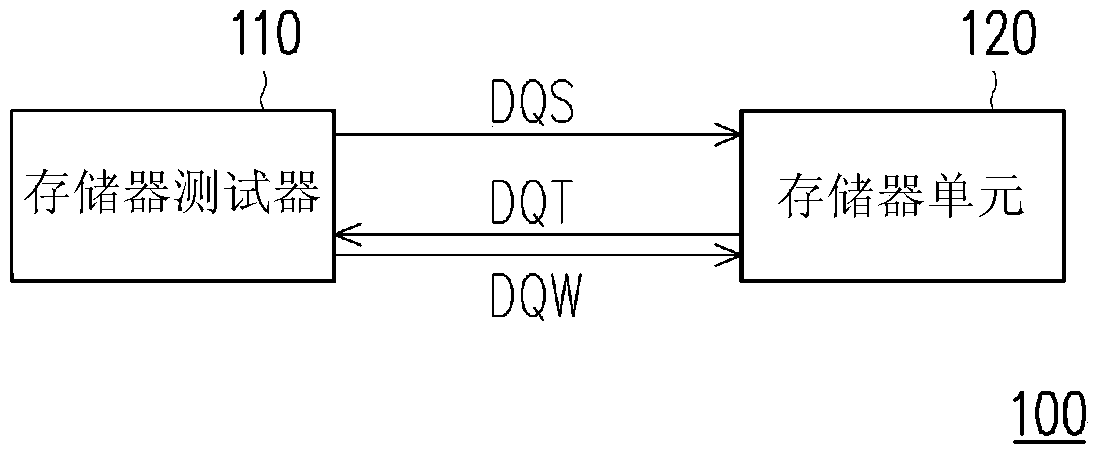

[0041] First please refer to figure 1 , figure 1 It is a schematic diagram of a memory testing system according to an embodiment of the present invention. In this embodiment, the memory testing system 100 includes a memory tester 110 and a memory unit 120 . Wherein the memory unit 120 under test may be, for example, a double data rate (DDR) memory, a second generation double data rate (DDR2) memory, a low power second generation double data rate (LPDDR2) memory or a third generation double Data rate (DDR3) memory and other memory devices.

[0042] exist figure 1 Among them, the memory tester 110 may generate the data strobe signal DQS during testing. Also, the memory tester 110 may transmit the data strobe signal DQS to the memory unit 120 . In detail, the memory tester 110 outputs the write data signal DQW with the test data DT to the memory unit 120 in advance. Moreover, the memory cell under test in the memory unit 120 can store test data DT (logic 0 or 1) according t...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More