Operating method for decreasing read delay of solid-state disk

A method of operation, solid-state storage technology, applied in the input/output process of data processing, instruments, input/output to record carriers, etc., can solve the problem of long response delay of read operation data

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

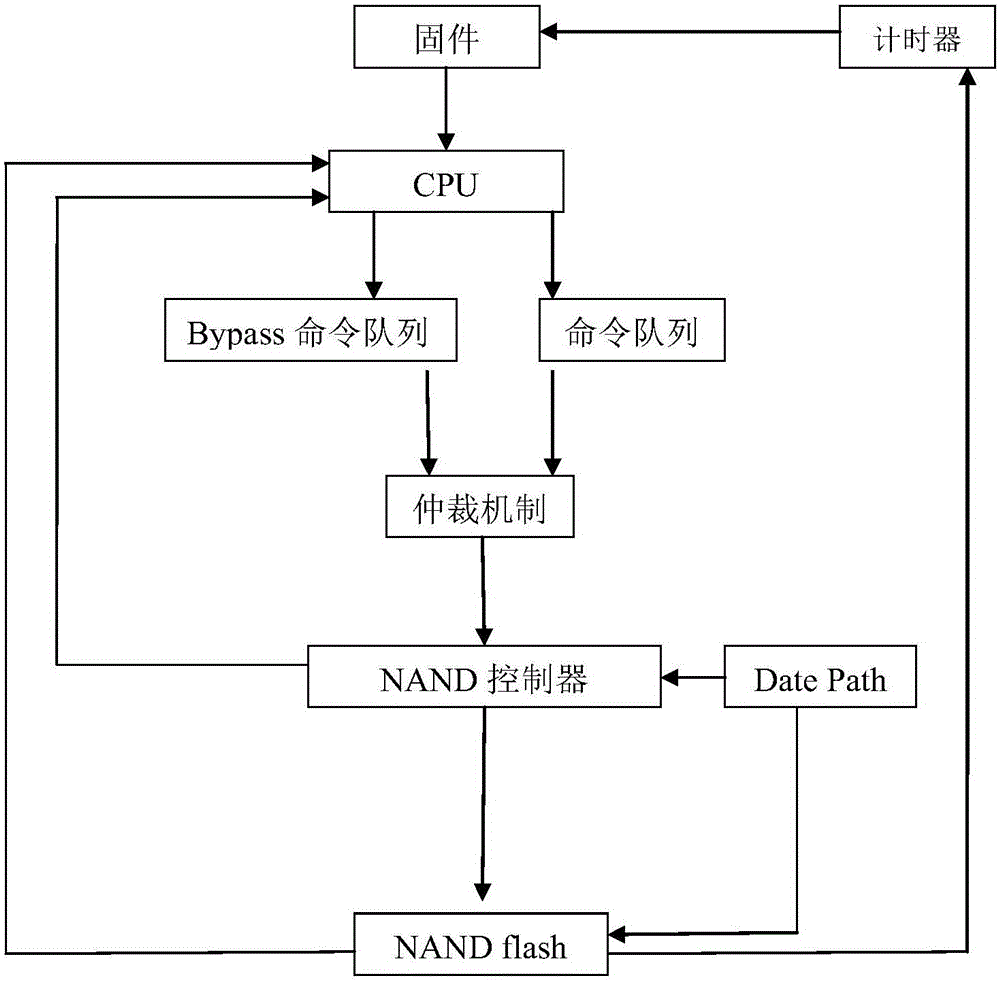

Embodiment 1

[0016] Embodiment 1: When the page write operation or the page erase operation is just completed, the firmware sends the read command to the NAND controller through the Bypass command queue, and the NAND controller preferentially executes the read command in the Bypass command queue through an arbitration mechanism, thereby speeding up the read The execution of the operation.

[0017] In Embodiment 2 and Embodiment 3, the firmware judges the execution time of the page write or page erase operation through the timer, and according to the different preset nodes of the execution status, when the execution status does not exceed the preset node, the page is suspended or cancelled. The execution of the write operation or the page erase operation waits for the execution of the page write operation or the page erase operation when the execution state exceeds the preset node. The preset node is half of the page writing or page erasing operation.

Embodiment 2

[0018] Embodiment 2: When the firmware judges by the timer that the page writing or page erasing operation does not exceed the preset node, the firmware records the current page writing operation or page erasing operation, and sends a pause write to the NAND controller through the Bypass command queue Instructions for page write operation or page erase operation, and then the firmware sends the read operation to the NAND controller through the Bypass command queue to execute the read operation that needs to be accelerated. After the execution is completed, the firmware sends the instruction through the Bypass command queue to restore The page write operation or page erase operation is being executed; for NAND media that do not support the suspension of page write operation or page erase operation, the NAND media sends to cancel the page write operation or page erase operation, and resends the previously canceled one through the Bypass command queue Write operation or erase oper...

Embodiment 3

[0019] Embodiment 3: When the firmware judges by the timer that the page write operation or the page erase operation exceeds the preset node, it is not enough to interrupt the operation through the Bypass command queue, and the firmware waits for the page write operation or the page erase operation to be executed. , and then send the read operation through the Bypass command queue or the regular command queue.

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More