Substrate etching method

A substrate and main etching technology, which is applied in the manufacturing of electrical components, circuits, semiconductor/solid-state devices, etc. The bottom width and height are satisfied, and the effect of increasing the bottom width of the graphic

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

specific Embodiment

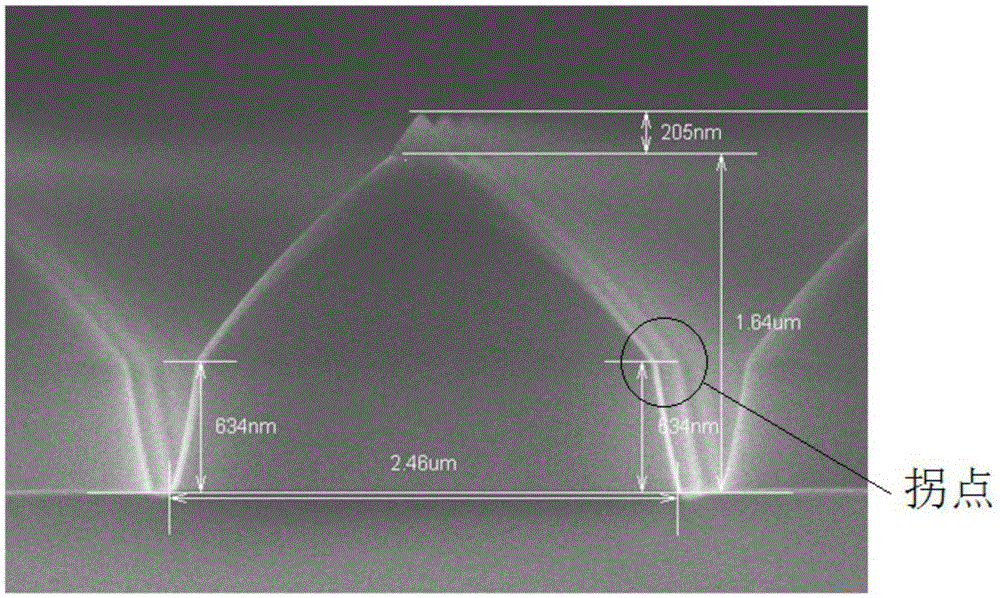

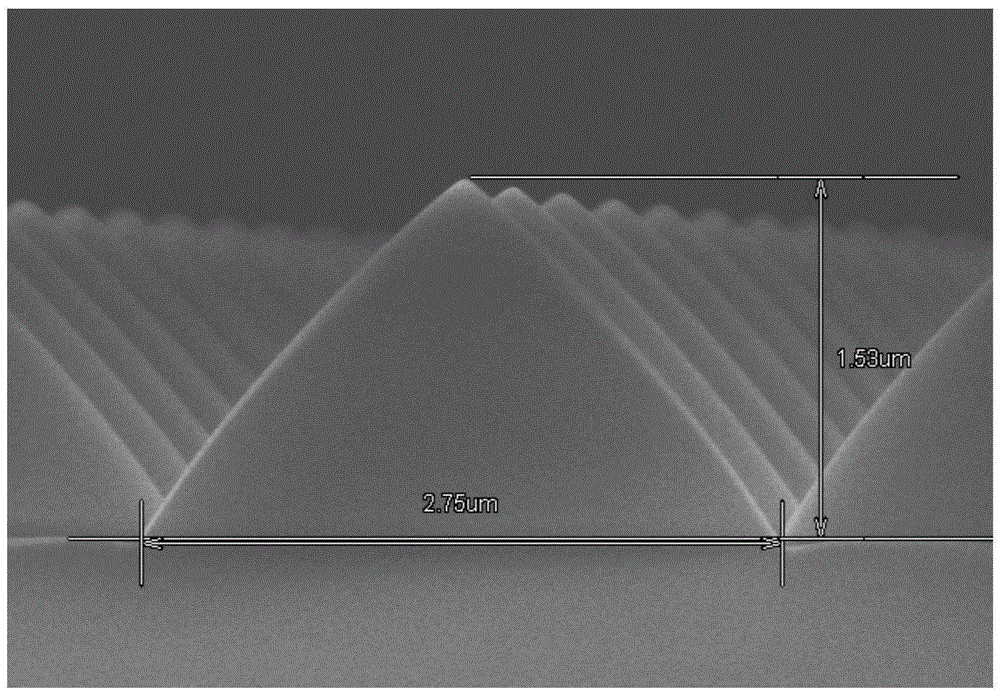

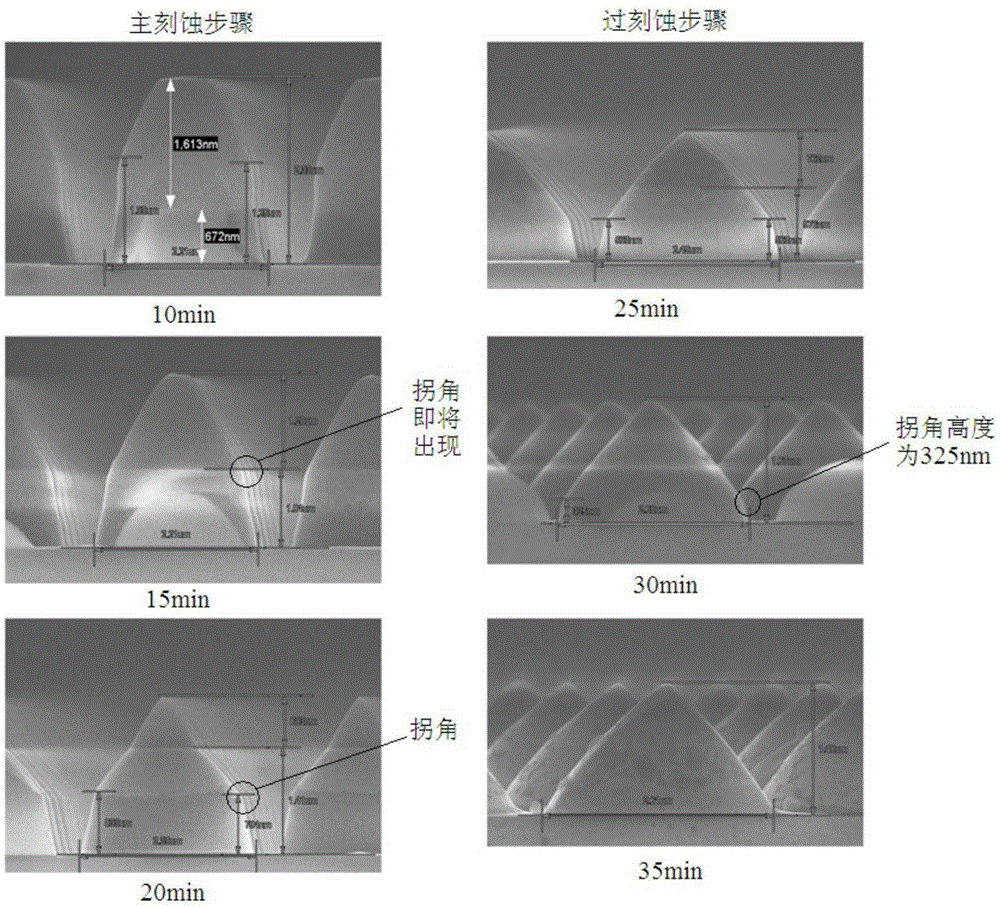

[0046] The following is a specific embodiment of the substrate etching method provided by the present invention, the substrate etching method specifically includes the following steps:

[0047] Main etching step, which further comprises step ME1 and step ME2, wherein,

[0048] The process parameters of step ME1 are: the chamber pressure of the reaction chamber is 2.5mT; the power of the upper electrode is 1400W; the power of the lower electrode is 350W; the flow rate of the etching gas is 80sccm; the process time is 18min;

[0049] The process parameters of step ME2 are: the chamber pressure of the reaction chamber is 2.5mT; the power of the upper electrode is 1400W; the power of the lower electrode is 350W; the etching gas is 80sccm; the process time is 7min;

[0050] Overetching step, which further includes step OE1 and step OE2, wherein,

[0051] The process parameters of step OE1 are: the chamber pressure of the reaction chamber is 2.2mT; the power of the upper electrode ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More