Non-volatile memory with restricted dimensions

A memory, memory word technology, applied in the field of memory, can solve the problem that the separation voltage solution is not suitable, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

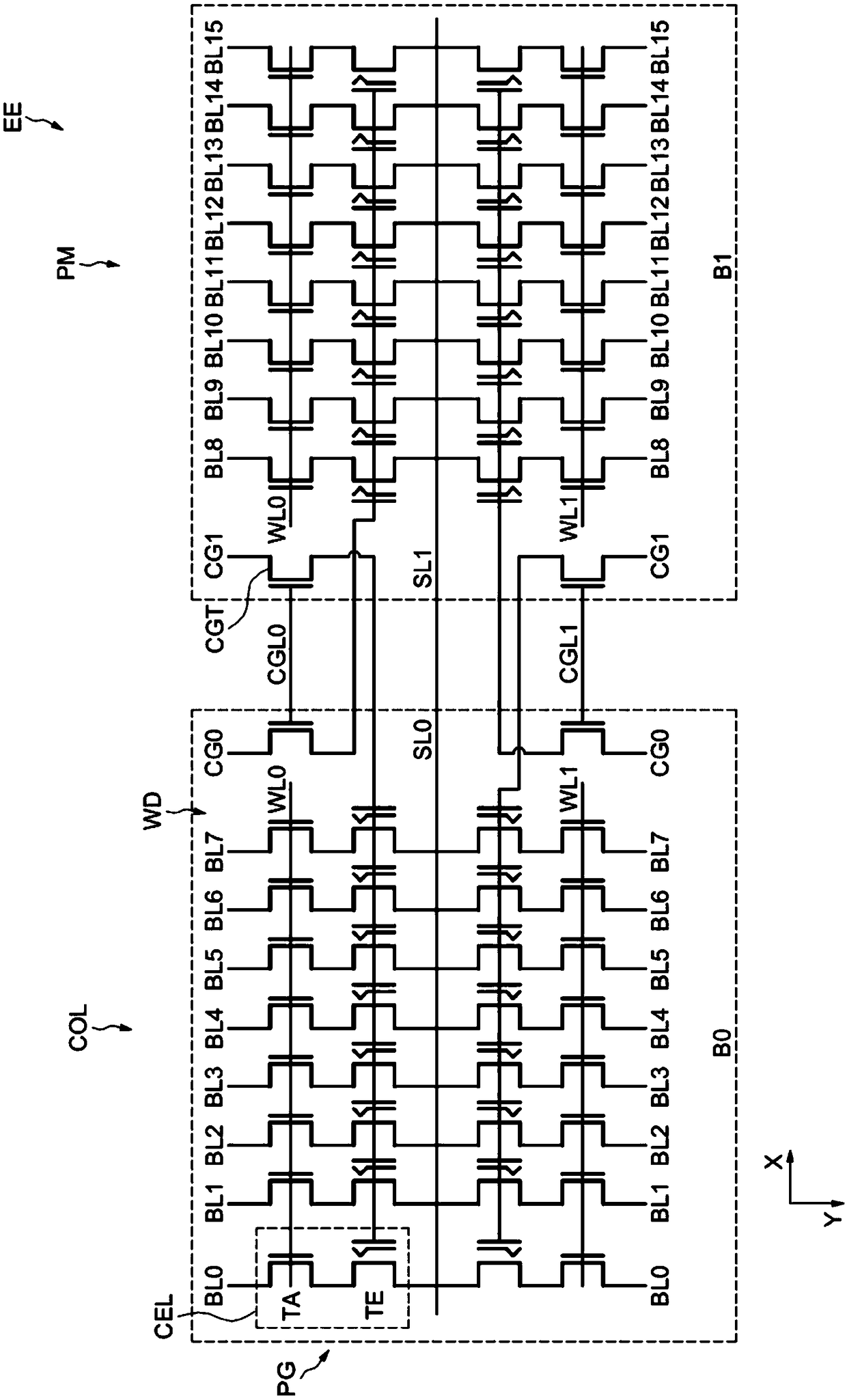

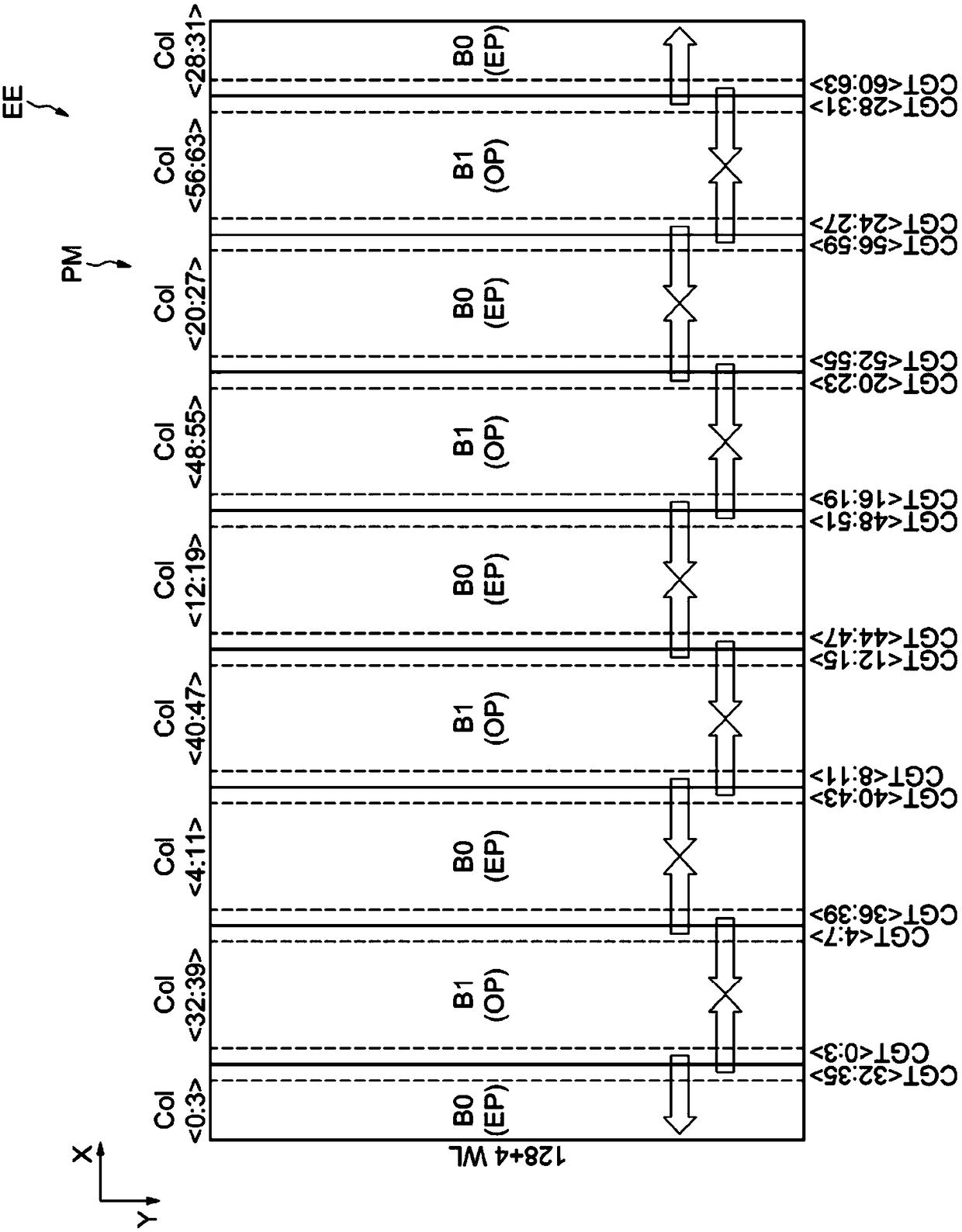

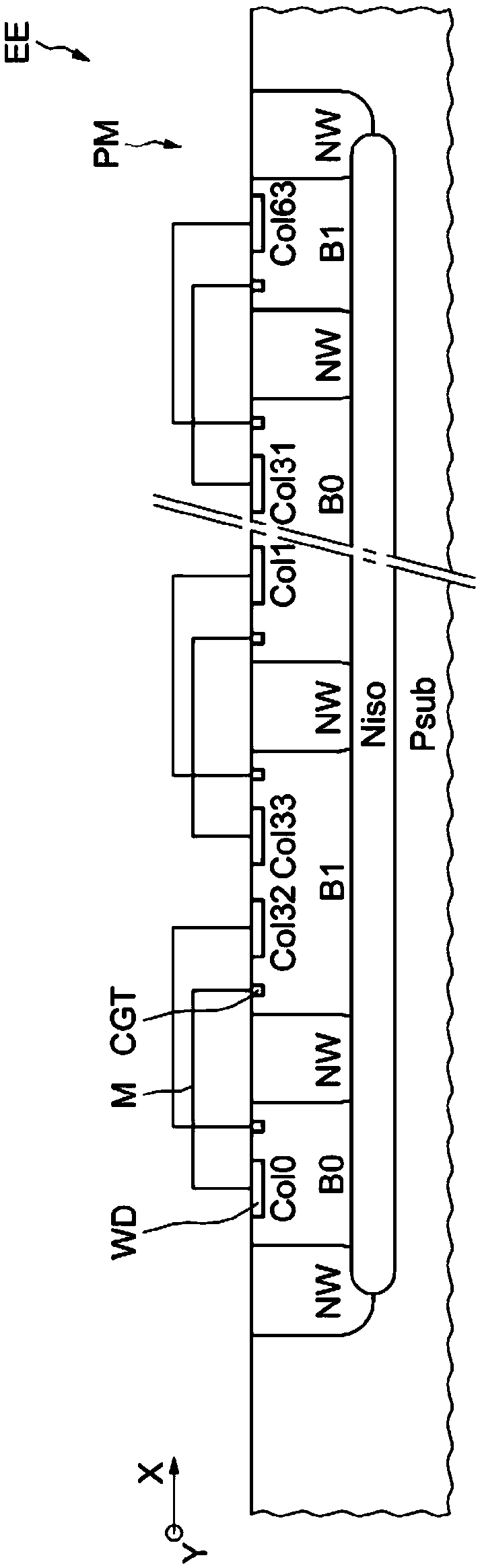

[0029] A solution is proposed that makes it possible to address the voltage limitations of the components while reducing the surface area consumed both in the memory plane and at the periphery.

[0030] In this respect it is therefore proposed a memory device of the electrically erasable programmable non-volatile memory type comprising a memory plane comprising a series of adjacent semiconductor grooves of a first conductivity type electrically insulated from each other, each each memory cell includes a state transistor having a floating gate and a control gate, each control gate The select transistors are coupled to the control gates of the state transistors of the memory word to which it is assigned, each control gate select transistor being located in and on an adjacent semiconductor recess housing the semiconductor recess of the memory word to which it is assigned.

[0031] Thus, it is possible to increase the potential of the groove comprising the control gate selection t...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to view more

Login to view more - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap