SMV model construction method for register transfer level verilog code

A technology of register transfer level and construction method, which is applied in the field of SMV model construction of register transfer level Verilog code, can solve problems such as poor independence, and achieve good practical effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

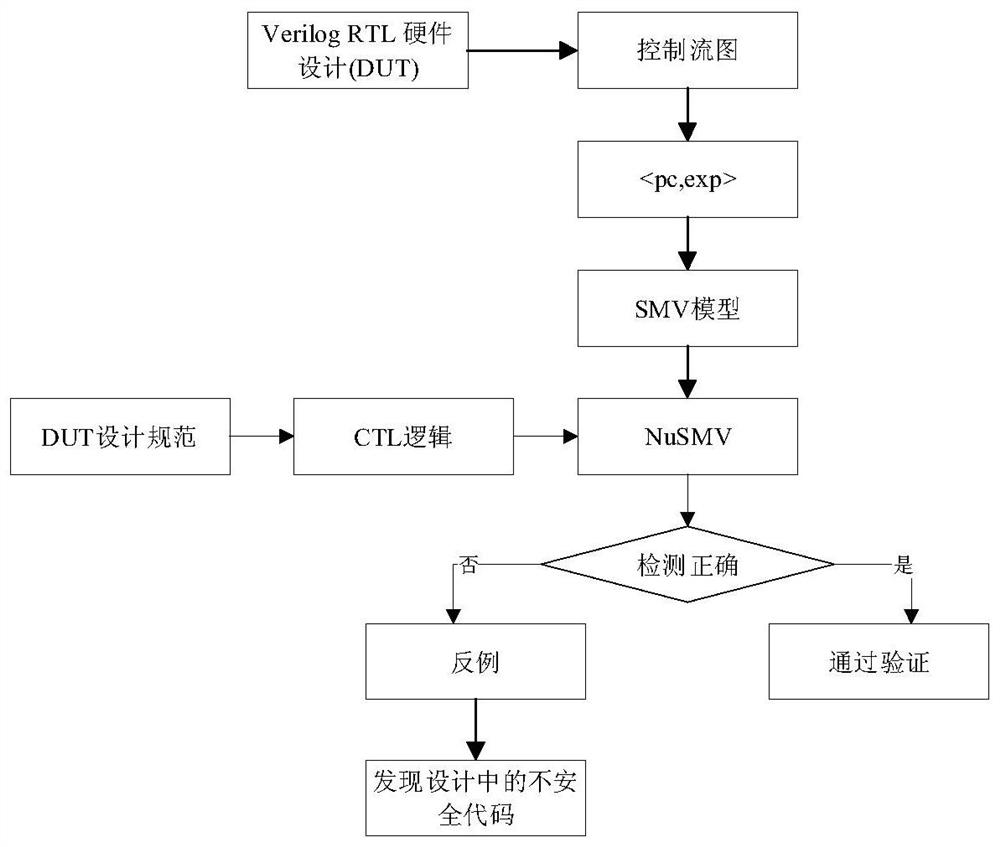

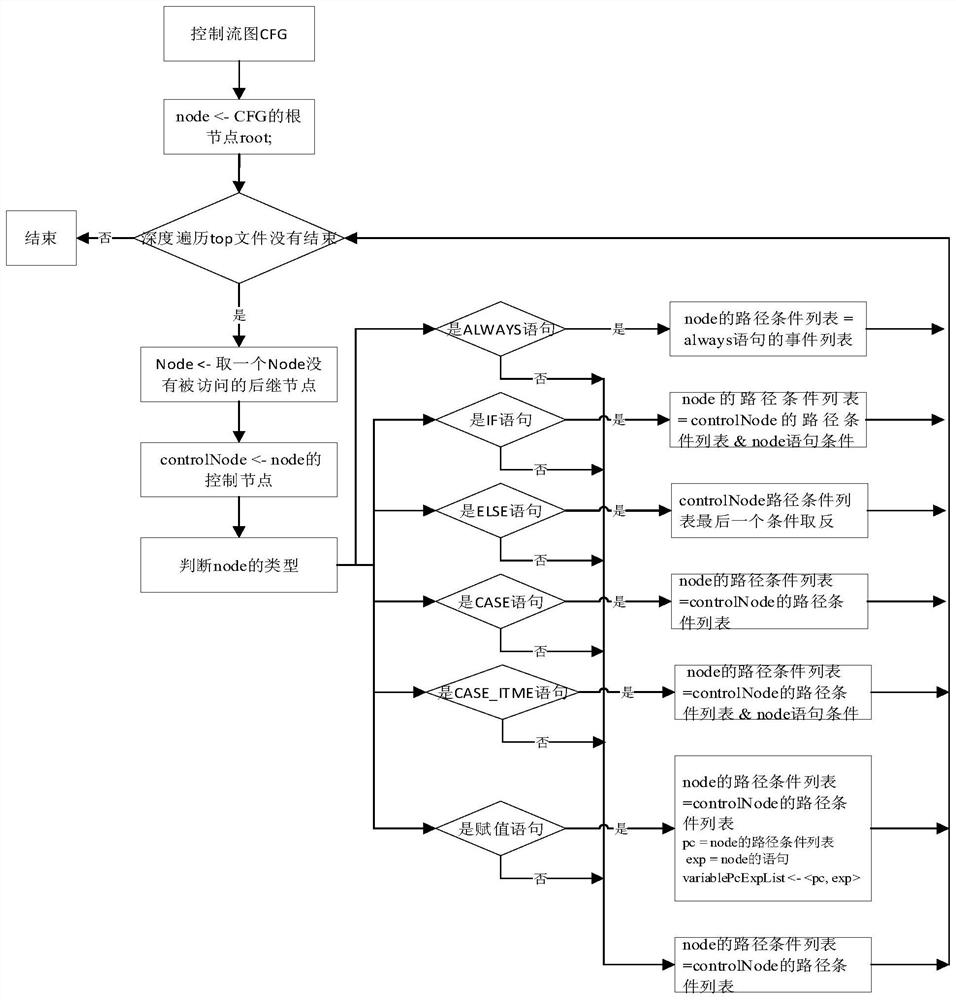

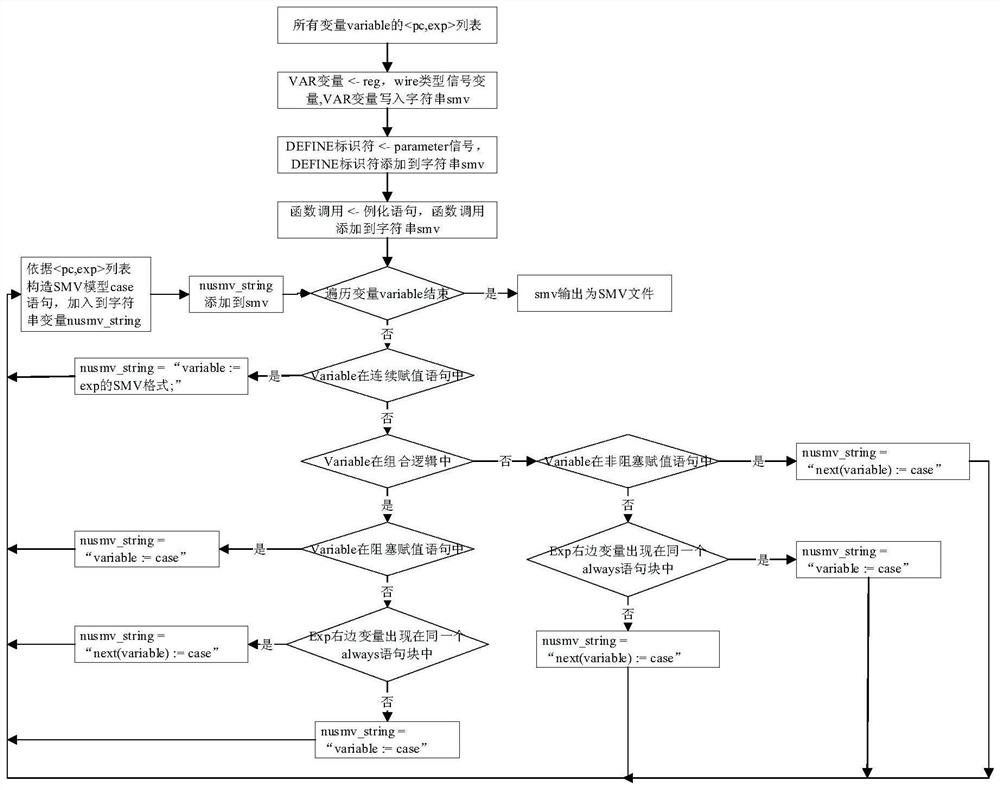

[0020] refer to Figure 1-4 . The concrete steps of the SMV model construction method of the register transmission level Verilog code of the present invention are as follows:

[0021] Select RS232-T600 on Trust-Hub as the analysis object, which contains three Verilog files: uart.v, u_xmit.v and u_rec.v. The three Verilog files are shown below. There are hardware Trojans in the file u_xmit.v. The hardware Trojan is a finite state machine, which detects the sending data sequence, when the sequence 8'hAA, 8'h55, 8'h00 and 8'hFF appears, the Trojan is activated, the output variable xmit_doneH is set to "1", and The 7th bit of the transmitted data is replaced.

[0022] 1.uart.v program source code:

[0023]

[0024]

[0025] 2.u_xmit.v program source code:

[0026]

[0027]

[0028]

[0029]

[0030] 3.u_rec.v program source code:

[0031]

[0032]

[0033]

[0034] Step 1, generation of variable list.

[0035] Take lines 60-67 of u_xmit.v as an ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More