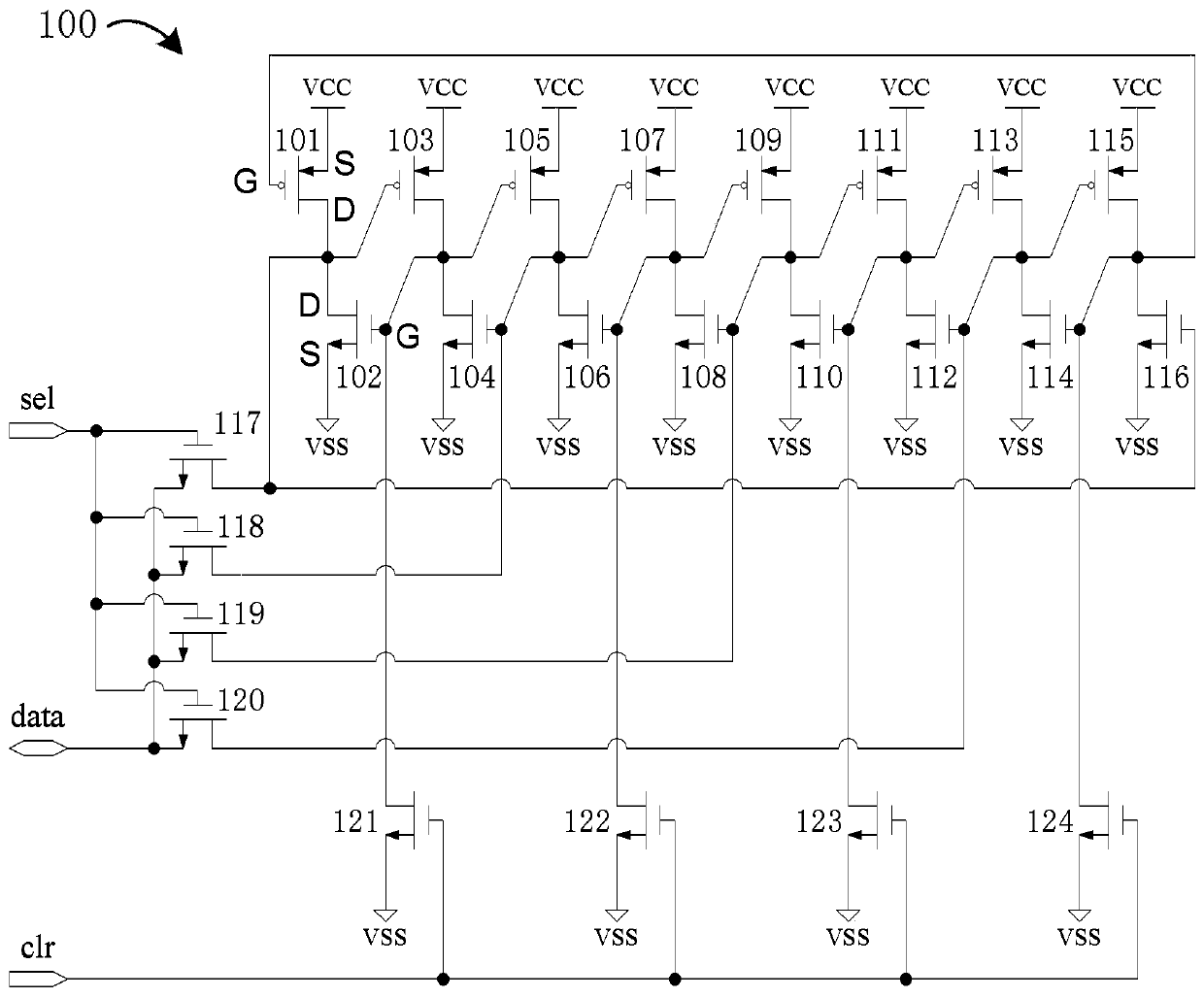

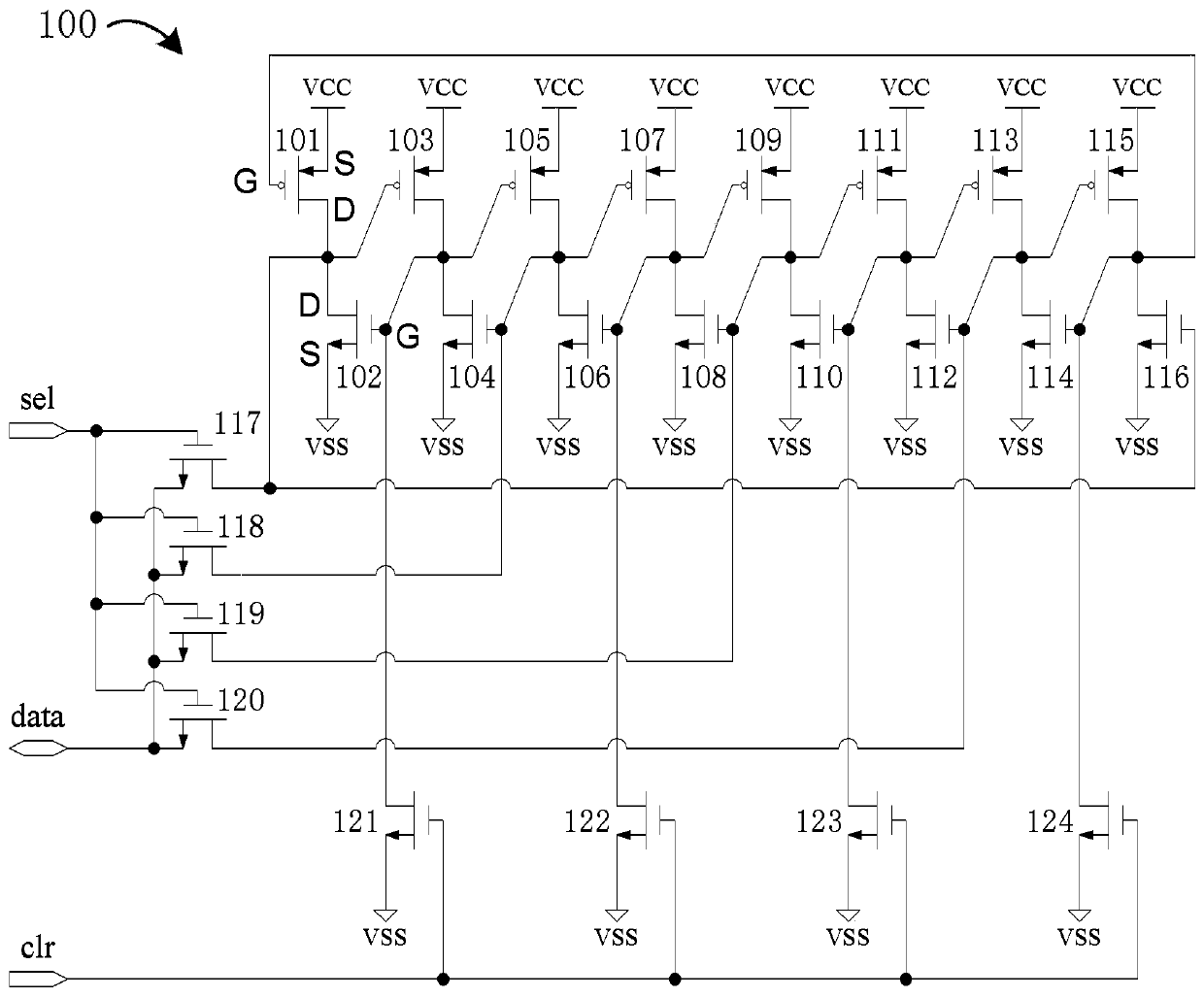

N-mode redundancy configuration storage unit circuit for FPGA

A technology for configuring storage and unit circuits, applied in static memory, instruments, etc., can solve problems such as wiring, complex structure, and cumbersome components, and achieve the effect of simplifying wiring and structure, and improving the anti-single-event flip threshold.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0028] The read-write storage unit at both ends of the prior art has the defects of wiring, complex structure, and cumbersome components. In view of this, the present invention provides an N-mode redundant configuration storage unit circuit for FPGA, which is different from that in the prior art. Both '0' and '1' need to be read and written. The N-mode redundant configuration storage unit circuit used in the present invention is cleared to zero once when the circuit is powered on, and then the configuration unit that needs to write '1' and then write '1' during configuration; When reading back the configuration data, it also defaults to '1', and only reads back '0'. It only needs to use as few MOS transistors as possible to implement the configuration requirements in the FPGA, which can improve the anti-single event turnover threshold of programmable logic devices.

[0029] In order to make the object, technical solution and advantages of the present invention clearer, the pres...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More