Dual-mode redundant configuration storage unit circuit for programmable logic devices

A storage unit and configuration storage technology, applied in information storage, static memory, digital memory information, etc., to achieve the effect of improving the anti-single event turnover threshold

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0017] In order to make the object, technical solution and advantages of the present invention clearer, the present invention will be described in further detail below in conjunction with specific embodiments and with reference to the accompanying drawings.

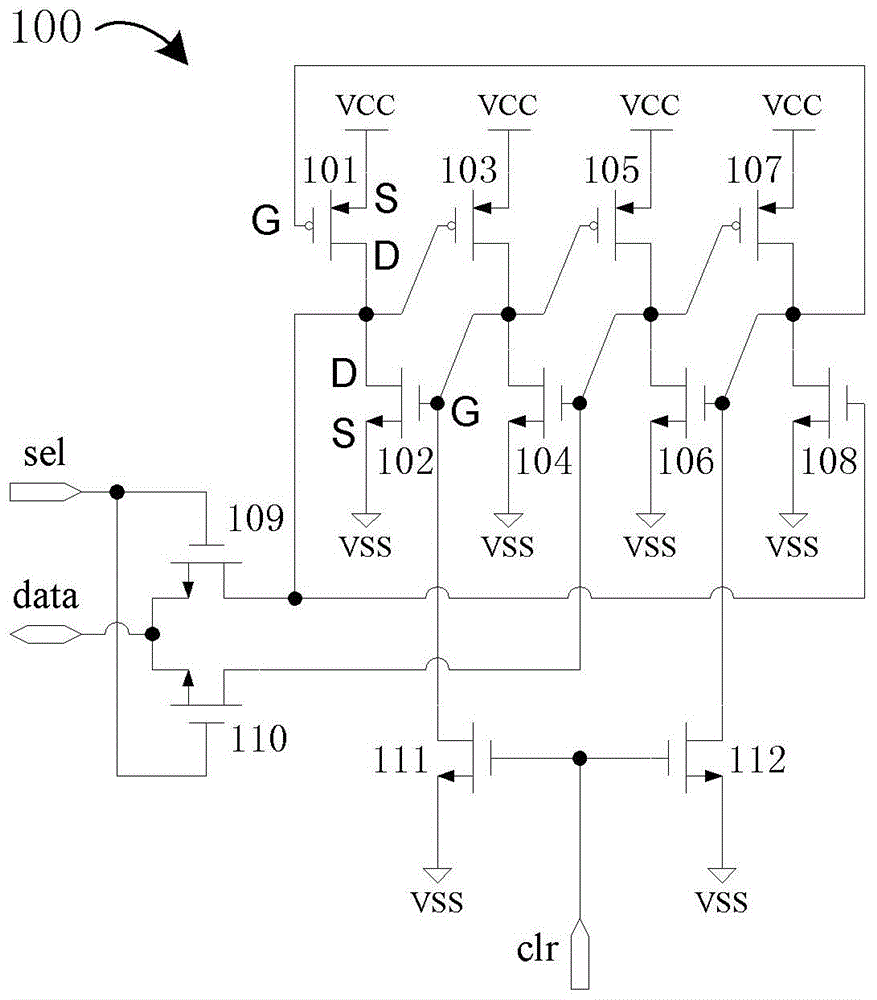

[0018] figure 1 It is a schematic diagram of a dual-mode redundant configuration storage unit circuit according to an embodiment of the present invention, such as figure 1 As shown, the dual-mode redundant configuration storage unit circuit 100 for programmable logic devices includes: 4 levels of 4 PMOS transistors 101, 103, 105, 107 and 4 NMOS transistors 102, 104, 106, 108 Interlocking storage unit, 2 transmission tubes 109 and 110, and 2 zeroing tubes 111 and 112, wherein:

[0019] The first PMOS transistor 101 and the first NMOS transistor 102 form a first-level interlock storage unit, the second PMOS transistor 103 and the second NMOS transistor 104 form a second-level interlock storage unit, and the third PMOS tran...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More