Signal jitter estimation method for the output of lpddr4 IO interface

A technology of LPDDR4IO and output terminal, applied in the direction of calculation, design optimization/simulation, CAD numerical modeling, etc., to achieve the effect of high accuracy and rich frequency domain details

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

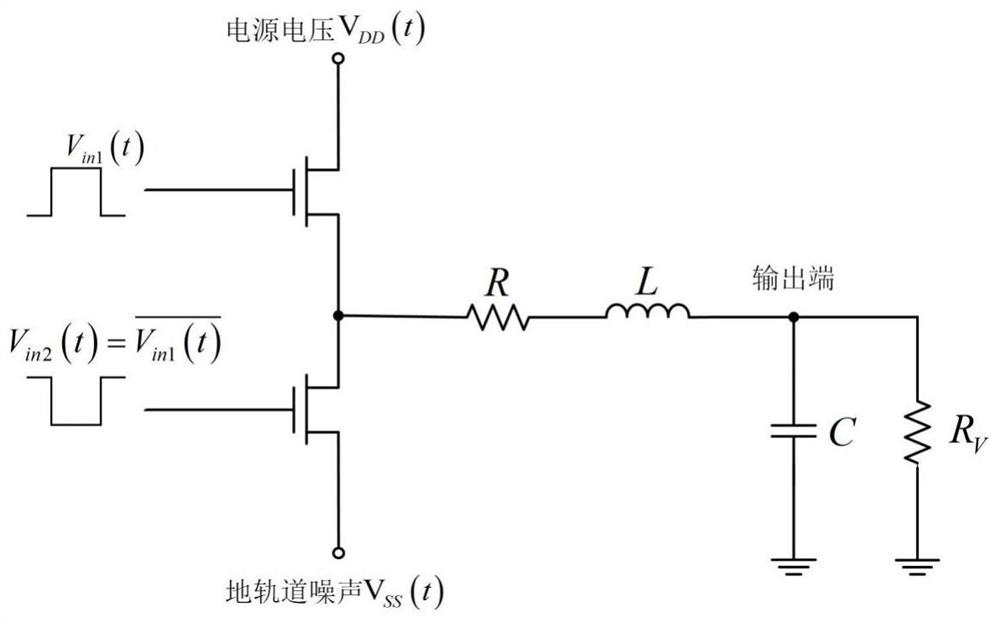

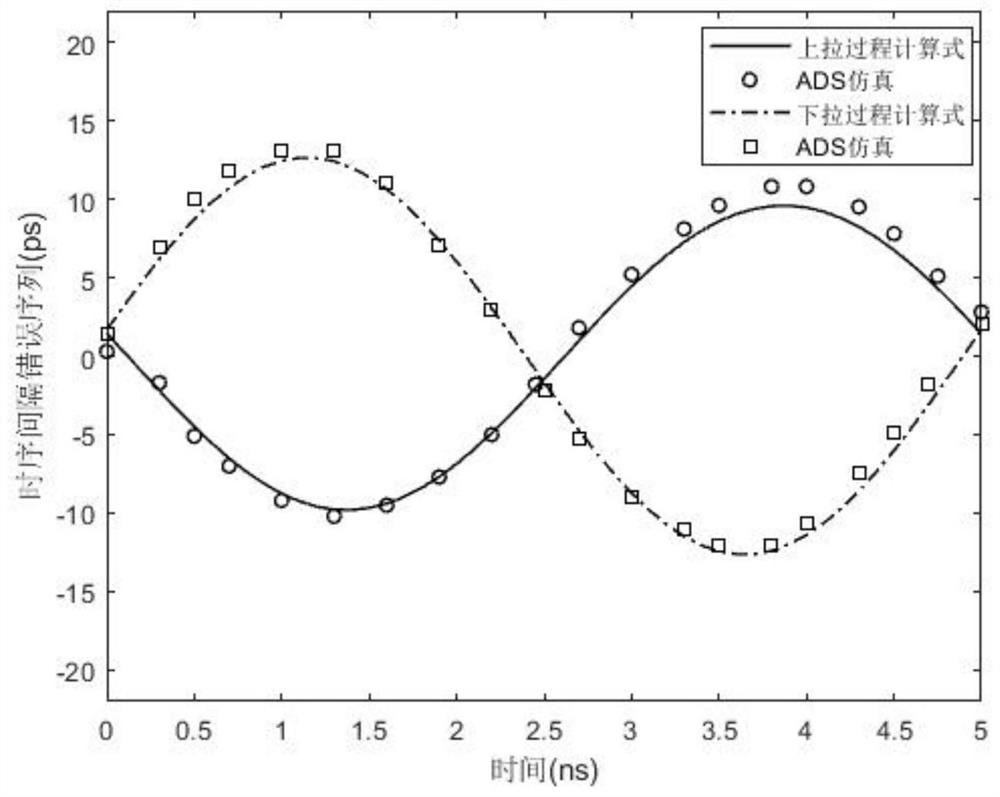

[0055] The present invention will be further described below in conjunction with the accompanying drawings.

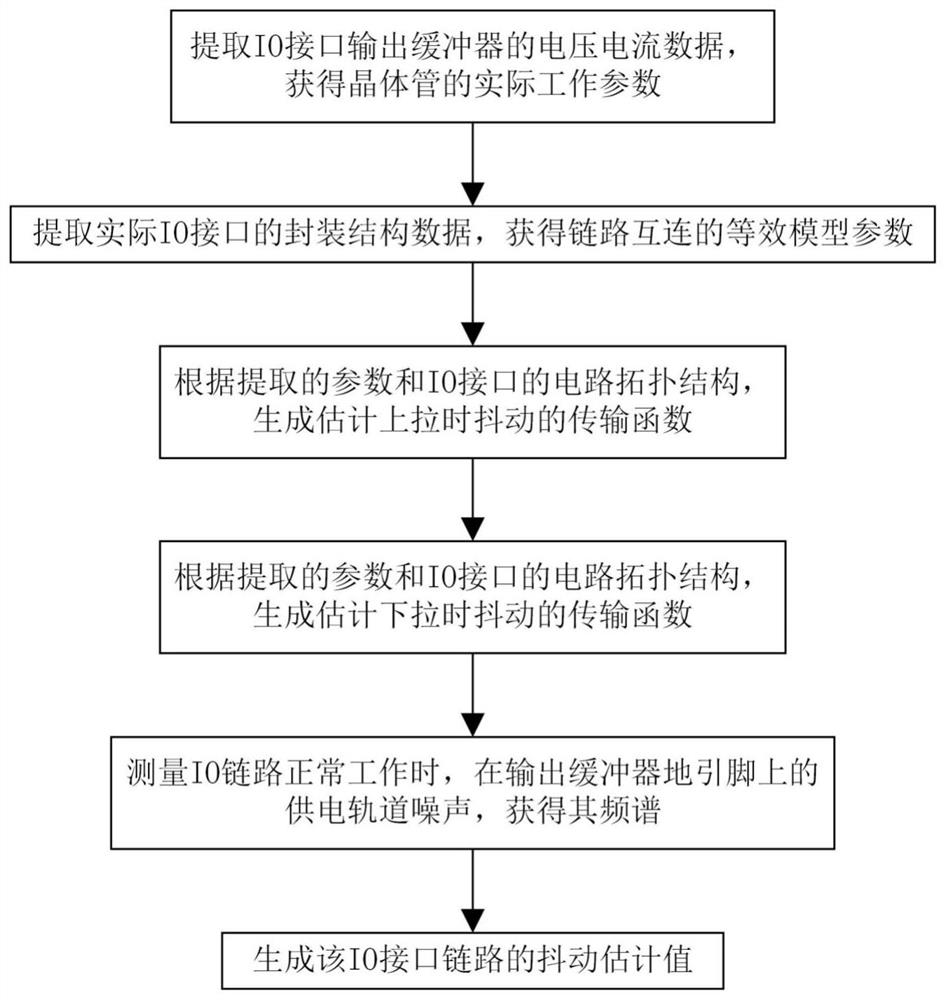

[0056] Refer to attached figure 1 , to further describe the specific steps of the present invention.

[0057] Step 1, obtaining the actual working parameters of the MOS tube.

[0058] The first step is to extract the working data of the output device used in the actual LPDDR4 IO interface link, and draw the current and voltage working curves of the pull-up NMOS and the pull-down NMOS.

[0059] The second step is to obtain the DC operating point voltage V of the pull-up NMOS transistor according to the current-voltage curve of the pull-up NMOS. 0 , DC transconductance g dc and small signal AC transconductance g m .

[0060] Specific steps are as follows:

[0061] In the first step, the center point of the maximum and minimum values of the gate-source voltage when the pull-up NMOS is working is taken as the DC operating point voltage V 0 .

[0062] Step 2, find...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More