Network-on-chip design method and device based on hybrid routing algorithm

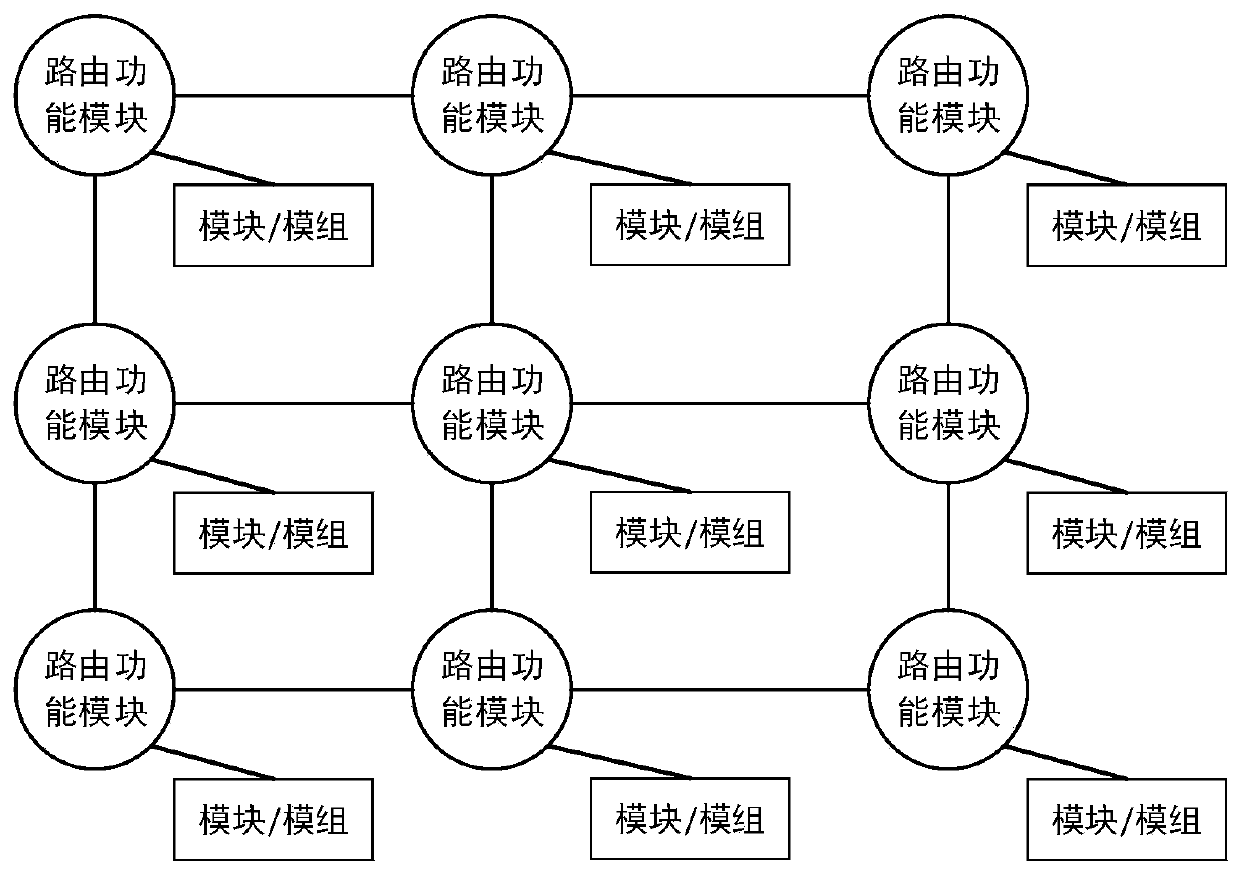

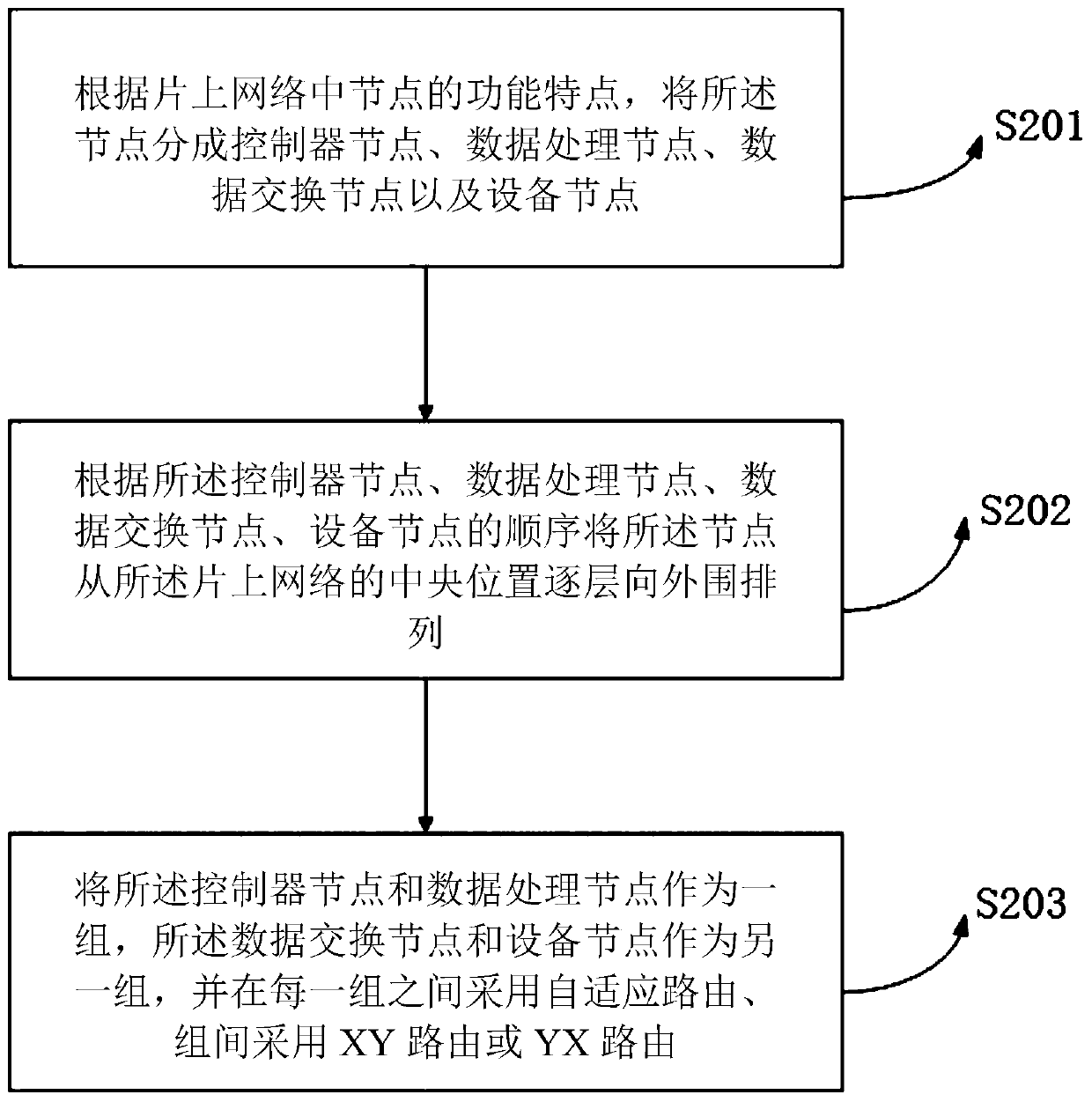

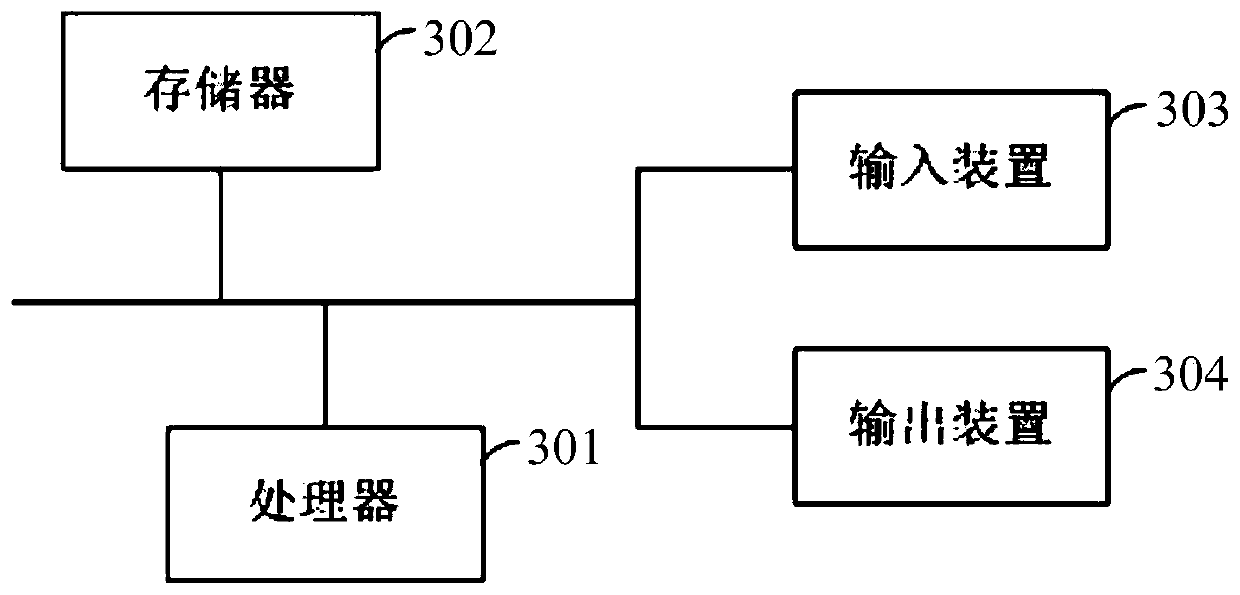

An on-chip network and hybrid routing technology, applied in the computer field, can solve the problem of not being able to improve efficiency, and achieve the effects of improving efficiency, reducing data congestion, and improving performance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0036]Embodiments of the present invention are described below. It is to be understood, however, that the disclosed embodiments are merely examples and that other embodiments may take various alternative forms. The figures are not necessarily to scale; some features may be exaggerated or minimized to show details of particular components. Therefore, specific structural and functional details disclosed herein are not to be interpreted as limiting, but merely as a representative basis for teaching one skilled in the art to variously employ the present invention. As will be understood by persons of ordinary skill in the art, various features shown and described with reference to any one figure can be combined with features shown in one or more other figures to create embodiments not explicitly shown or described . Combinations of features shown provide representative embodiments for typical applications. However, various combinations and modifications of the features consisten...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More