Three-dimensional chip based on system bus and three-dimensional method thereof

A system bus and three-dimensional chip technology, which is applied in the direction of electrical components, electric solid devices, circuits, etc., can solve the problem that logic chips cannot be processed in three-dimensional way

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0030] In order to make the above-mentioned features and effects of the present invention more clear and understandable, the following specific examples are given together with the accompanying drawings for detailed description as follows.

[0031] In a preferred embodiment of the present invention, a vertical stacking method of multi-layer homogeneous logic chips is proposed. These include: how to implement information communication on-chip or off-chip in the design of two or more isomorphic logic chips to complete the 3D of the chip.

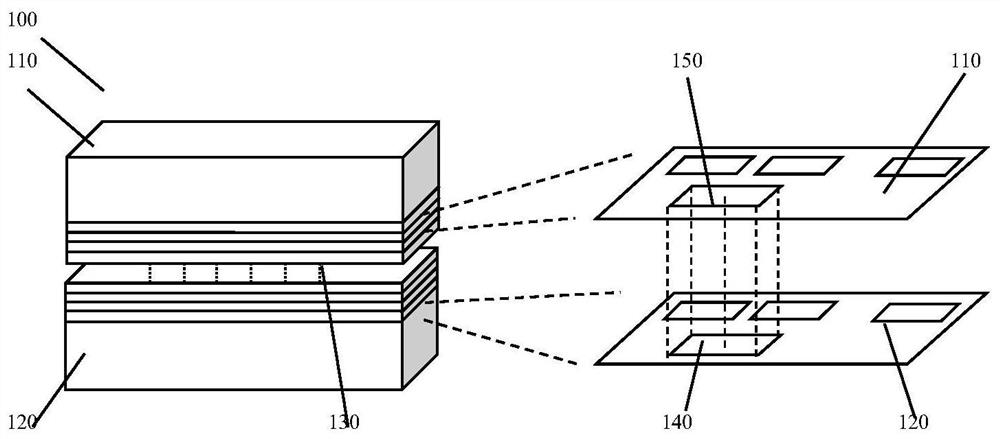

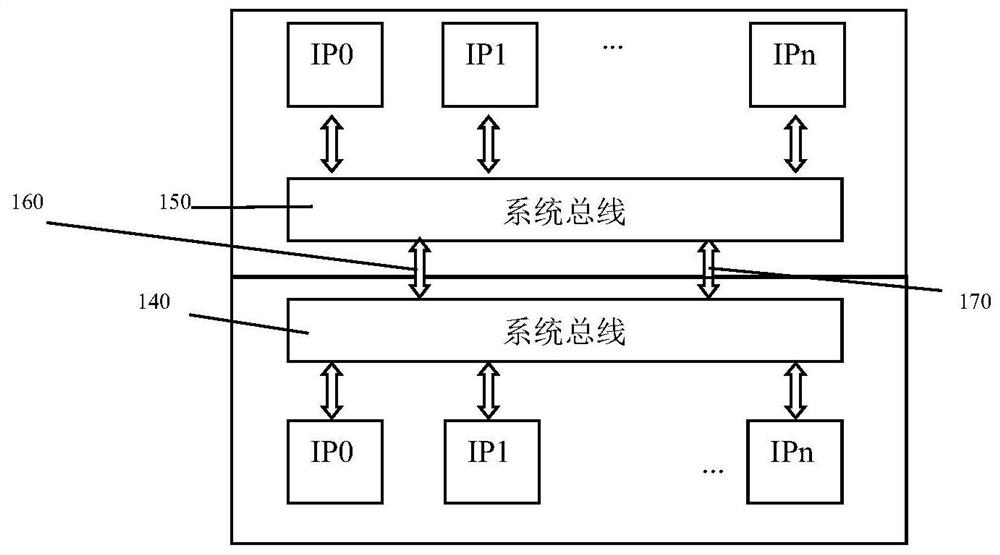

[0032] Such as Figure 1a and Figure 1b As shown, the 3D chip (100) is stacked by two isomorphic logic chips (110 and 120) in a direct bonding (130) manner (for example: DBI) through the top and top of the chip. The individual modules in the chip overlap completely. The system buses (140 and 150) in each chip are directly bonded to realize information exchange between chips, and the 3D design of the chip is completed.

[0033] Two channels...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More