Storage circuit with odd-even check unit array

一种单元阵列、奇偶校验的技术,应用在半导体存储器领域,能够解决无法测试、测试图形无法直接提供数据总线等问题,达到缩短测试时间的效果

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 1 example

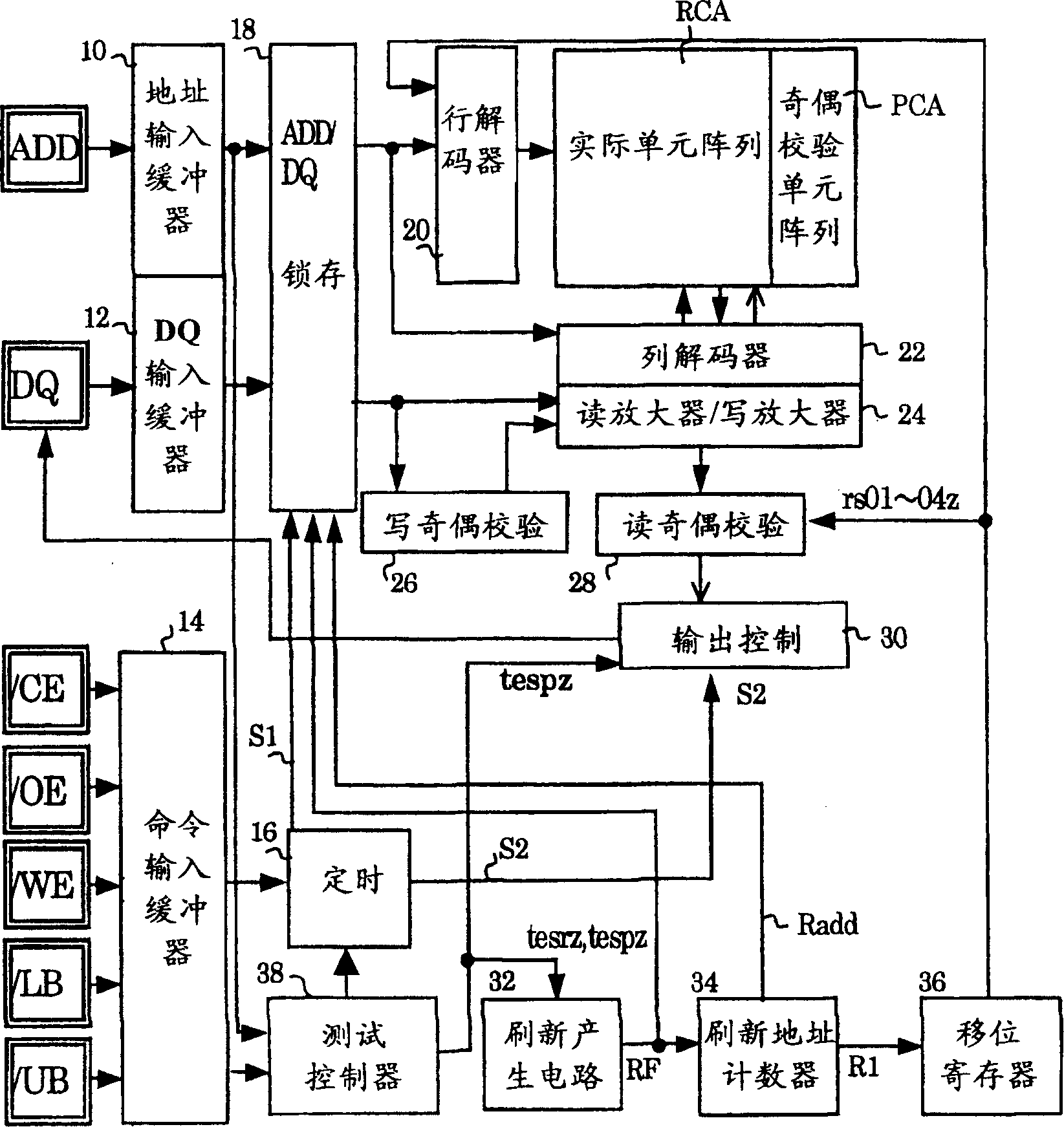

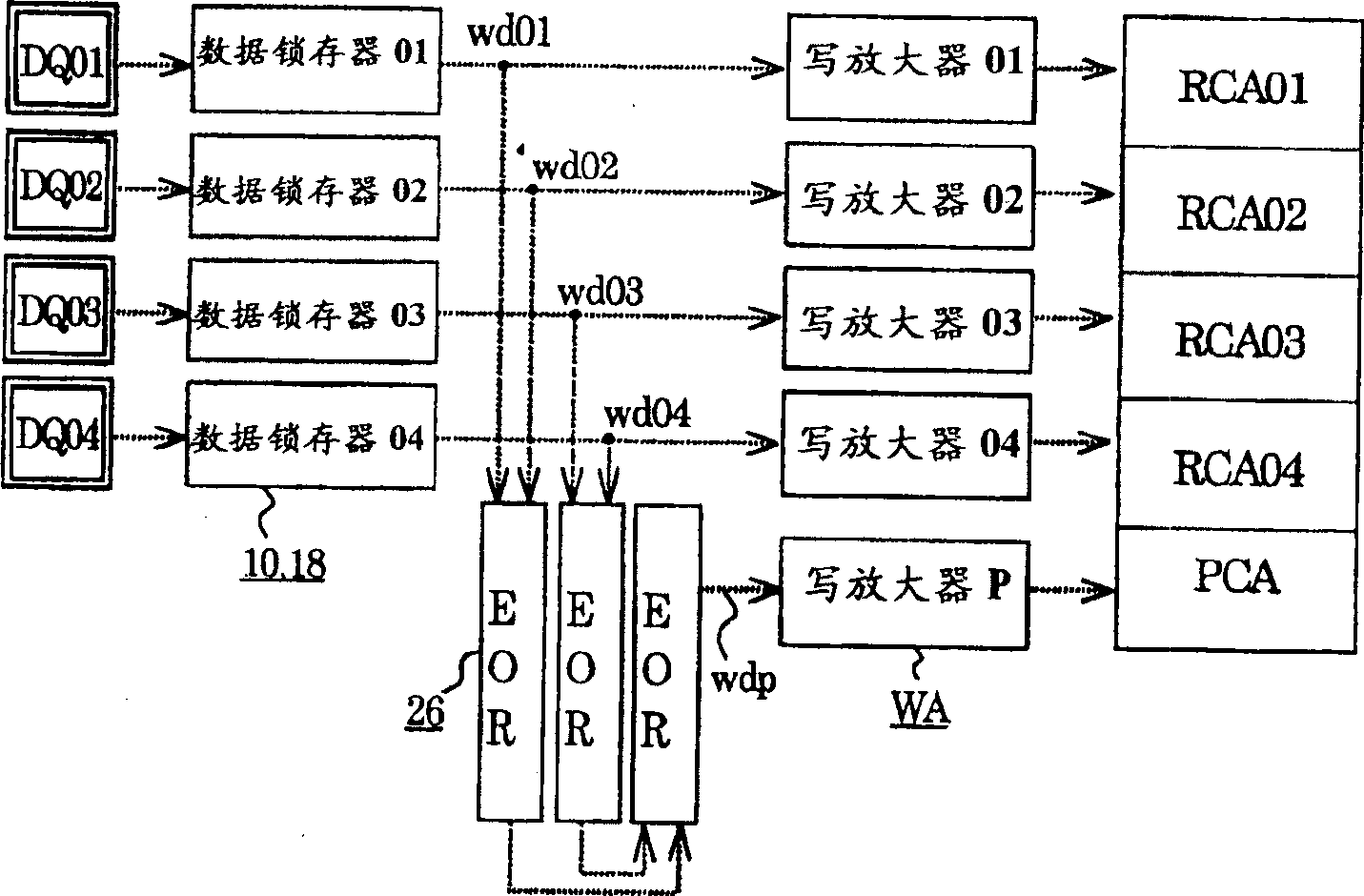

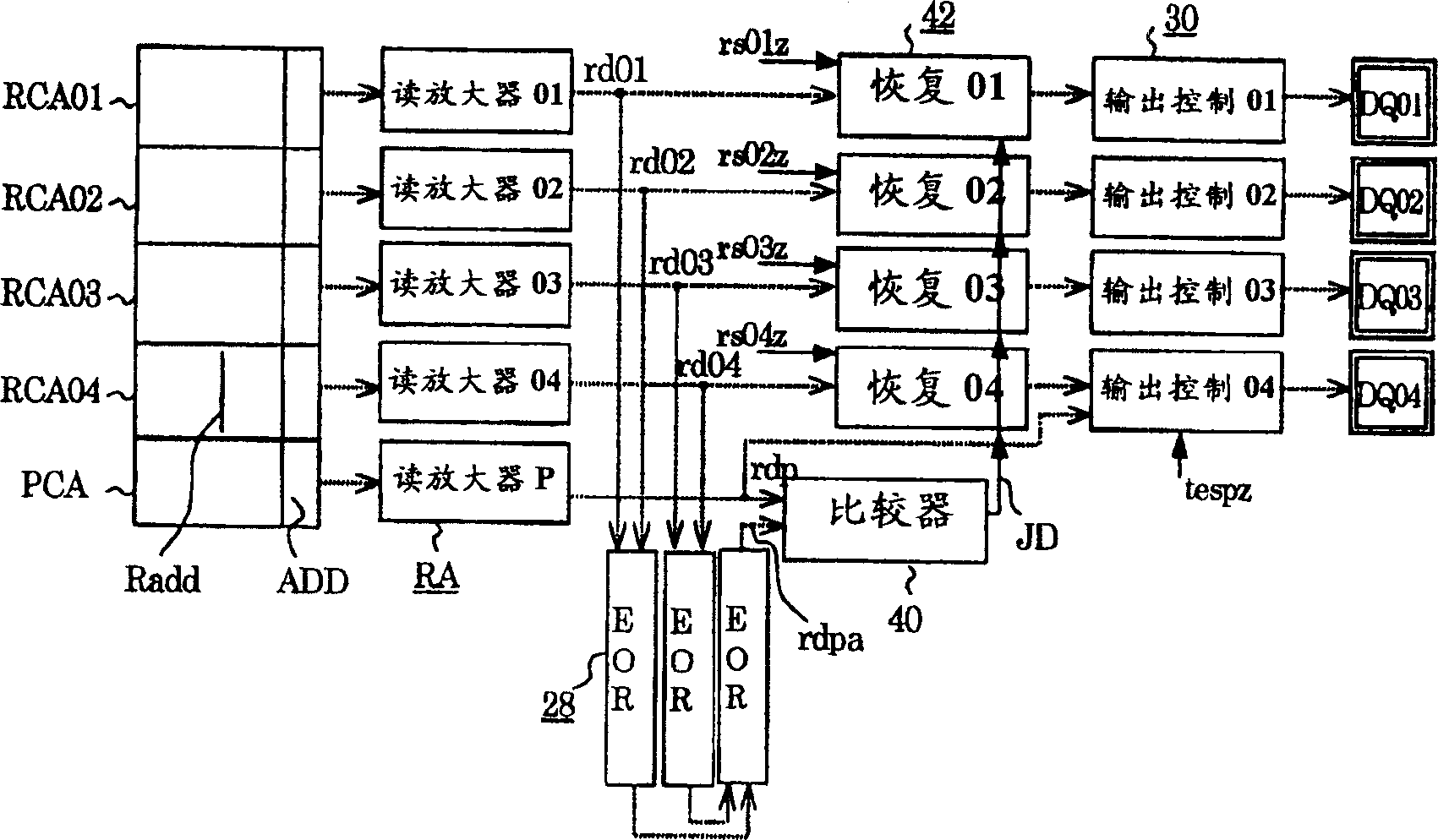

[0063] figure 1 The overall configuration of the memory circuit of the first embodiment is explained. This memory circuit has a general real cell array RCA for storing data, and has a parity cell array PCA for storing parity bits of data written in the real cell array. The cell arrays each include (not shown) a plurality of word lines, a plurality of bit lines, and 1 transistor / 1 capacitor unit located at intersections between these word lines and bit lines.

[0064] The parity bits stored in the parity cell array PCA are codes generated by computing data written into the actual cell array, ie, codes that allow error recovery in data subsequently read from the actual cell array. Therefore, in this sense, the parity cell array may be referred to as an ECC cell array storing an error correction code (ECC). That is, by storing ECC generated by more complicated logic than parity bits, even if there is a partial error in data read out from the actual cell array, the error can be ...

no. 2 example

[0101] Next, a second embodiment will be described. In the figure, signal lines indicated by thick lines are configured in various forms. In addition, some blocks connected by bold lines are composed of multiple circuits. The same reference symbols as the terminal names are used for the signals supplied via the external terminals, and the same reference symbols as the signal names are used for the signal lines that transmit the signals.

[0102] Figure 11 A second embodiment of the semiconductor memory of the present invention will be described. This semiconductor memory is formed as a DRAM on a silicon substrate using a CMOS process. The DRAM has a function of performing memory cell refresh operations without external recognition. Here, the refresh operation is an operation of rewriting data held in memory cells.

[0103] In addition, the specifications of the external terminals of the DRAM and the specifications of the signal input / output timing are made so as to confo...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com