Dynamic frequency conversion device of bus in high speed and kermel interface of processor under SOC architecture

A processor core and processor technology, applied in the direction of electrical digital data processing, instrumentation, signal generation/distribution, etc., can solve the problems of restarting the system, lack of flexibility, etc., and achieve the effect of saving electric energy and rationally utilizing power consumption

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0019] The present invention will be further described in detail below in conjunction with the accompanying drawings and specific embodiments.

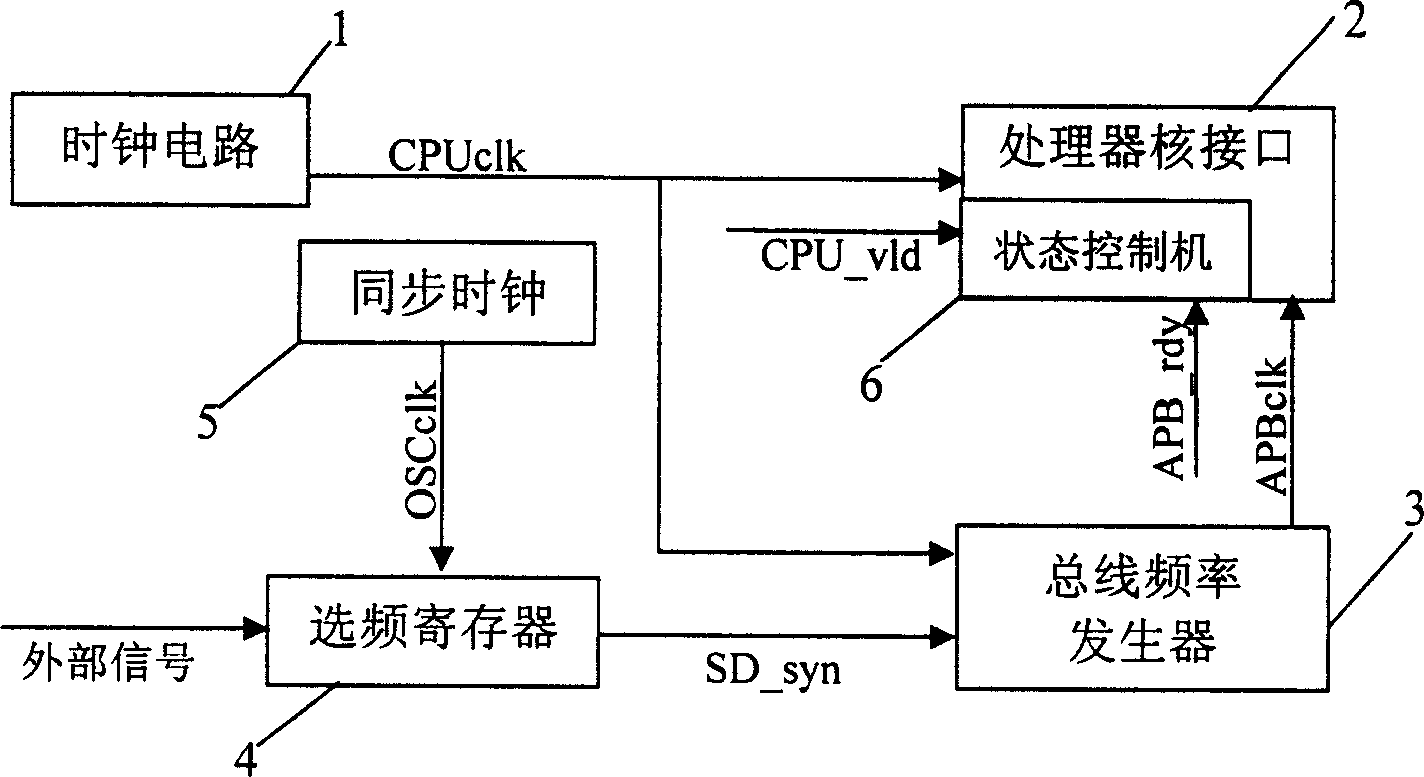

[0020] Such as figure 1 In the high-speed bus dynamic frequency conversion device shown, the clock circuit 1 is conventional and generally consists of a phase-locked loop. The clock circuit 1 provides the main frequency CPUclk for the processor core (not shown in the figure) through the processor core interface 2 .

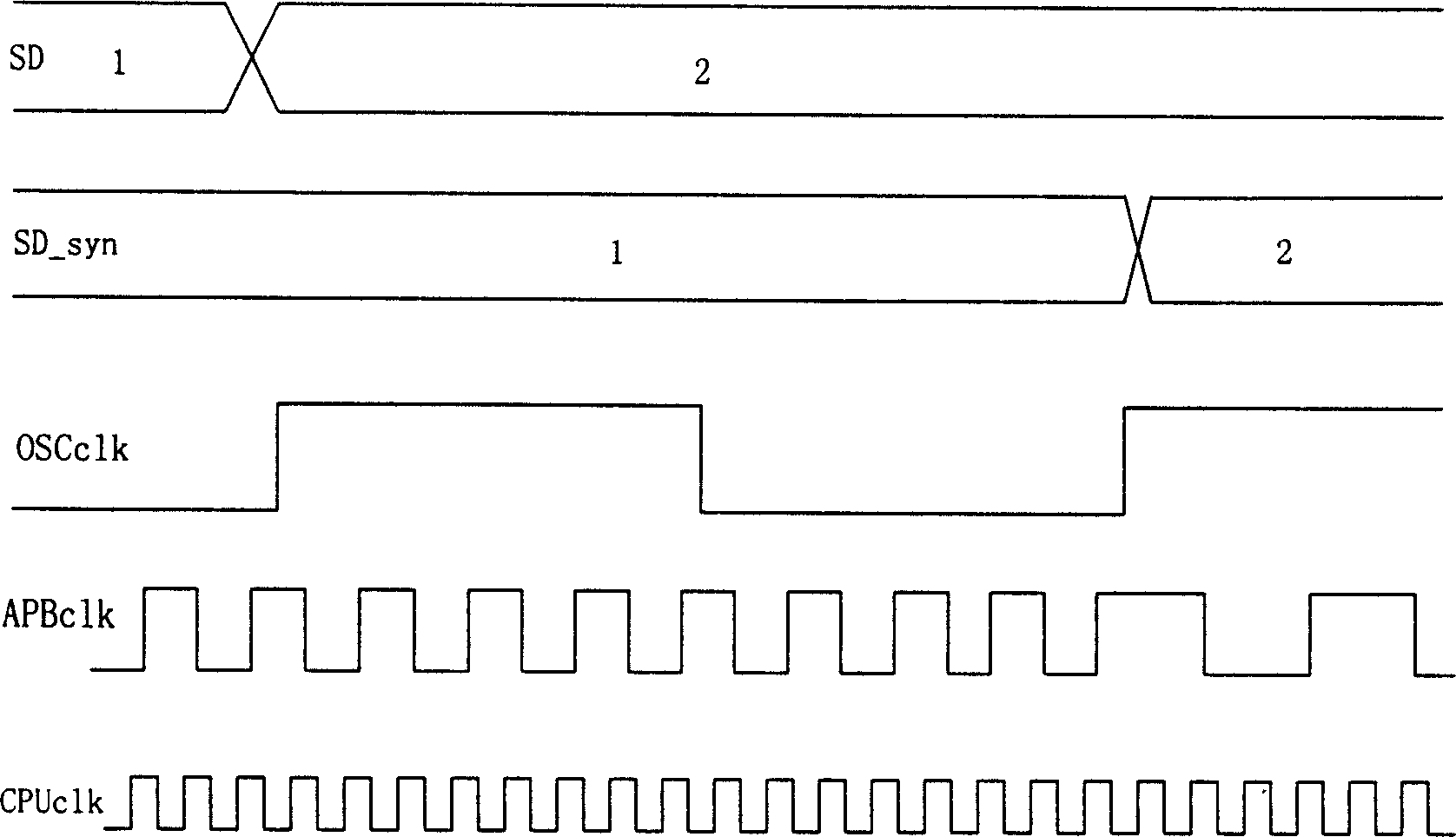

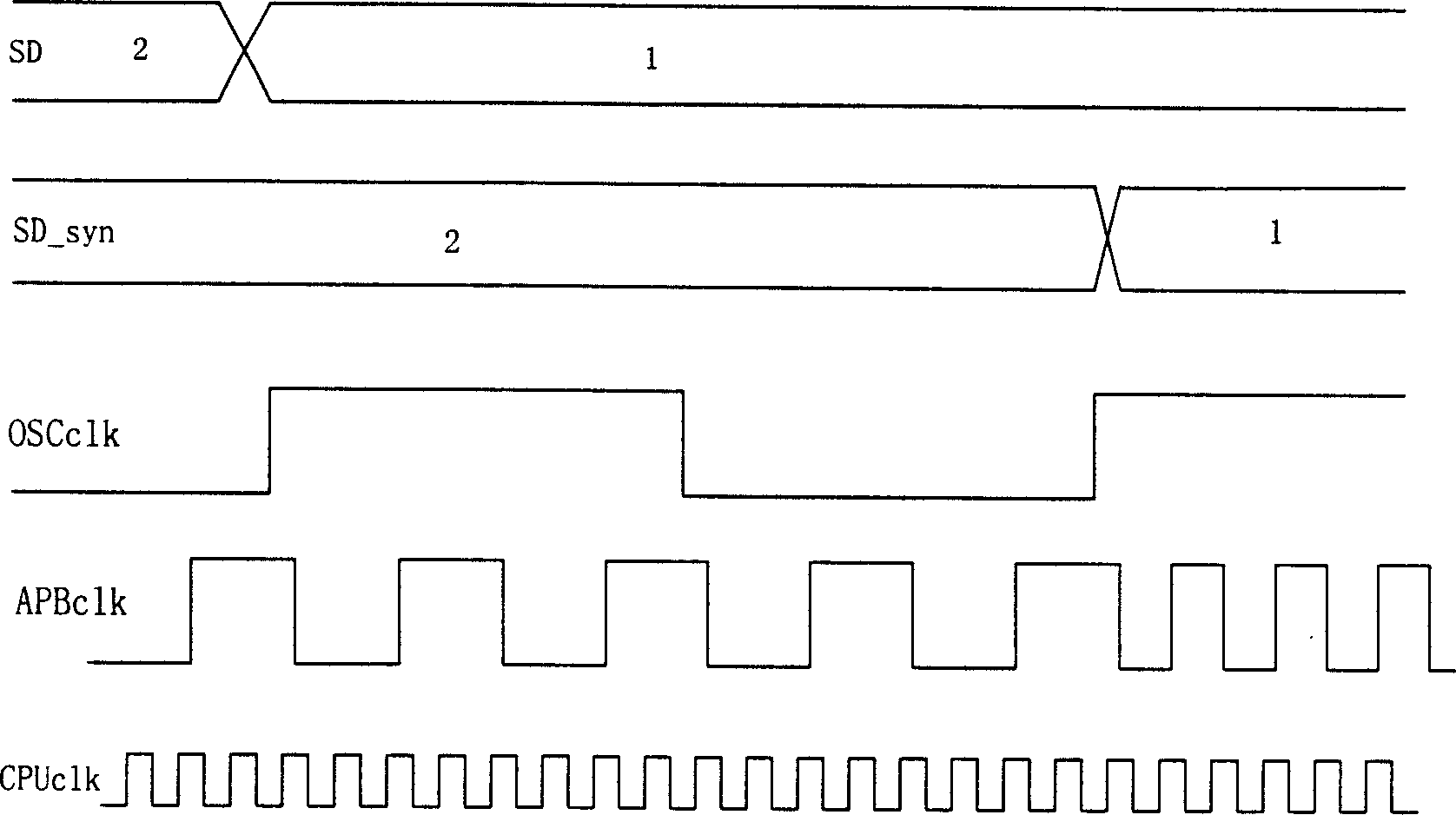

[0021] In the present invention, the processor core main frequency CPUclk is also sent to the bus frequency generator 3 as the bus reference frequency, and the bus frequency generator 3 divides the processor core main frequency CPUclk to provide the bus frequency APBclk. Such as figure 1 As shown, the frequency selection register 4 stores the frequency division relationship value SD of the bus frequency APBclk and the processor core main frequency CPUclk. Due to the need for synchronization across clock domains, the fre...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More