Dynamic frequency conversion device for core of processor under SOC architecture and method

A processor core and frequency conversion device technology, applied in the field of processor core dynamic frequency conversion, can solve uneconomical problems and achieve the effect of saving electric energy and rationally utilizing power consumption

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0026] The present invention will be further described in detail below in conjunction with the accompanying drawings and specific embodiments.

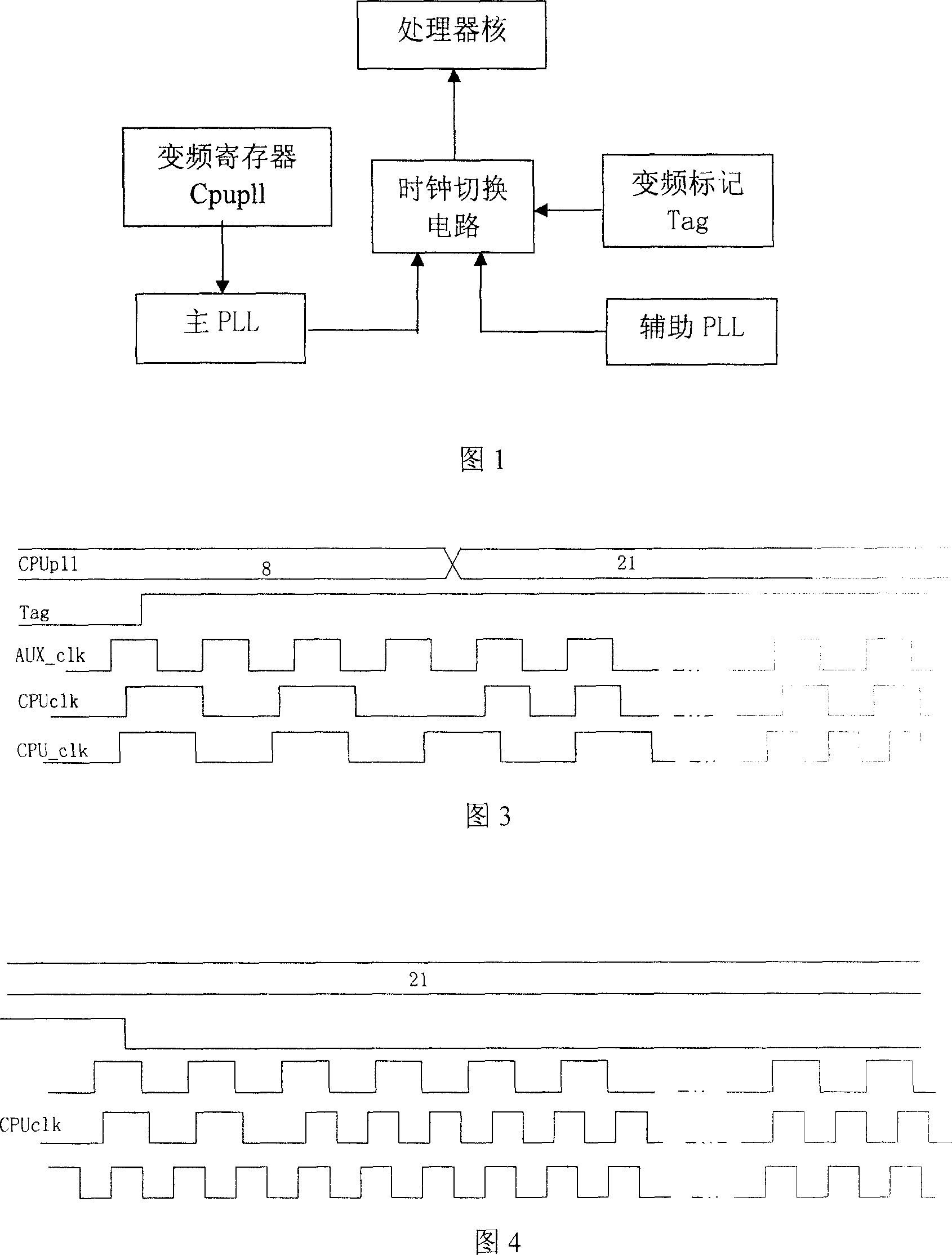

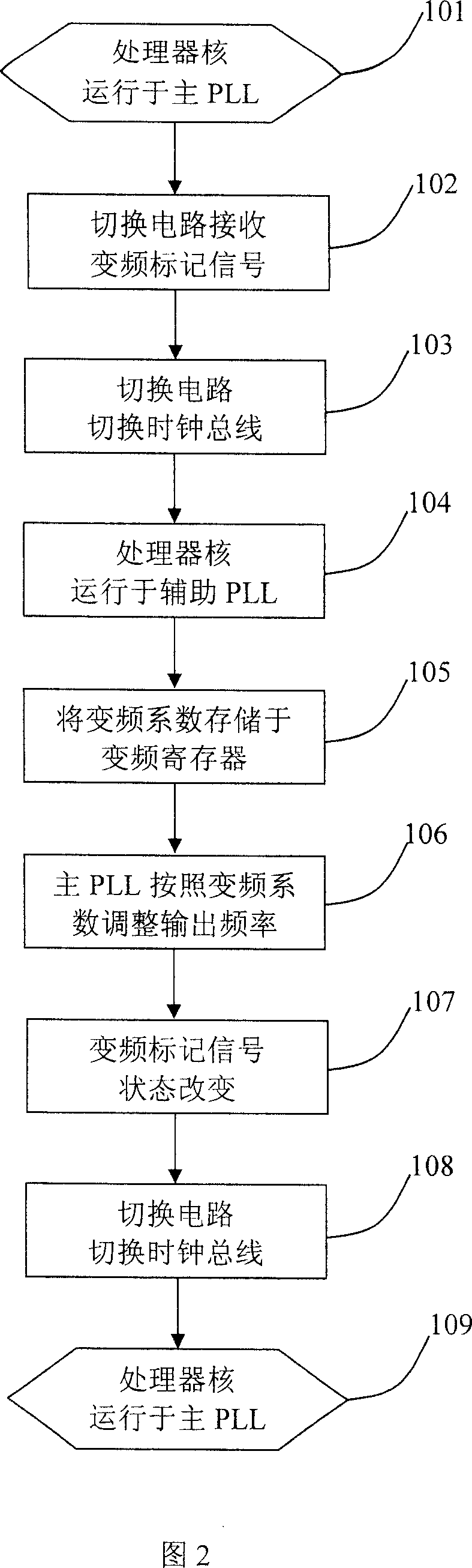

[0027] In the frequency conversion device of the present invention shown in FIG. 1 , the main PLL and the auxiliary PLL provide clock signals for the processor core through a switching circuit. The switching circuit has an input terminal for receiving the variable frequency tag signal Tag. The frequency conversion mark signal Tag controls the switching circuit to switch between the clock signals provided by the main PLL and the auxiliary PLL, so that the switching circuit only provides the clock signal of one of the main PLL and the auxiliary PLL to the processor core at a certain moment. Implementation of the circuits will be apparent to those of ordinary skill in the art. A frequency conversion register is connected with the main PLL, in which the frequency conversion coefficient Cpupll is stored. The main PLL adjusts the frequenc...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More