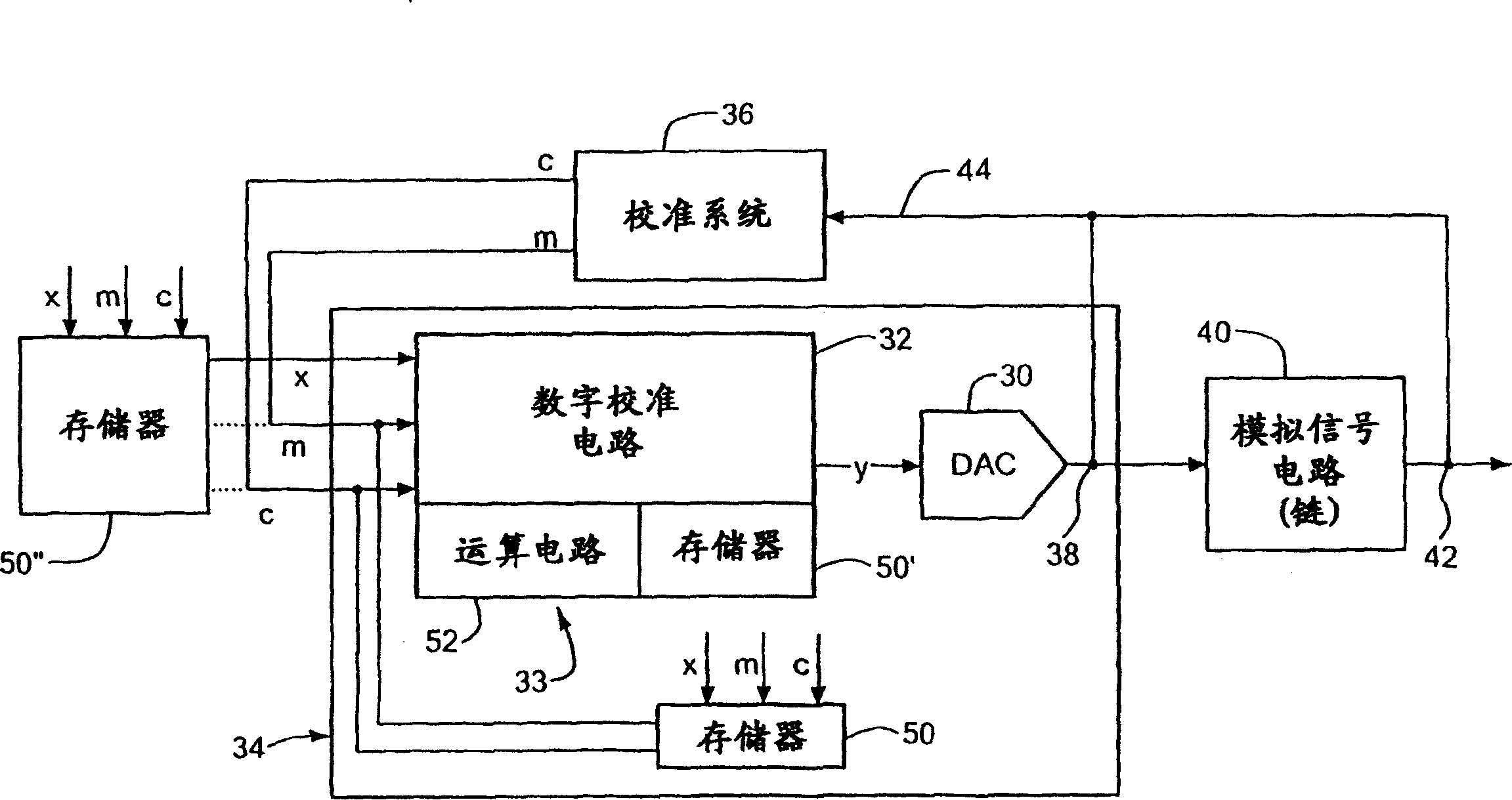

Integrated digital calibration circuit and digital to analog converter (DAC)

A technology for digital-to-analog converters and calibration circuits, applied in the direction of digital-to-analog converters, analog/digital conversion calibration/testing, etc., can solve problems such as high cost, high complexity and cost, and expensive manufacturing technology

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

example 1

[0073] Example 1: Calculating m and c coefficients to correct for gain and offset errors

[0074] Vref+=4.096v

[0075] Vref-=0v

[0076] DAC resolution, N=12

[0077] Therefore, the ideal LSB = 4.096-0 / 2 11 = 1mv

[0078] Step 100 => 102 => Voutzs = -10mv

[0079] Step 100×106 => Voutfs = 4.115v

[0080] New step: calculate LSB size = (Voutfs-Voutzs) / (2 11 -1)=(4.115-0.01) / 4095=1.002442mv

[0081] Calculate c / zs=-(Voutzs-Voutzsideal) / LSB size=-(-0.01-0) / LSB size=9.9756

[0082] Quantize c / zs to required resolution (12b) => 10

[0083] Calculate m=ideal output range / (Voutfs-Voutzs)=4.095 / (4.115-0.010)=0.997564

[0084] Quantize m to required level (12b) => 4086

example 2

[0085] Example 2: Calculating zs and fs coefficients to remove zero-scale and full-scale errors

[0086] We can extend Example 1 and use the same data to calculate new coefficients as follows:

[0087] set dfs=-(Voutfs-Voutfs-ideal) / LSB size=-(4.115v-4.096) / 1.002442mv=18.954=18.954LSB

[0088] Quantize dfs to 12b (LSB) level: dfs→19LSB

[0089] set fs = Voutfs / LSB size = 4.115 / 1.002442mv = 4104.97565

[0090] Quantize fs to 12b (LSB) level: fs→4105

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More