CMOS symmetrical output D flip-latch with self-correction function

A symmetric output, latch technology, applied in the direction of pulse generation, electrical components, and electrical pulse generation, can solve the problem of not providing CLK-D latch circuit structure, not providing NORSR latch circuit structure, and not having resistance. Soft errors and other problems, to achieve the effect of strong resistance to soft errors

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

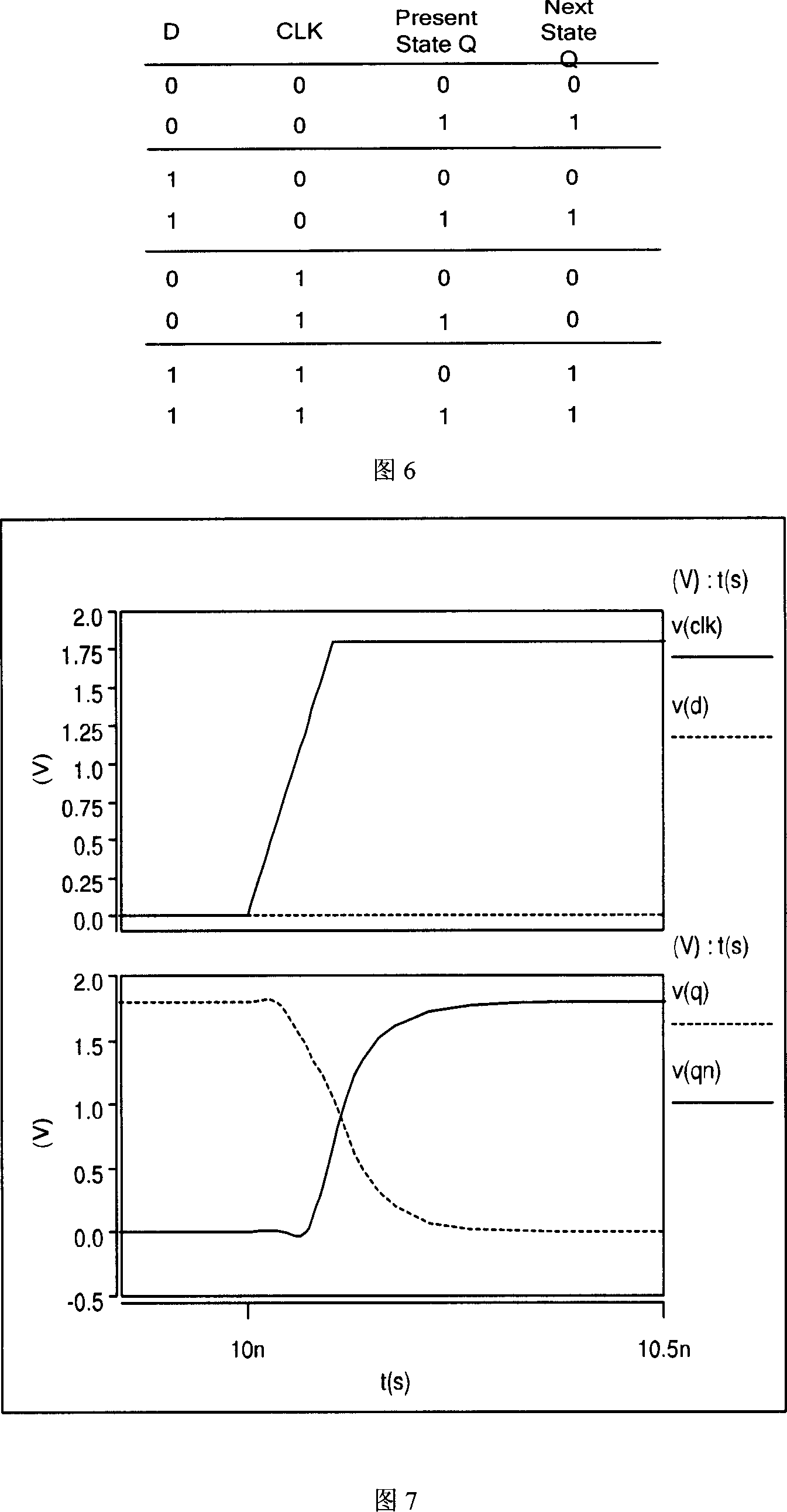

[0018] The technical solution of the present invention to solve the technical problem is: a CMOS symmetrical output D latch with self-correction function controlled by the clock CLK, as shown in FIG. 5 .

[0019] For the CMOS symmetrical output D latch with self-correction function controlled by the clock CLK shown in Figure 5 . When CLK is at low level, n1 and p1 are in cut-off state, p4 and n4 are in conduction state, so the voltage at point Q is in hold state. At the same time, other nodes such as QN, QB, and QNB are also in hold state. When CLK is high, the state of Q depends on the value of D. When D is high, Q is charged through p1 and p2, and QN is discharged through n5 and n6 to realize the function of latching high level. When D is low, Q discharges through n1 and n2, and QN charges through p5 and p6 to realize the function of latching low level.

[0020] It can be seen that in any case there are only two transistors on the charge and discharge branches. Consideri...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More