CMOS symmetrical output SR flip-latch with self-correction function

A symmetrical output, self-correcting technology, applied in the direction of pulse generation, electrical components, generating electrical pulses, etc., can solve the problems of no anti-soft error, no SR latch circuit structure, etc., to achieve the effect of reducing soft errors

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

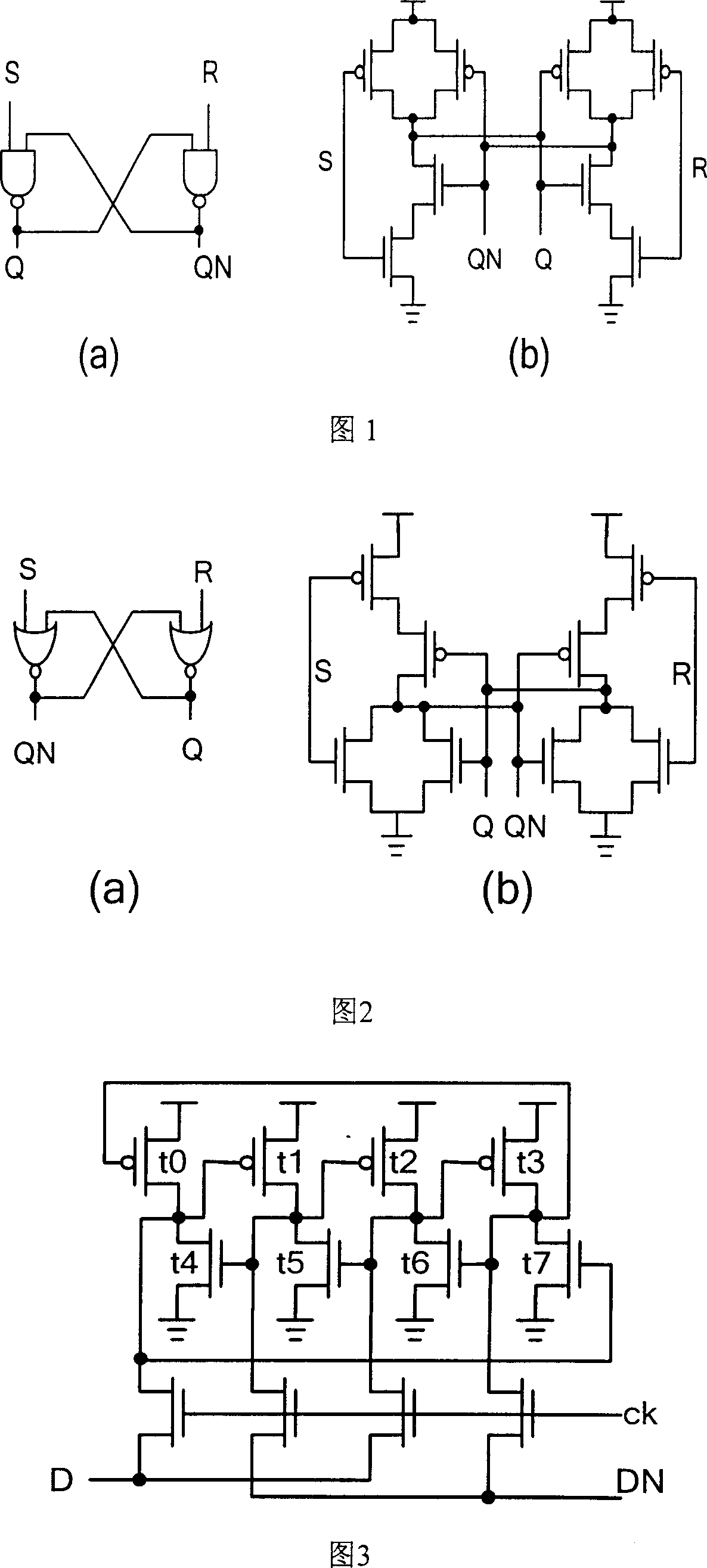

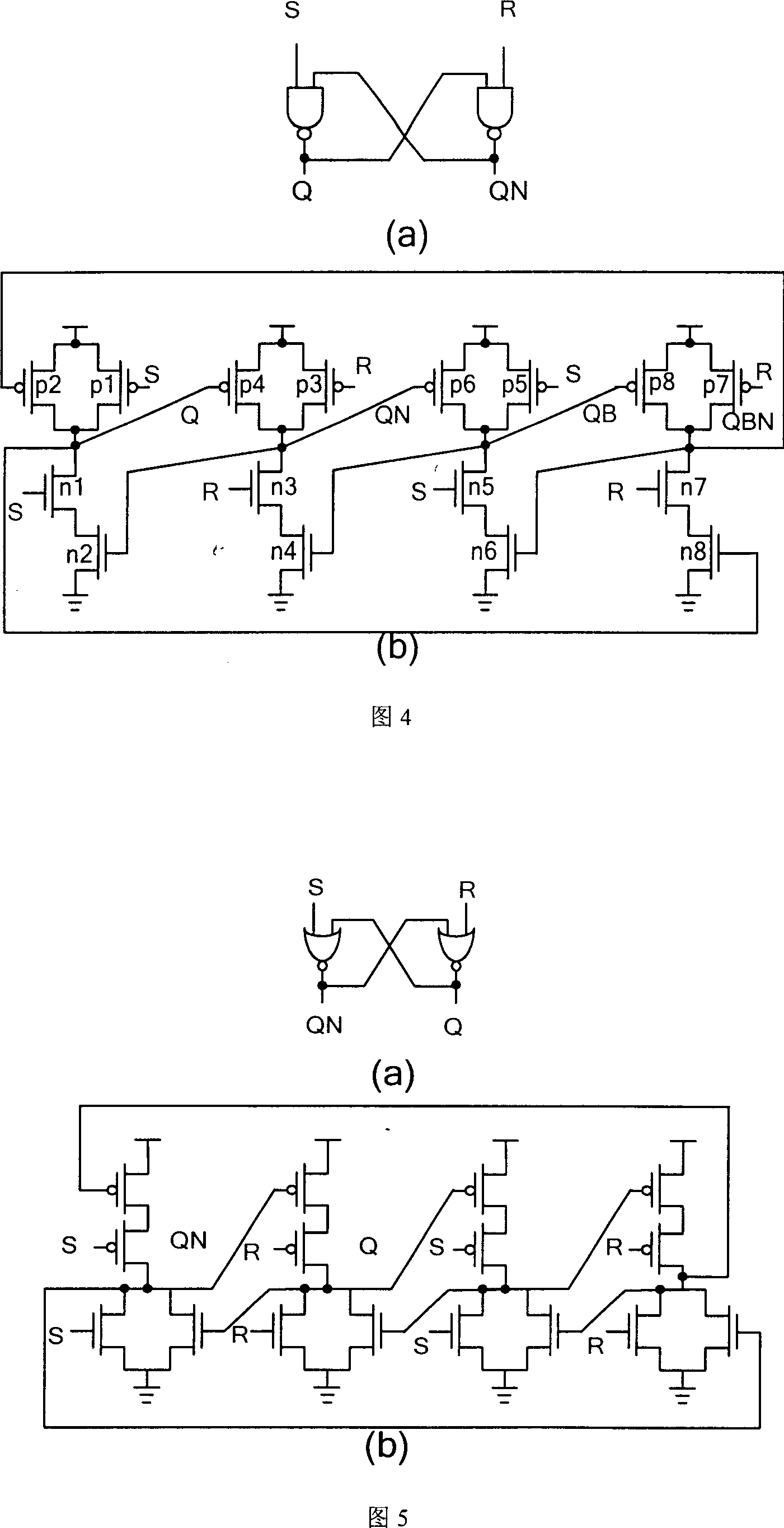

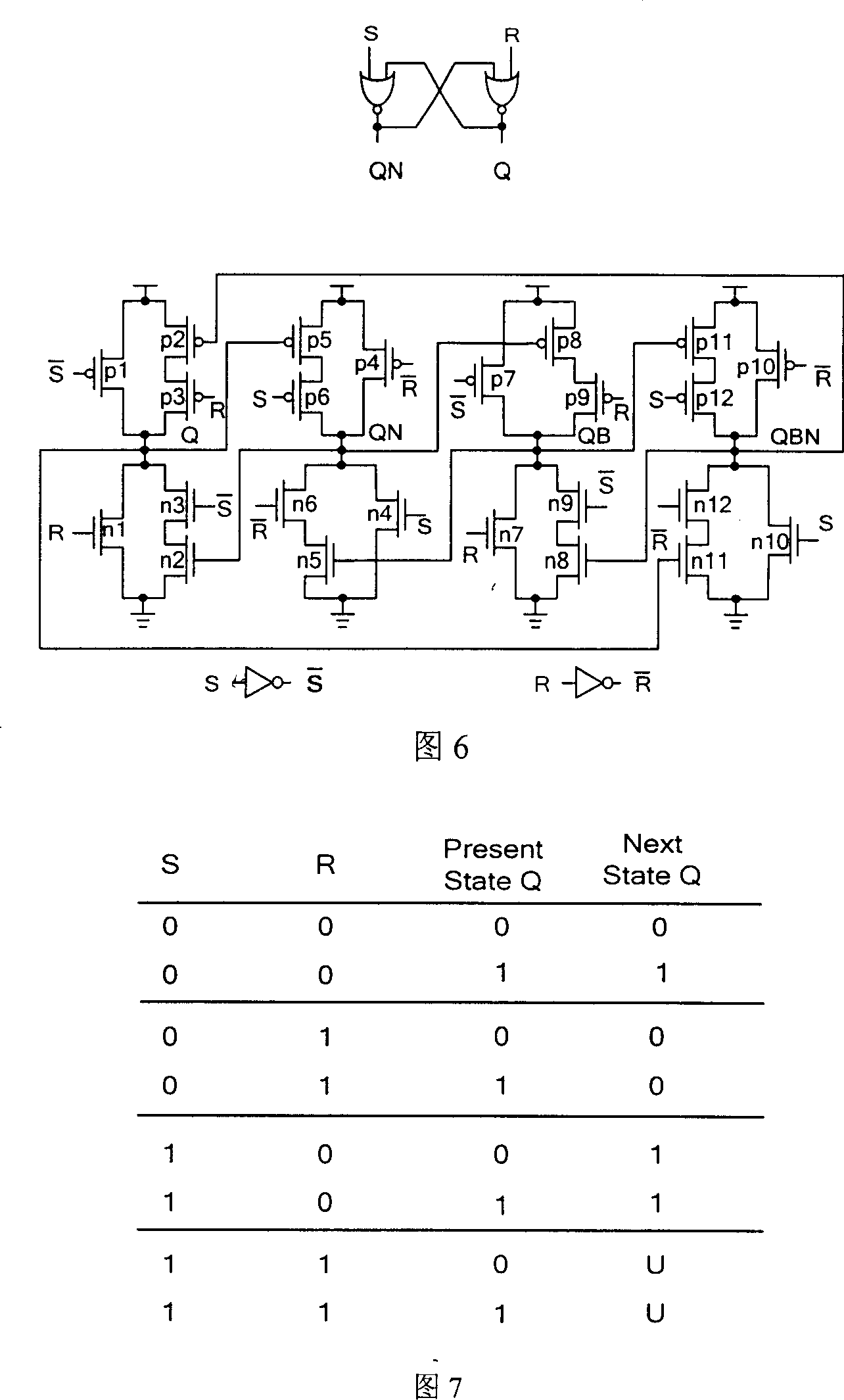

[0022] The technical solution of the present invention to solve its technical problem is: the CMOS symmetrical output SR latch with self-correction function is formed by NOR, as shown in Figure 6; The CMOS symmetrical output SR latch with self-correction function is formed by NAND, As shown in Figure 8. First, we describe the working principle of SEUT_SR composed of NOR.

[0023] For the SR latch composed of NOR shown in Figure 6, Indicates the signal after R is inverted by the inverter, Indicates the signal after S is inverted by the inverter. Since R, S, ,and Only drive the gate of the MOS transistor, ignoring the gate leakage current, no additional current will flow into R, S through the gate, ,and , thus avoiding the problem of reverse drive. For NOR to form an SR latch, R is high and S is high, which is a forbidden input combination. Therefore, we only consider the other three R, S combination states.

[0024] When S is low and R is high, Q is discharged ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More