Methods for assembling semiconductor devices in superimposed relation with adhesive material defining the distance adjacent semiconductor devices are spaced apart from one another

a technology of adhesive material and semiconductor device, which is applied in the direction of semiconductor device details, semiconductor/solid-state device details, electrical apparatus, etc., can solve the problems of wasting adhesive, reducing the actual practice of incorporation of different types of functionality into a single semiconductor device, and severely limited obtainable height of such multi-chip modules, so as to facilitate the introduction and spread of the effect of reducing the overall height of the assembly and facilitating the introduction

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

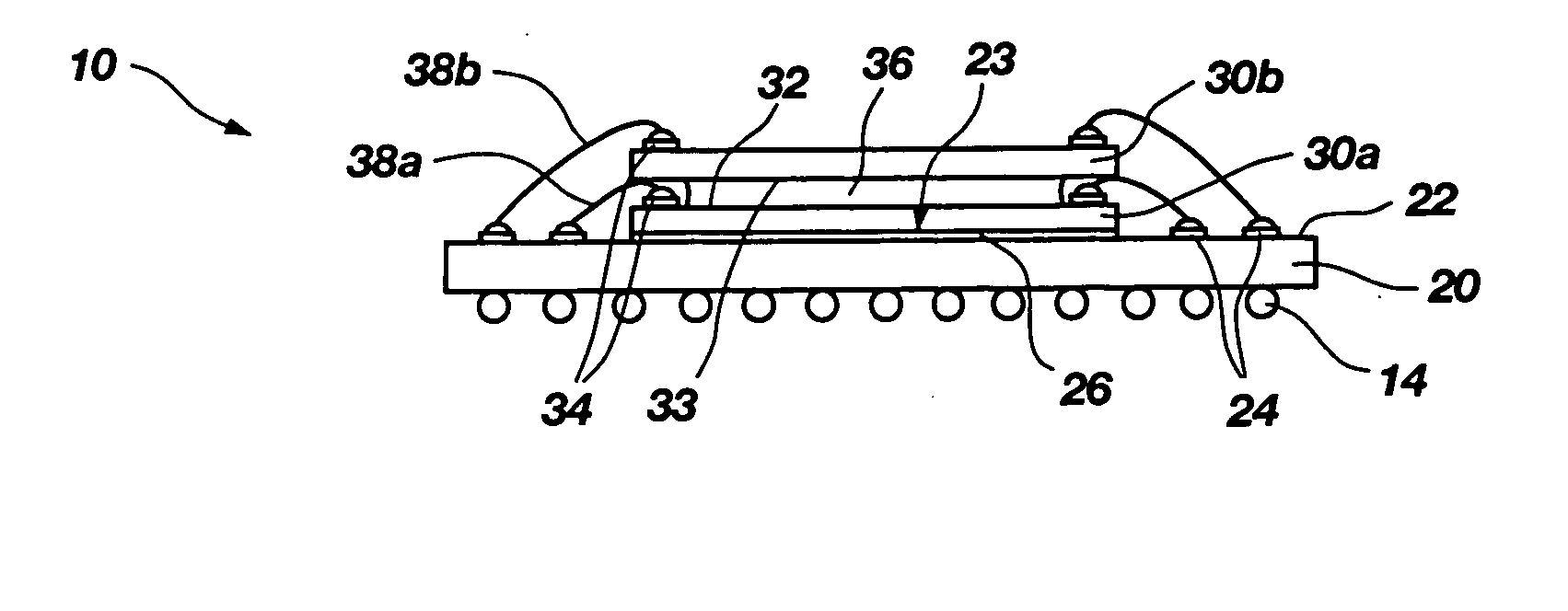

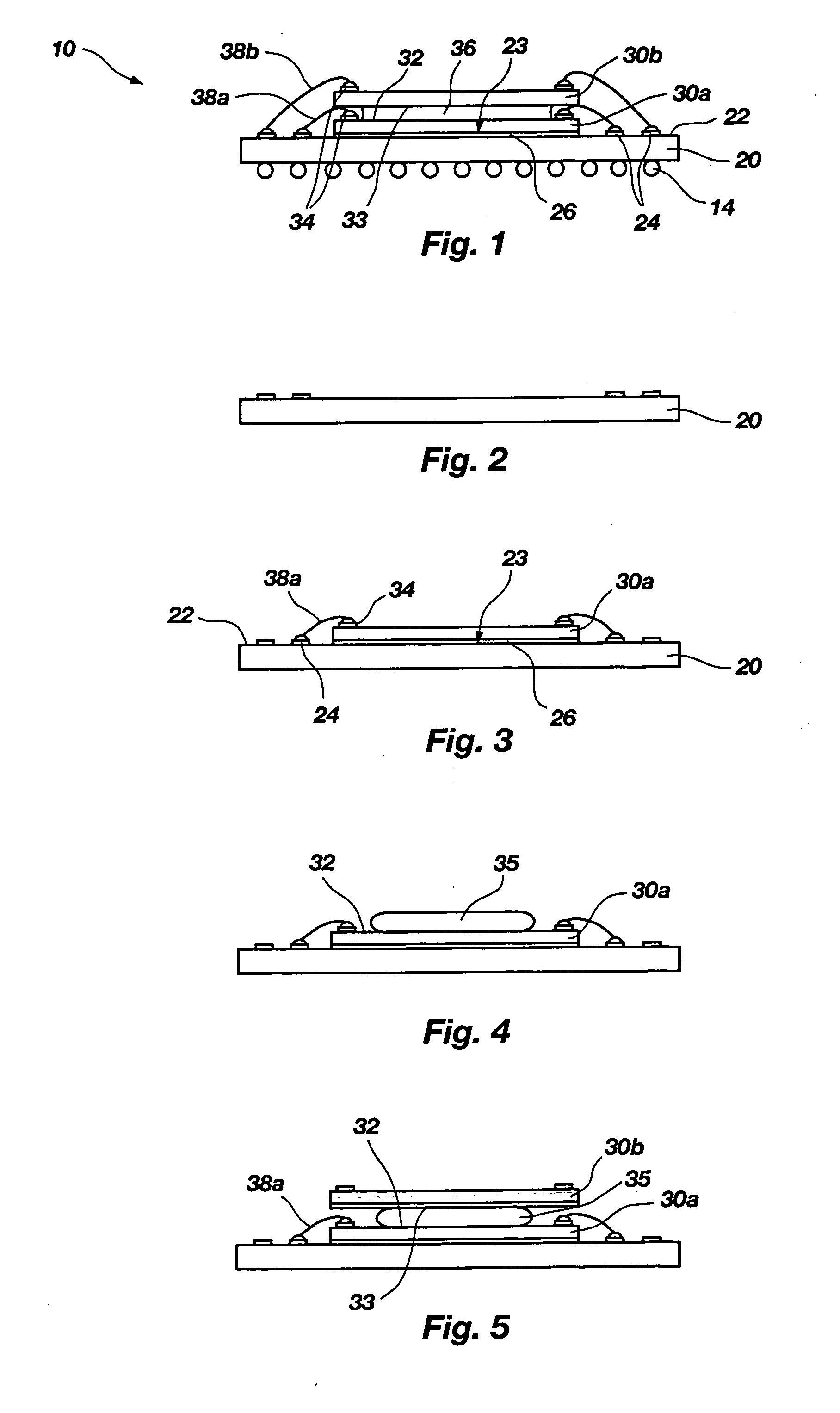

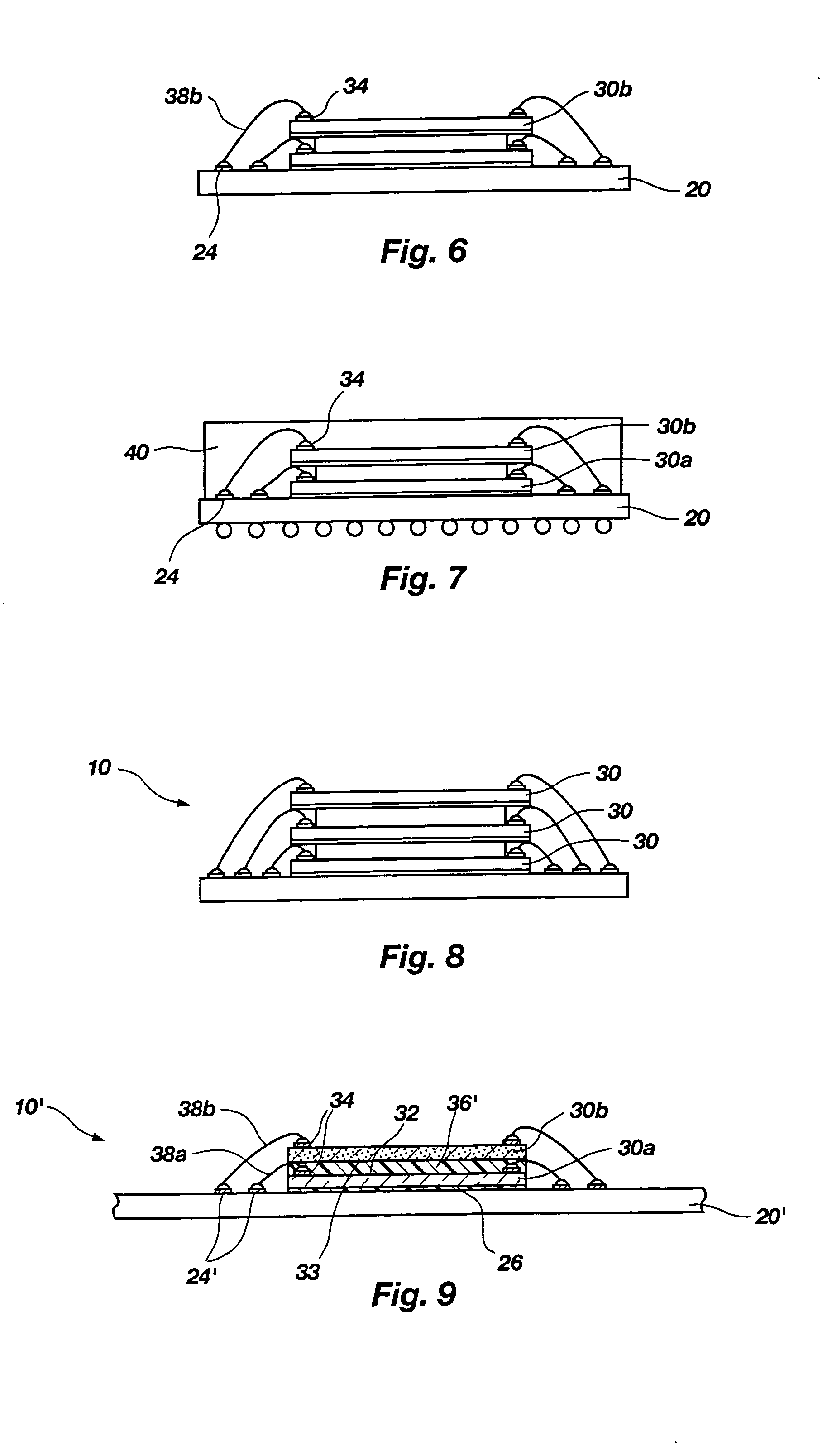

[0041] With reference to FIG. 1, an exemplary embodiment of an assembly 10 incorporating teachings of the present invention is illustrated. As shown, assembly 10 includes a substrate 20 with two semiconductor devices 30a, 30b (collectively referred to as “semiconductor devices 30”) positioned thereover in stacked arrangement.

[0042] The depicted substrate 20 is an interposer with a number of bond pads, which are referred to herein as contact areas 24, through which electrical signals are input to or output from semiconductor devices 30 carried upon or adjacent to a surface 22 of substrate 20. Each contact area 24 corresponds to a bond pad 34 on an active surface 32 of one of the semiconductor devices 30 positioned upon substrate 20.

[0043] Of course, the use of other types of substrates, such as circuit boards, semiconductor devices, leads, and the like, in assemblies and assembly methods incorporating teachings of the present invention is also within the scope of the present invent...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More