Multiple layer structure for substrate noise isolation

a multi-layer structure and substrate technology, applied in the direction of semiconductor devices, semiconductor/solid-state device details, electrical devices, etc., can solve the problems of digital circuit noise interference with the proper functioning of analog circuits, and achieve high impedance noise, high impedance noise, and high impedance noise.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

second embodiment

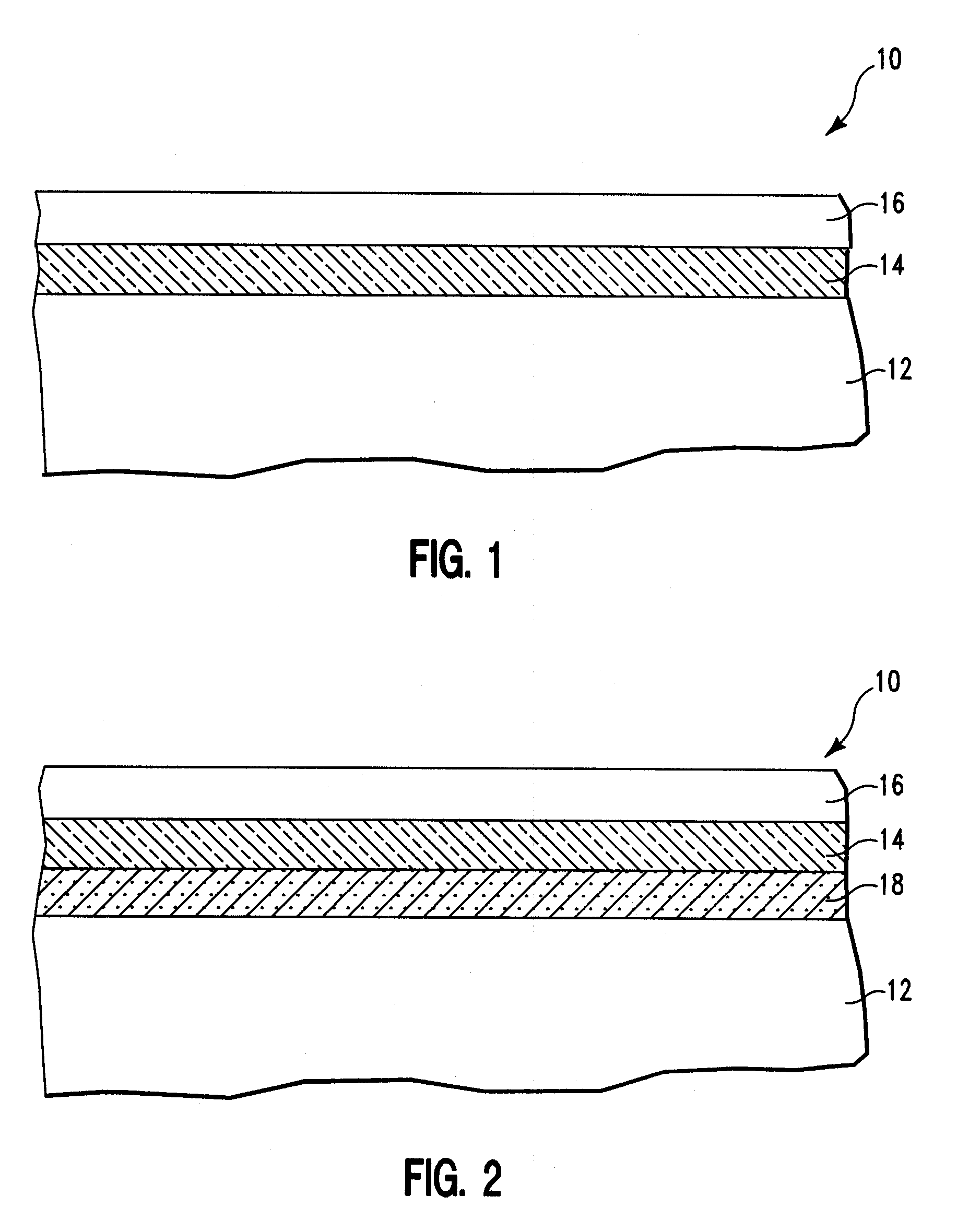

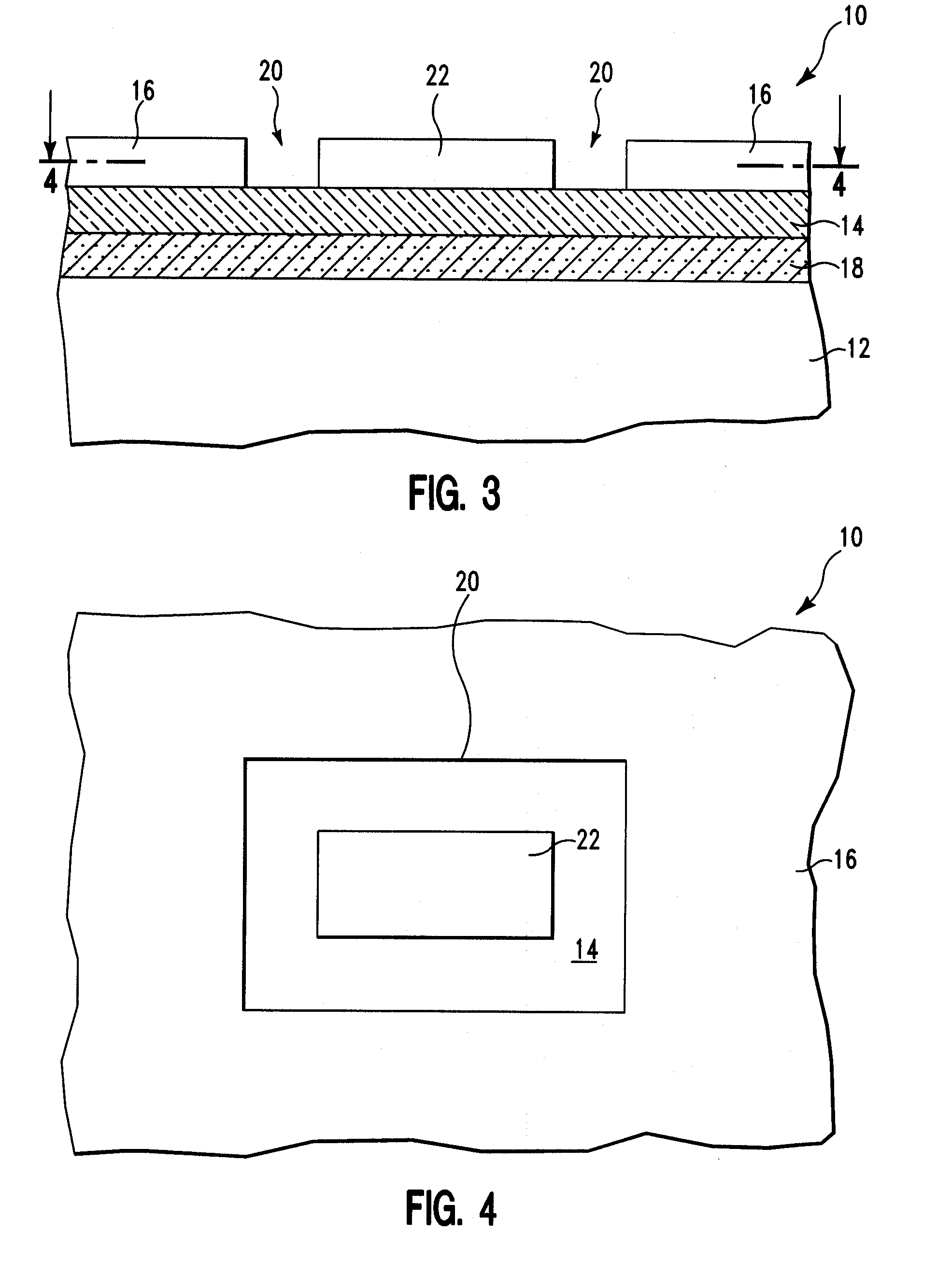

[0055] In accordance with a second embodiment, an SOI 100 comprising a semi-conductive substrate 112, such as silicon (p− or n−), a buried oxide layer 114, such as silicon dioxide, and an upper semi-conductive layer 116 above the buried oxide layer 114, that may comprise the same, or a similar, material as the substrate 112, is formed (FIG. 9). Following formation of the SOI 100, a first heavily doped layer 118 is formed within the SOI 100, beneath the buried oxide layer 114, as illustrated in FIG. 10. The first heavily doped layer 118 may comprise a p+ silicon doped with B, or other similarly used material. The first heavily doped layer 118 may be formed by a conventional ion implantation process, etc. The first heavily doped layer 118 may be formed having a thickness in the range of about 10-500 nm.

[0056] Also illustrated in FIG. 10, a second heavily doped layer 120 is formed within the SOI 100, beneath the buried oxide layer 114 and above the first heavily doped layer 118. The se...

third embodiment

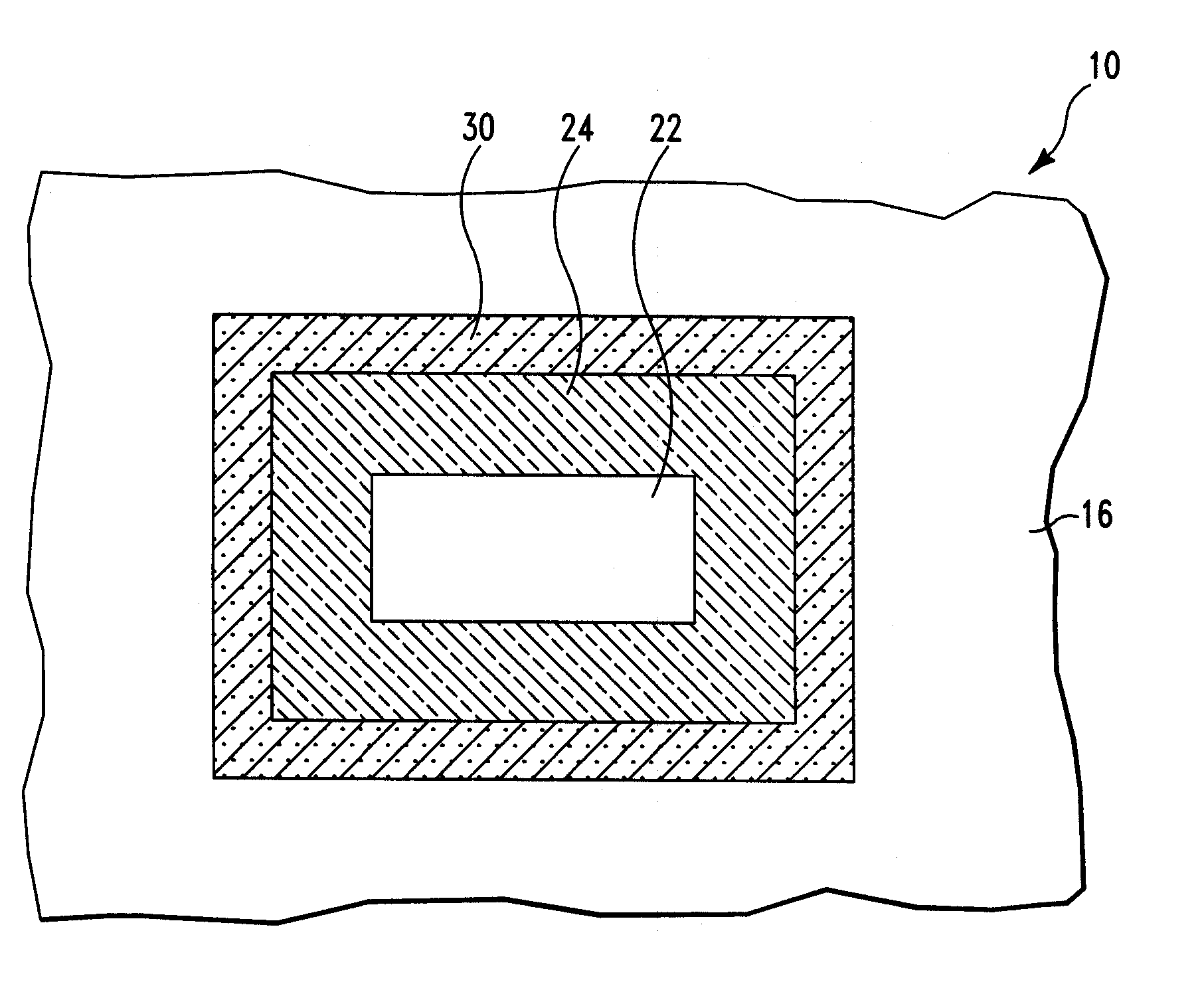

[0065] In accordance with the present invention, an SOI 200 comprising an semi-conductive substrate 212, such as silicon (p− or n−), a first buried oxide layer 214, such as silicon dioxide, a second buried oxide layer 216, such as silicon dioxide, and an upper semi-conductive layer 218 above the second buried oxide layer 216, that may comprise the same material as the substrate 212, are formed (FIG. 26). A heavily doped layer 220 is then formed between the first isolation layer 214 and the second buried oxide layer 216. The heavily doped layer 220 may comprise silicon (p+ or n+) doped with As, P, B, or other similarly used material. One method of forming the SOI structure 200 is to implant oxygen ions twice, each time with different implant energies. The higher energy oxygen ions are implanted within the deeper, or second buried oxide, layer 216 and the lower energy oxygen ions are implanted within the shallower, or first buried oxide, layer 214. Arsenic, P, B, or other similarly us...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More