Etching method

a technology of etching and etching layers, applied in the direction of basic electric elements, semiconductor/solid-state device manufacturing, electric devices, etc., can solve the problems of increasing the difficulty and cost of high-resolution lithography techniques, the cd of the corresponding opening in the etching layer cannot meet the requirement, and the dimension of the semiconductor device unceasingly gets smaller, so as to reduce the after-etching inspection. effect of inspection

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

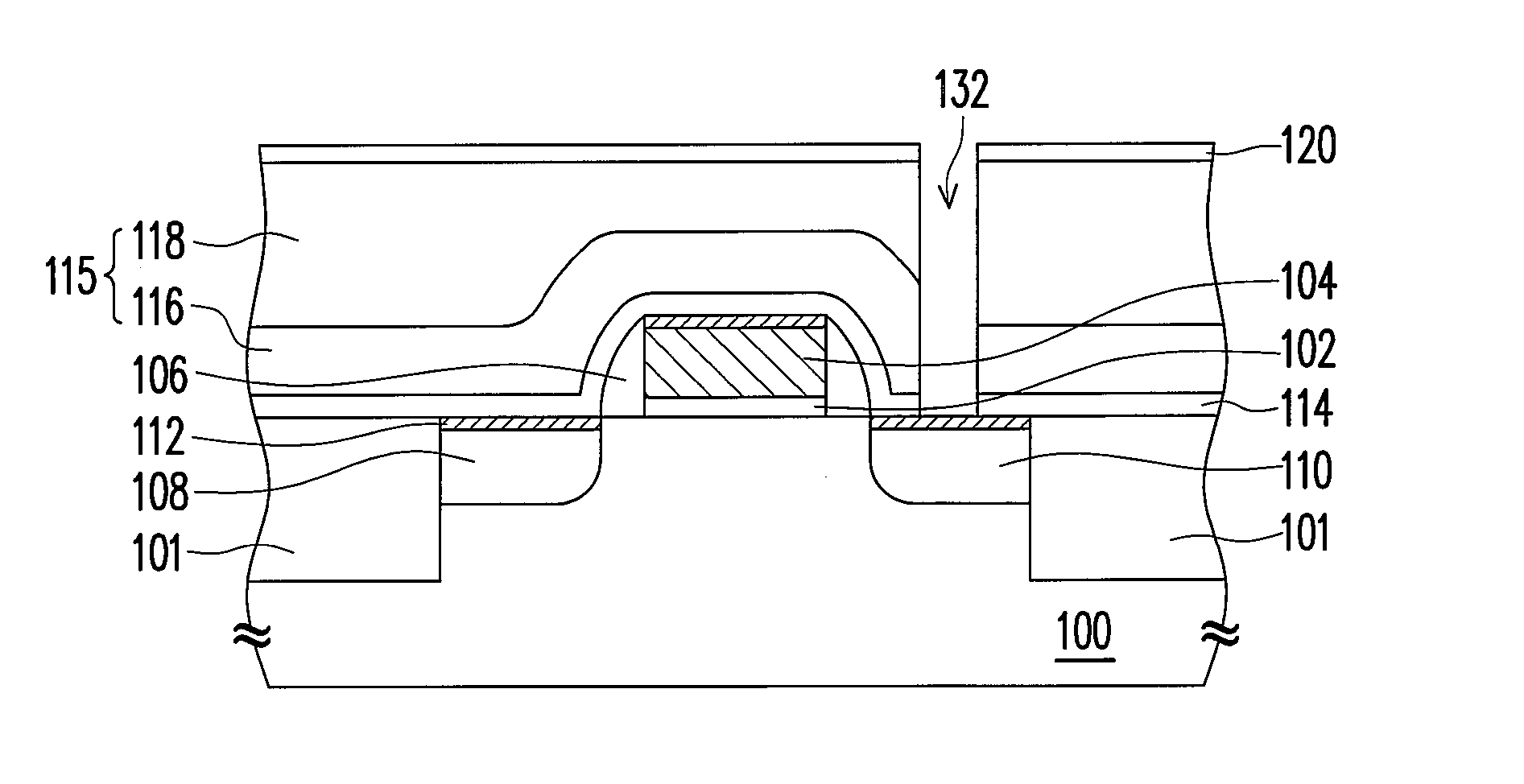

[0028] Referring to FIG. 1A, a semiconductor substrate 100 having a metal-oxide-semiconductor (MOS) device thereon is provided, wherein the MOS device is isolated from adjacent devices by an isolation structure 110 like a shallow-trench-isolation (STI) structure. In the MOS device, a gate 104 is formed on a gate dielectric layer 102, and a spacer 106 is formed on the sidewall of the gate 104. A source region 108 and a drain region 110 are formed in the substrate 100 beside the gate 104. In another embodiment, a metal silicide layer 112 is further formed on the gate 104, the source region 108 and the drain region 110 to reduce their resistance, wherein the material of the metal silicide layer 112 may be nickel silicide, tungsten silicide or cobalt silicide, etc. Because the material and forming method of each part in the above MOS device are known to one of ordinary skills, the description of them is omitted here.

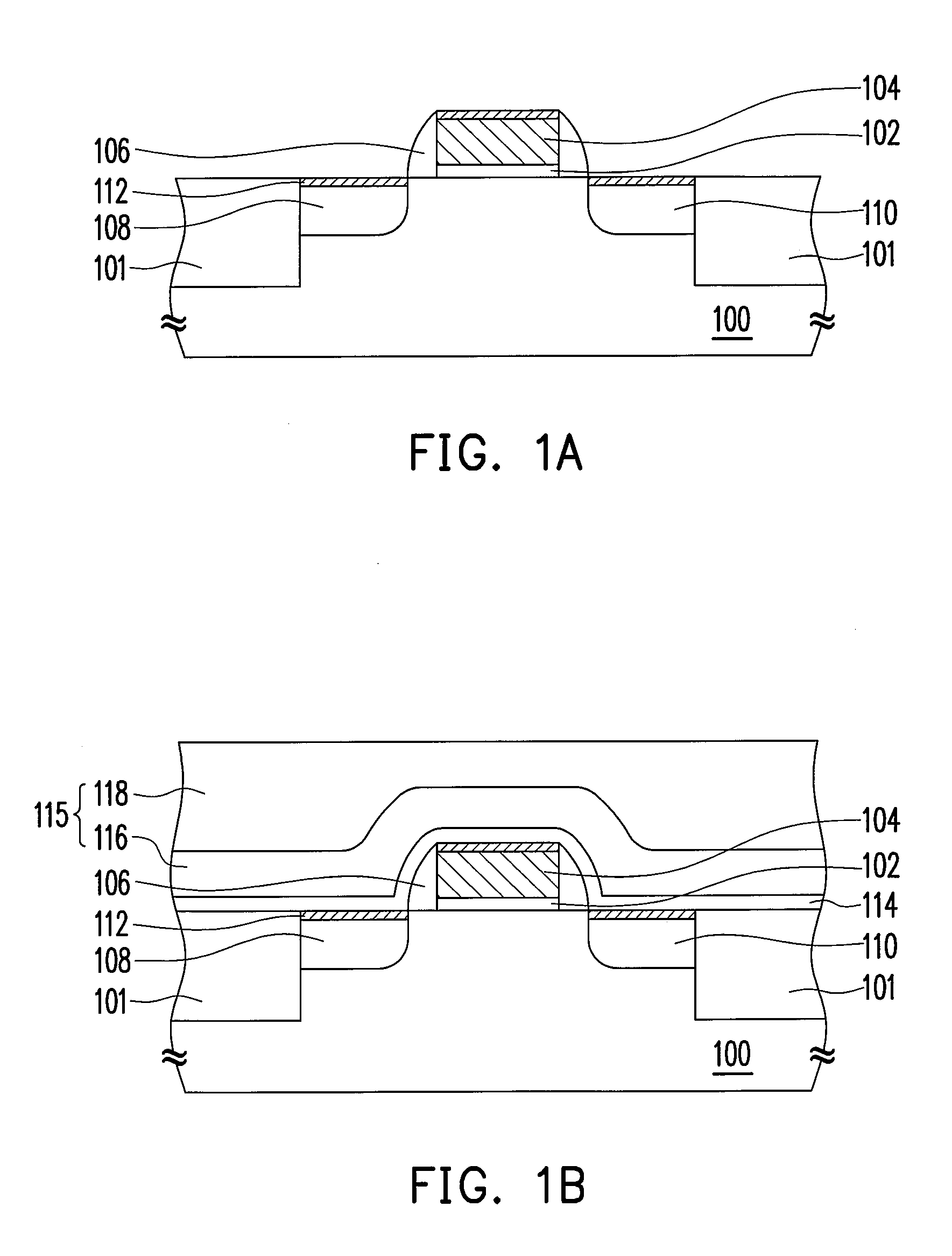

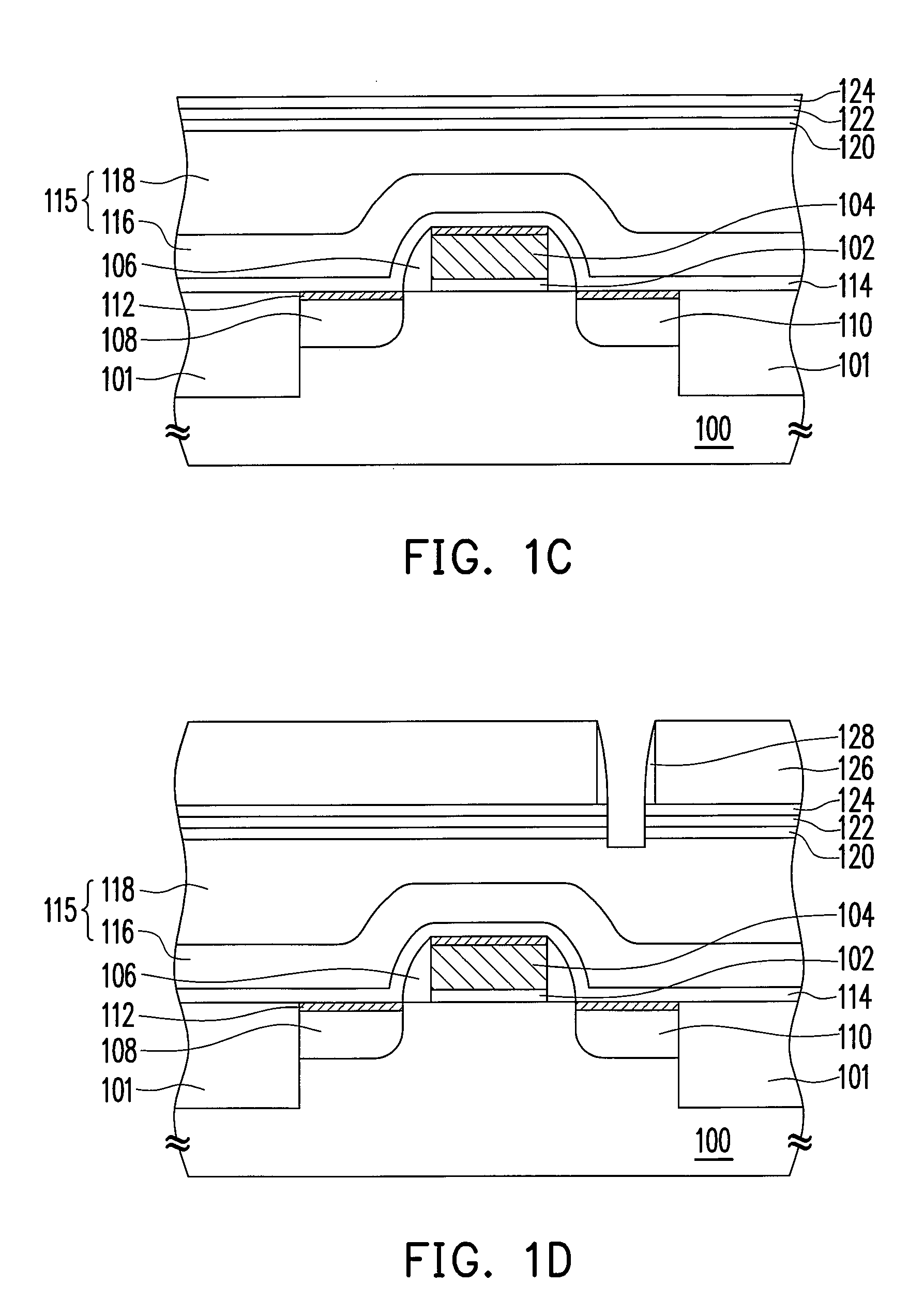

[0029] Referring to FIG. 1B, a dielectric layer 115 is formed on the s...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More