Chip packages with power management integrated circuits and related techniques

a technology of power management and integrated circuits, applied in the direction of printed circuit non-printed electric components, semiconductor/solid-state device details, instruments, etc., can solve the problems of large amount of energy, increase the high cost, so as to reduce the overall difficulty of circuit design, reduce manufacturing costs, and reduce the transient response time

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

embodiment 1

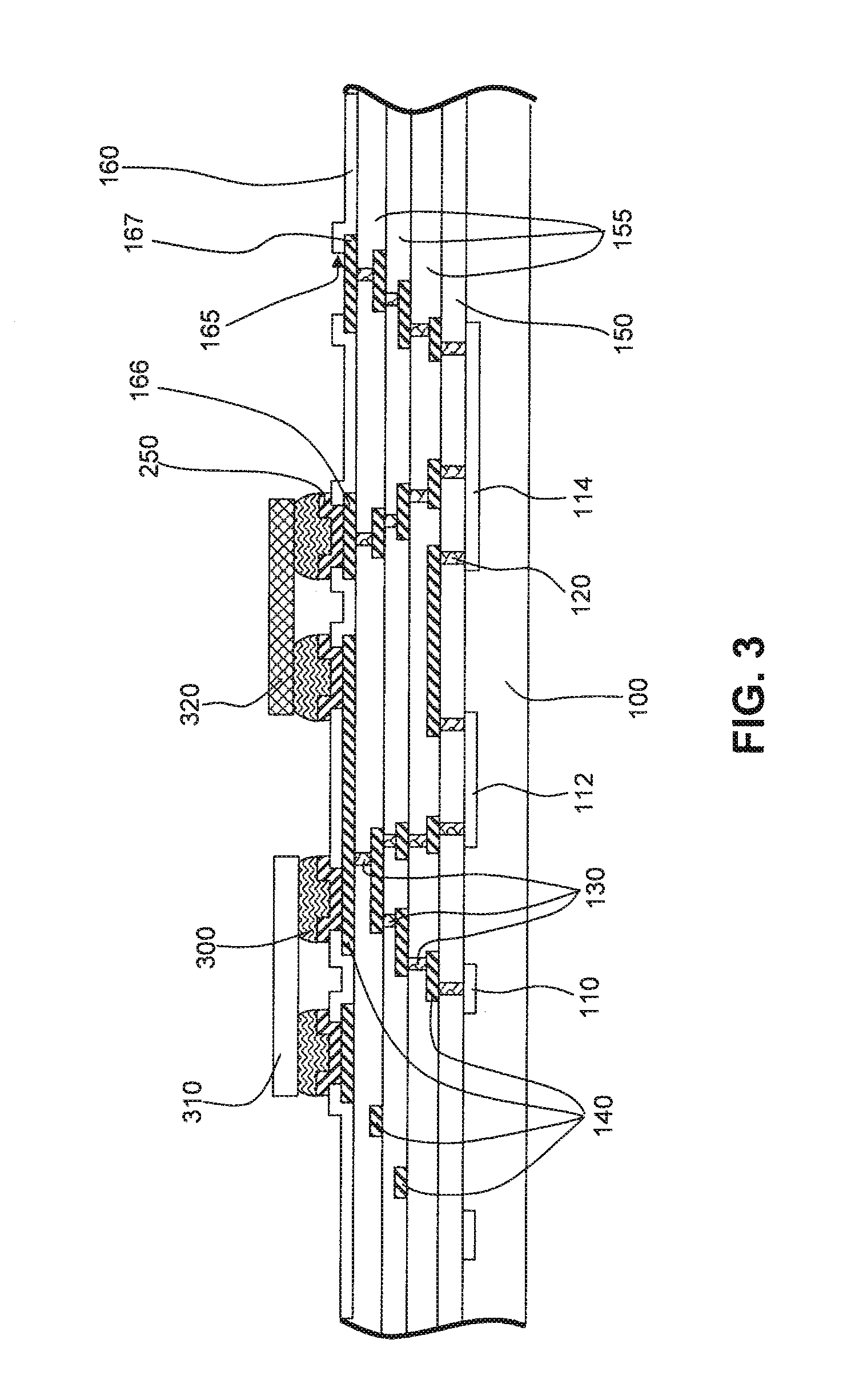

[0060]FIG. 3 depicts a substrate 100 made of a type of semiconductor base. This substrate can be silicon based, gallium arsenide (GaAs) based, silicon indium based (SiIn), silicon antimony based (SiSb), indium antimony based (InSb), or silicon germanium (SiGe) based, and many of the devices, such as devices 110, 112, and 114, are located in or over substrate 100. These devices 110, 112, and 114 can mainly be active devices, though passive devices can also be included. Active devices include voltage feedback devices, switch controller, or MOS devices, such as p-channel MOS devices, n-channel MOS devices, n-channel DMOS devices, p-channel DMOS devices, LDMOS, BiCMOS devices, Bipolar Junction Transistor (BJT), or CMOS.

[0061]As shown in FIG. 3, a thin circuit structure can be disposed or located on substrate 100. This circuit structure can include a first dielectric layer 150, multiple metal layers 140, and at least one second dielectric layer 155. The thicknesses of the first dielectri...

embodiment 2

[0085]Referring to FIG. 4, a chip structure according to a second embodiment (“Embodiment 2”) of the present disclosure is similar to that of the above-described first embodiment (“Embodiment 1”), and therefore an explanation of some of the manufacturing processes and properties will not be repeated. A difference between Embodiment 2 and Embodiment 1 lies in an under bump metal structure 260 and a bonding metal layer 400c that are constructed on or over a pad 166b. The bonding metal layer 400c can be used to connect electrically to external circuits through a copper wire or gold wire formed by wire-bonding (not shown in figure).

[0086]The structure of Embodiment 2 can be manufactured by suitable methods, including the following methods:

Manufacturing Method 1 of Embodiment 2:

[0087]Referring to FIG. 4A, integrated circuit 20 represents all structures below passivation layer 160. Also included in integrated circuit 20 are substrate 100, devices 110, 112, 114, first dielectric layer 150,...

embodiment 3

[0126]Referring to FIG. 5, a third embodiment (“Embodiment 3”) is shown which is similar to Embodiment 2, with a difference being the material and thickness of connecting metal layer 400. In Embodiment 3, solder layer 400 is constructed on pad 166a and 166b. The following is a description of the formation of the structure of Embodiment 3.

Manufacturing Method of Embodiment 3:

[0127]Embodiment 3 can continue from FIG. 4R of manufacturing method 2 of Embodiment 2. Referring to FIG. 5A, a solder layer 400 is formed on metal layer 44 in photoresist layer openings 40a by an electroplating method. The thickness of solder layer 400 can be selected as desired, e.g., between about 30 micrometers and about 350 micrometers. Preferred materials for solder layer 400 include tin / silver, tin / copper / silver, and tin / lead alloy.

[0128]Referring to FIG. 5B, a removal process can be applied to remove the patterned photoresist layer 40 and the portions of seed layer 38 and adhesive / barrier layer 22 that ar...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More