Clock-locked frequency deviation detecting device

A detection device, a technology of frequency deviation, applied in the direction of automatic power control, electrical components, etc., can solve problems such as unfavorable circuit integration and chip design, increase design cost, consume resources, etc. , The effect of reducing the cost of circuit design and reducing the difficulty of circuit design

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0034] In order to make the object, technical solution and advantages of the present invention clearer, the present invention will be further described in detail below in conjunction with the accompanying drawings.

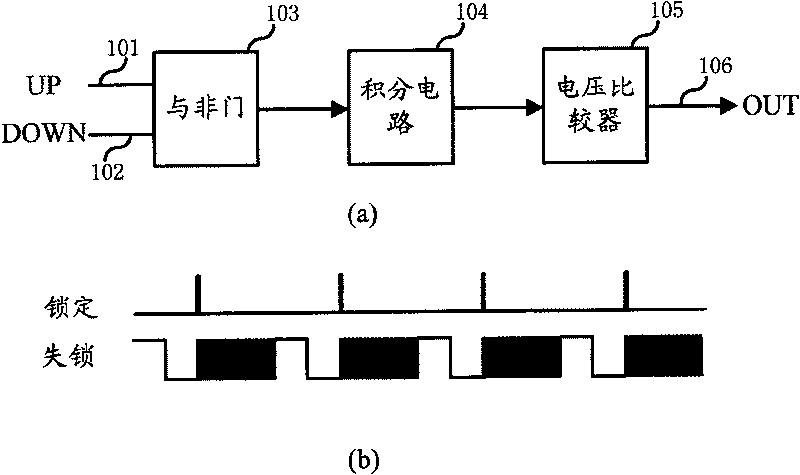

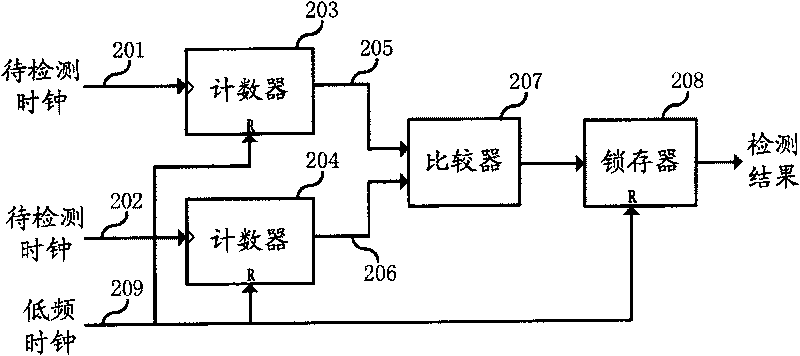

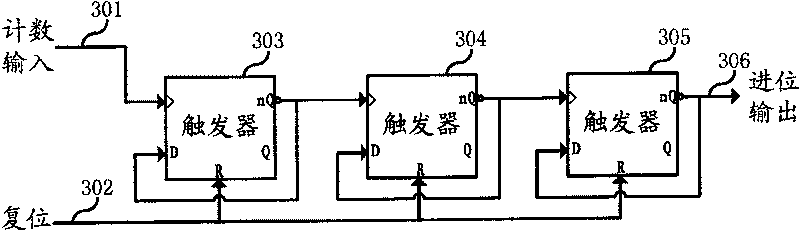

[0035]The basic idea of the present invention is to accumulate and judge the phase difference between the reference clock signal and the output clock signal, which is realized by a digital logic circuit. Specifically, the present invention first determines a detection range according to a low-frequency clock signal, uses two low-bit counters to carry out cyclic counting to the reference clock signal and the output clock signal in this detection range, and counts the counts of the two counters in the counting process Values are compared asynchronously, and the detection of loss of lock and frequency difference can be realized by setting the threshold value. Different from the prior art solution, the present invention adopts the comparison of low-digit counters ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More