Method of joining a chip on a substrate

a technology of chip and substrate, applied in the direction of soldering apparatus, manufacturing tools, auxiliaries welding devices, etc., can solve the problems of substrate bending and warpage, failure of beol structure, and increasing the number of failures, so as to reduce or prevent bending and warping of substrates and chips, the effect of reducing or preventing bending and warping

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

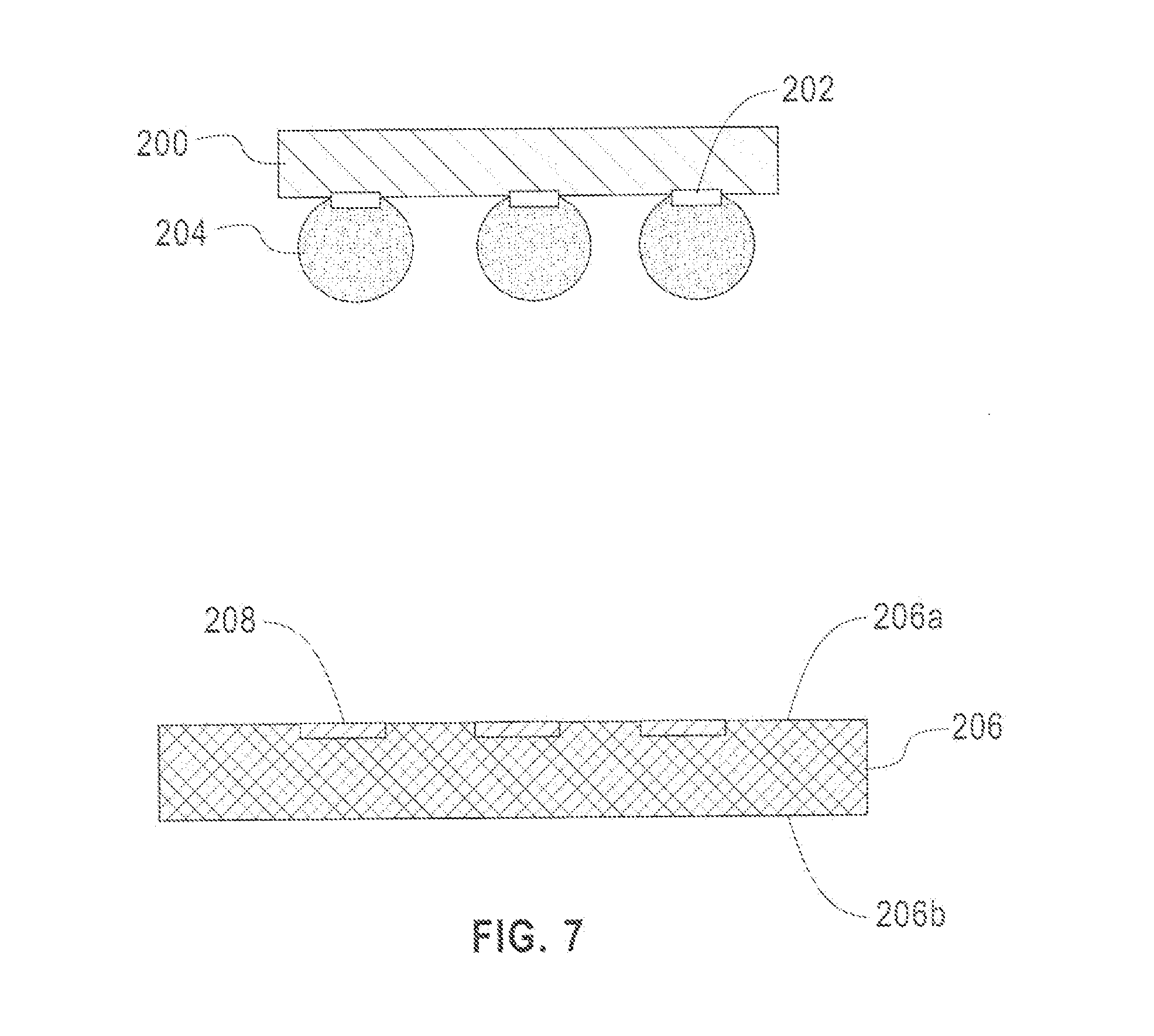

[0061]According to a preferred embodiment, a chip 200 and a substrate 206 are assembled by a flip chip assembly process. As shown in FIG. 7, the chip 200, which may be a silicon chip, includes a plurality of bump limiting metallurgy contacts (BLM) 202 formed or placed on a surface of the chip 200. The BLM 202 typically correspond to I / Os of the chip 200. A bump 204, such as a solder bump, is disposed on each BLM 202. A substrate, such as an organic substrate 206, includes a top surface 206a and a bottom surface 206b. The substrate 206 includes four lateral edges 206c, 206d, 206e, 206f, as shown in FIGS. 8 and 9. The substrate 206 includes a plurality of conductive pads 208 disposed along the top surface 206a of the substrate 206. The bumps 204 can be applied by any means, for example by evaporation, electroplating, direct placement (ball drop), IMS (C4NP), and the like.

[0062]The substrate 206 is positioned on a carrier 210 so that the bottom surface 206b of the substrate 206 contact...

PUM

| Property | Measurement | Unit |

|---|---|---|

| melting points | aaaaa | aaaaa |

| melting point | aaaaa | aaaaa |

| pressure | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More