Integrated circuit design utilizing array of functionally interchangeable dynamic logic cells

a dynamic logic and integrated circuit technology, applied in the field of integrated circuits and integrated circuit design, can solve the problems of inability to design integrated circuits, the complexity of electronic integrated circuits, and the complexity of electronic integrated circuits or “chips” has increased, and the design of integrated circuits has also become more difficul

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

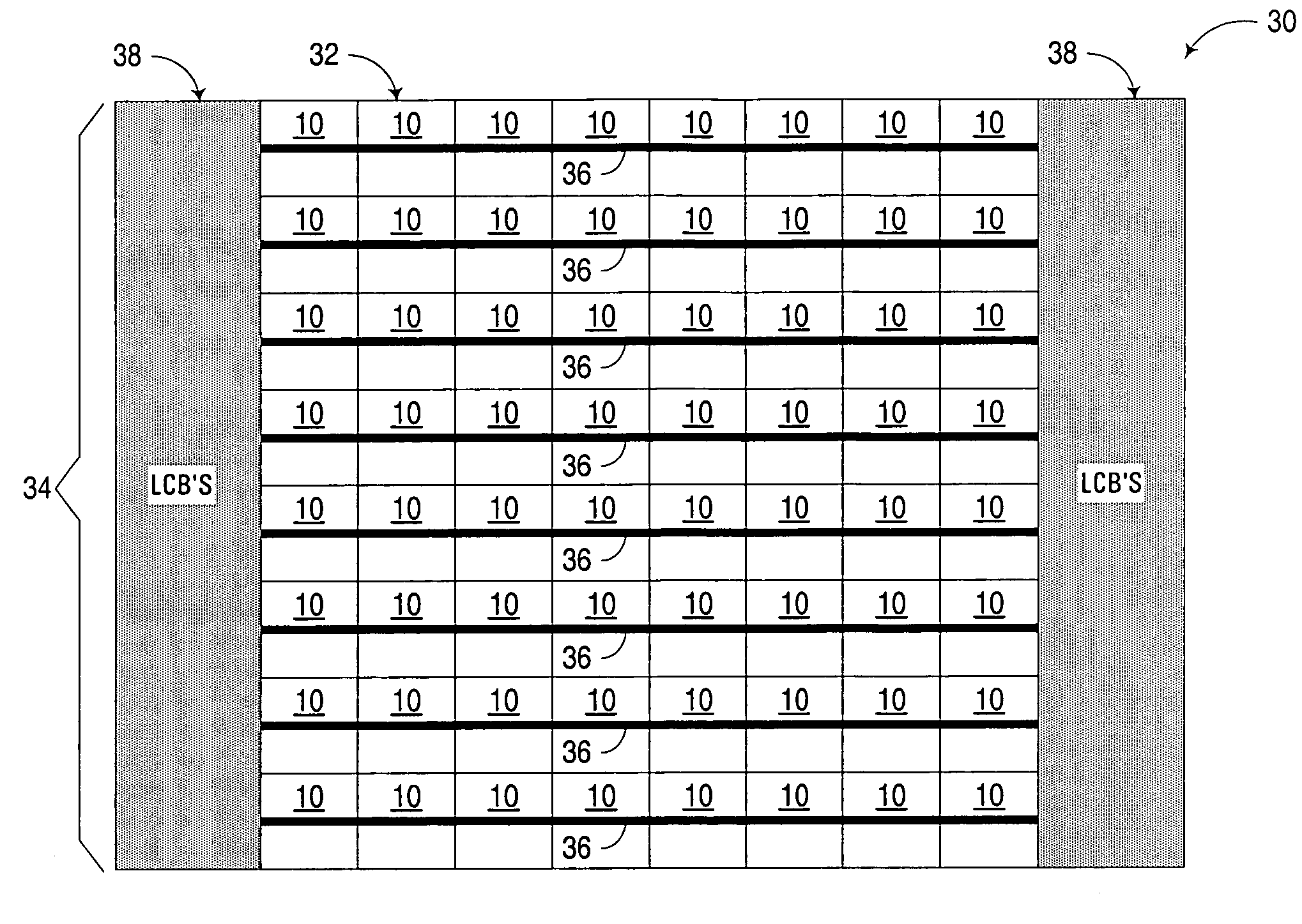

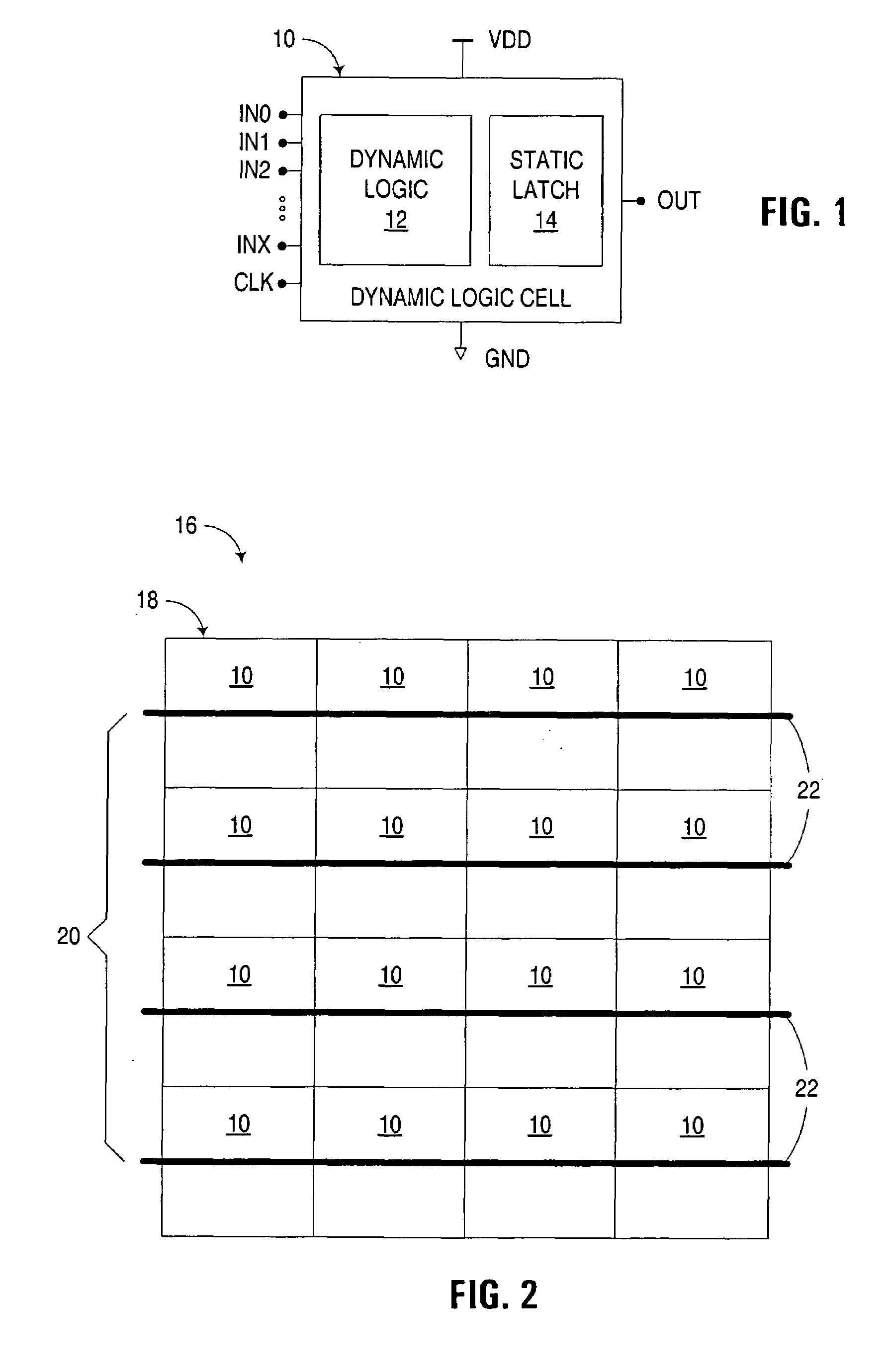

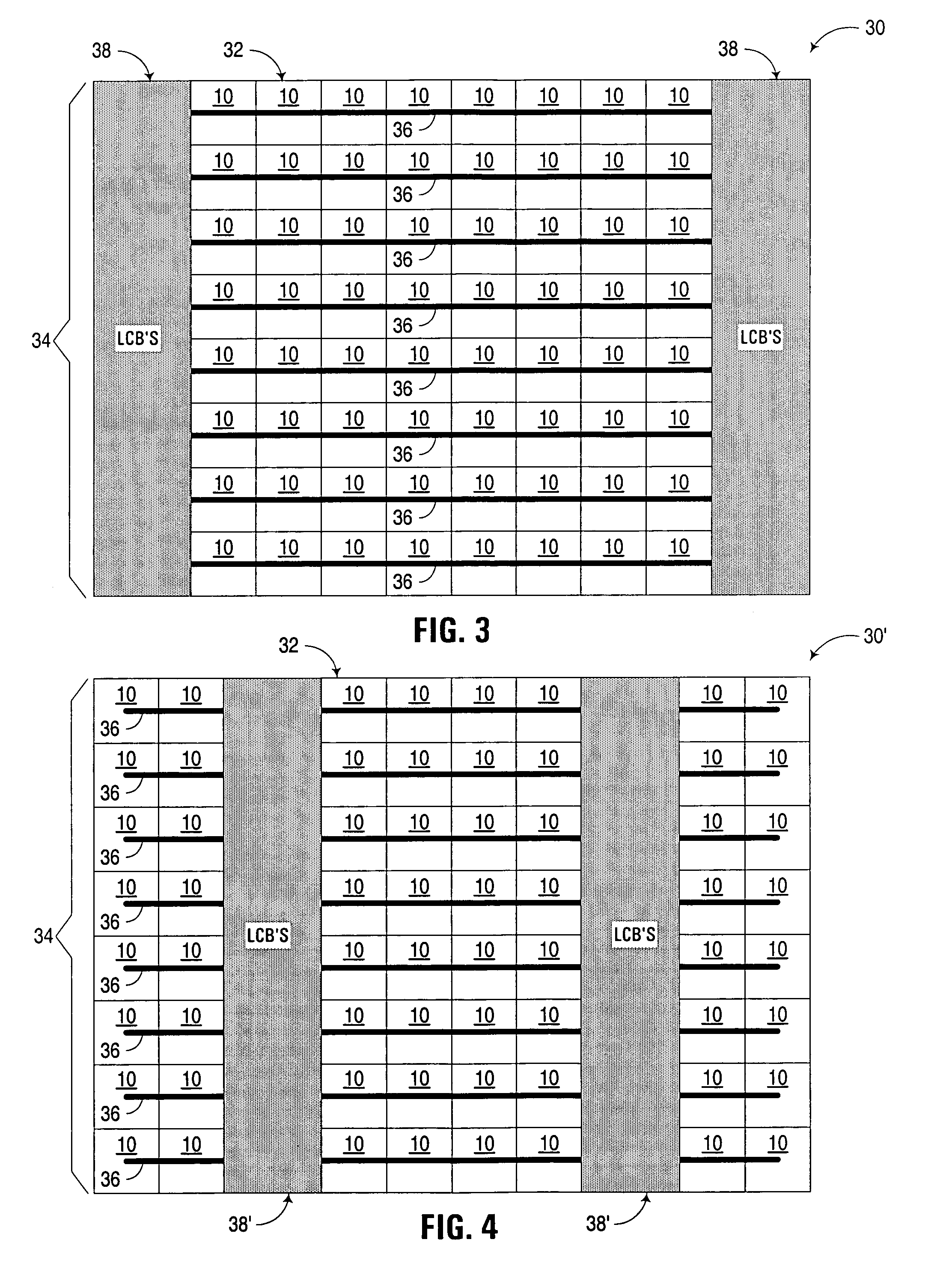

[0023]The embodiments discussed herein utilize an array of functionally interchangeable dynamic logic cells to implement application specific logic functions in an integrated circuit design.

[0024]A functionally interchangeable dynamic logic cell consistent with the invention incorporates an output latch implemented using static logic to capture a logic state generated by a dynamic logic circuit at a dynamic node in the cell. By doing so, the cell offers a stable storage element.

[0025]In addition, dynamic logic cells consistent with the invention are functionally interchangeable to the extent that each logic cell implements the same logical function such that any logic cell in an array may be substituted for another logic cell in the array when mapping the desired application specific logic function to the array of logic cells. While in many embodiments each functionally interchangeable dynamic logic cell may be identical also in terms of physical design and layout, in other embodime...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More