Method for restricting poly-silicon pattern

A technology of polysilicon and polysilicon layer, which is applied in the direction of electrical components, semiconductor/solid-state device manufacturing, circuits, etc., to achieve the effect of improving uniformity

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

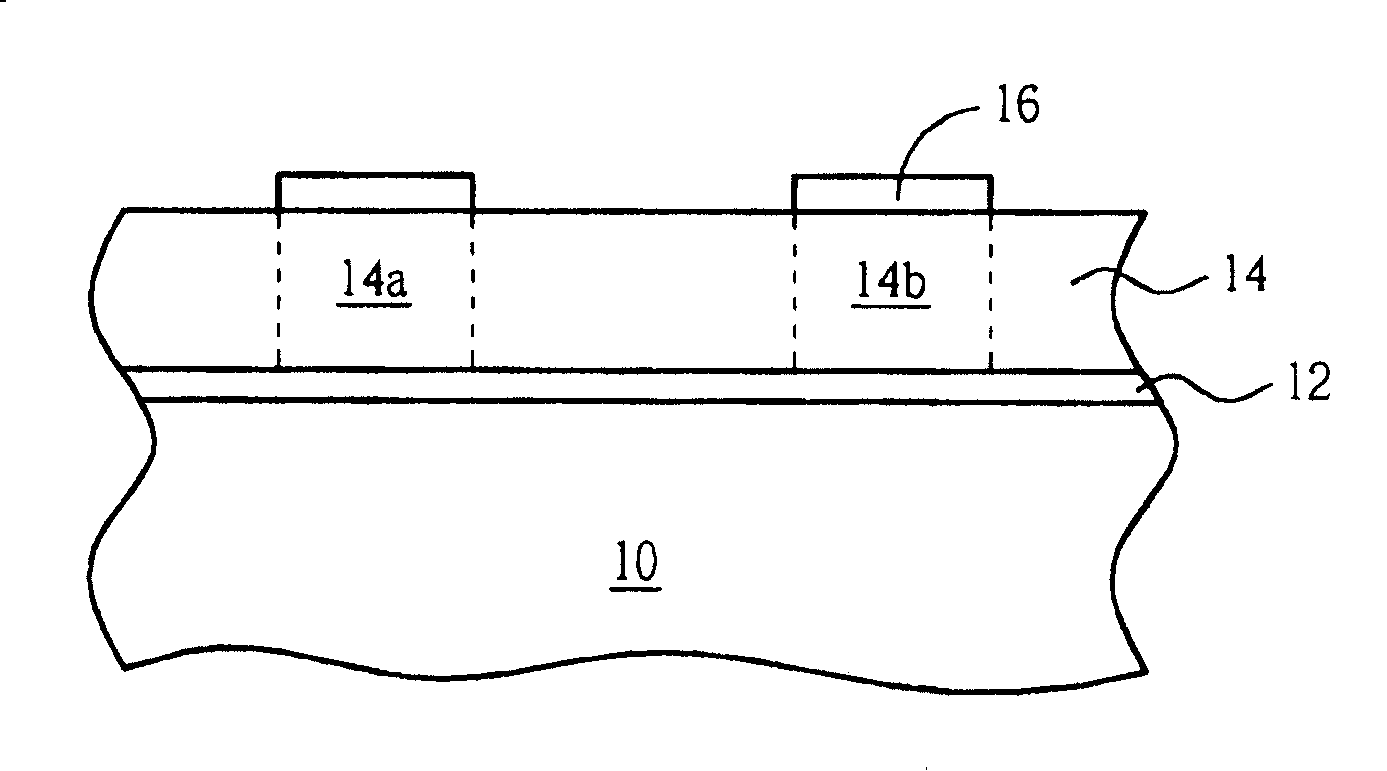

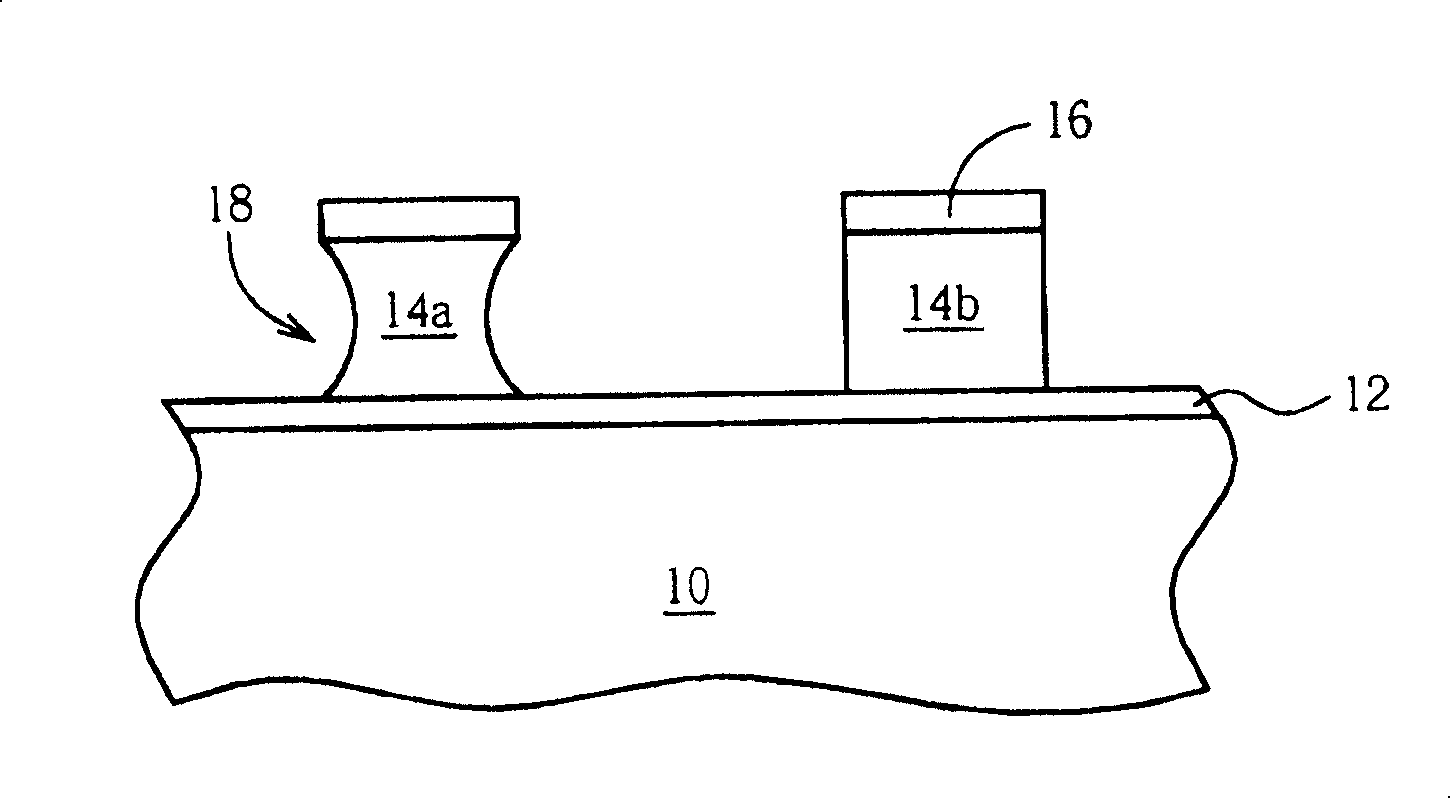

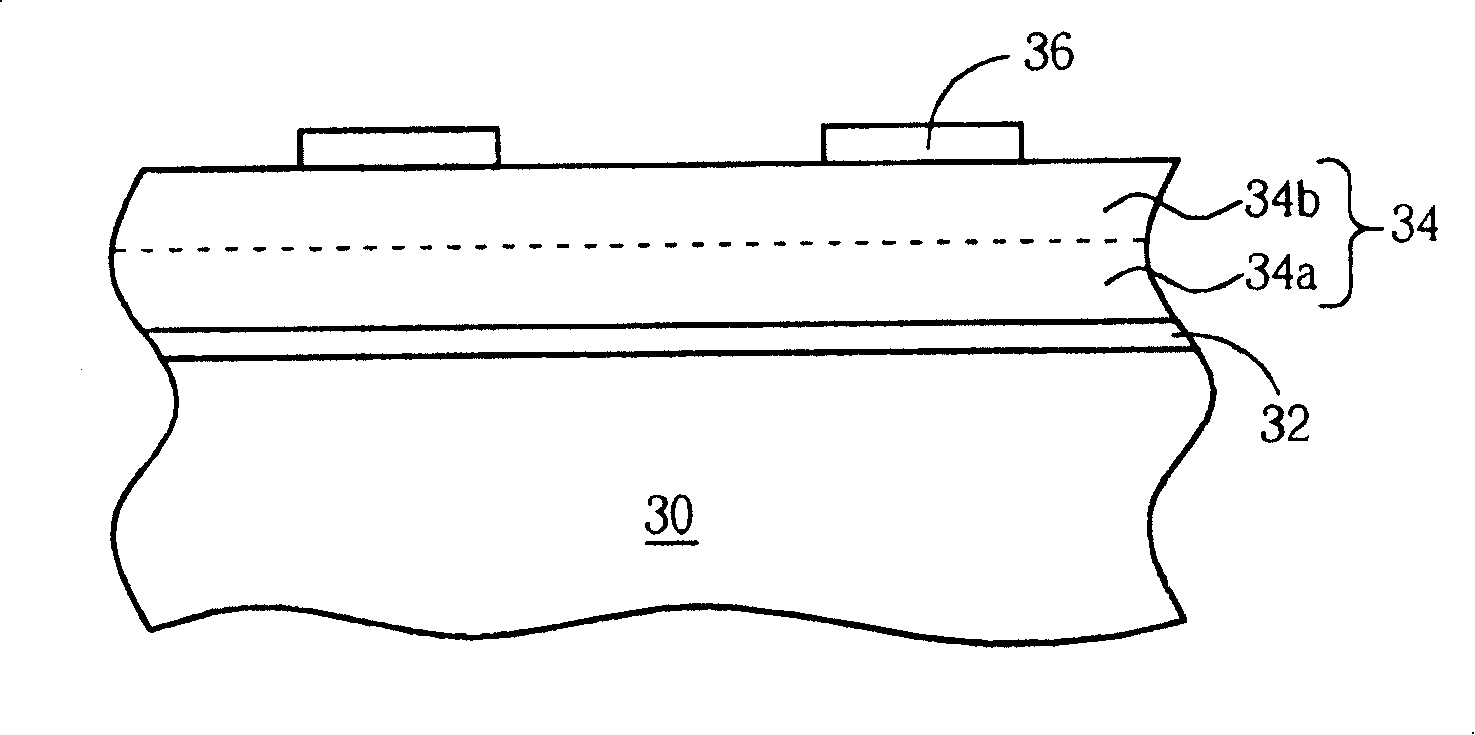

[0026] Please refer to Figure 5 to Figure 8 , Figure 5 to Figure 8 A method of defining a polysilicon pattern for the present invention. like Figure 5 As shown, the present invention provides a substrate 50, such as a silicon substrate, and then sequentially forms a gate oxide layer 52, a polysilicon layer 54, and a patterned photoresist masking layer 60 on the substrate 50, such as photoresist resist layer. In addition, the present invention needs to form a hard mask layer 56 between the photoresist mask layer 60 and the polysilicon layer 54, and optionally uses a bottom anti-reflection layer 58 and / or other material layers to form a composite The shielding material layer, and the composite shielding material layer including the hard masking layer 56 and the bottom anti-reflection layer 58 have been patterned to define a plurality of cavities on the surface of the polysilicon layer 54 .

[0027] The polysilicon layer 54 includes different regions (not shown) used to de...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com