Seal ring structure, semiconductor wafer, and method for reducing stress effect due to cutting

A sealing ring, semiconductor technology, used in semiconductor devices, semiconductor/solid-state device manufacturing, semiconductor/solid-state device components and other directions

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0044] In order to make the above and other objects, features and advantages of the present invention more comprehensible, a preferred embodiment is specifically cited below, together with the accompanying drawings, and is described in detail as follows:

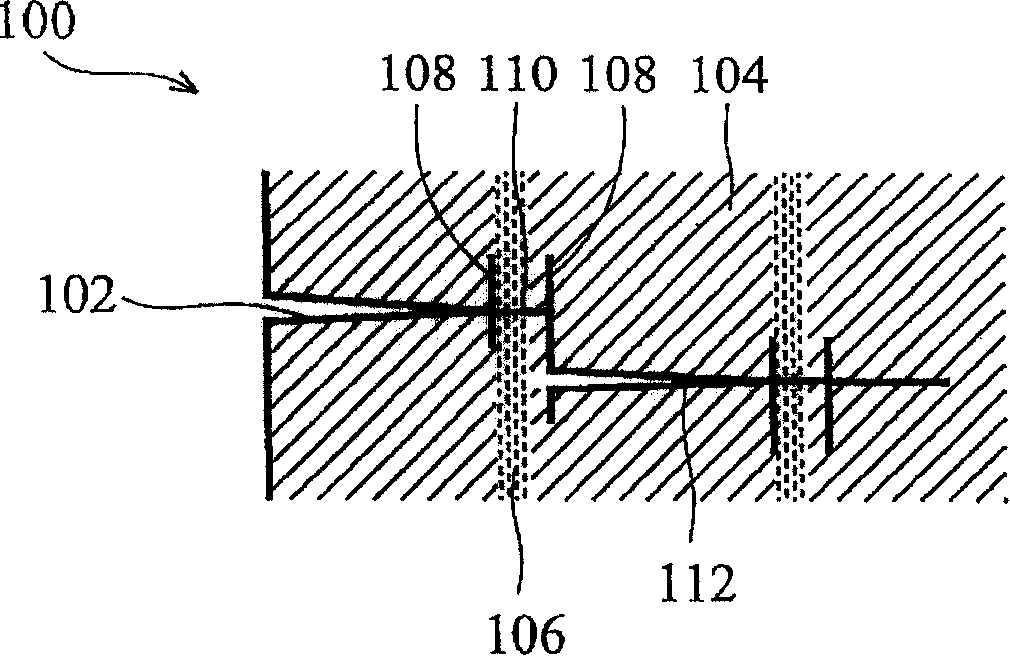

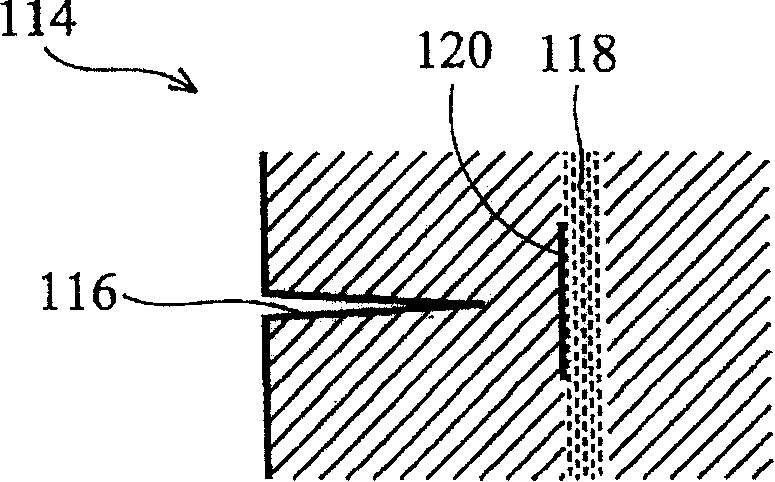

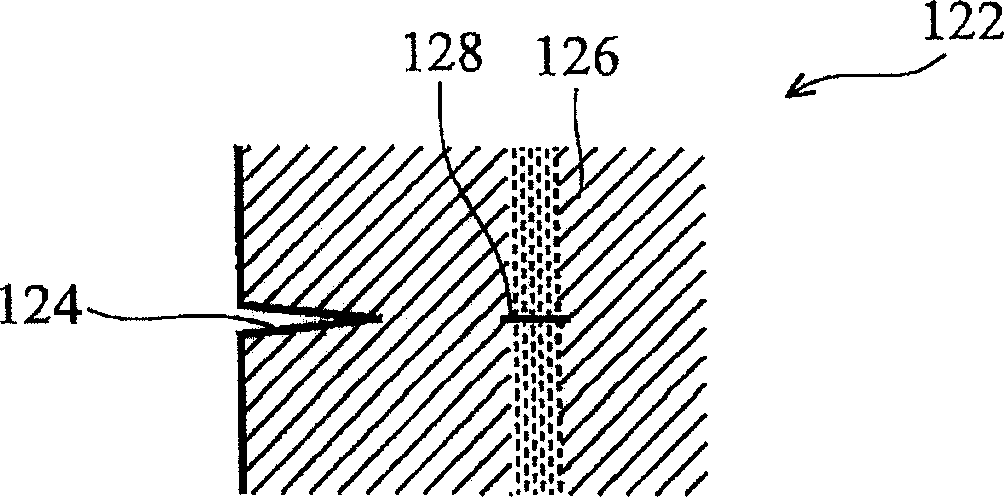

[0045]The invention discloses a sealing ring structure, which has strong physical strength and includes multiple metallization layers, which can preferably limit and prevent the advancement of cracks. The sealing ring structure is in a region between a core circuit and the edge of an integrated circuit chip and has a thick structure. This structure is a stack formed by upper bridges and lower bridges. Can provide greater mass and strength for improved resistance to crack intrusion.

[0046] A common failure situation that an integrated circuit chip may encounter is the generation and propagation of stress cracks from the edge of the integrated circuit chip. Such a failure can be achieved by Figure 1A This is caused by th...

PUM

| Property | Measurement | Unit |

|---|---|---|

| width | aaaaa | aaaaa |

| width | aaaaa | aaaaa |

| width | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com