Method for generating a structure on a substrate

一种基板、氮化层的技术,应用在电气元件、半导体/固态器件制造、电路等方向,能够解决艰难具有可能性、无法达到栅极长度、短栅极结构不可能等问题

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

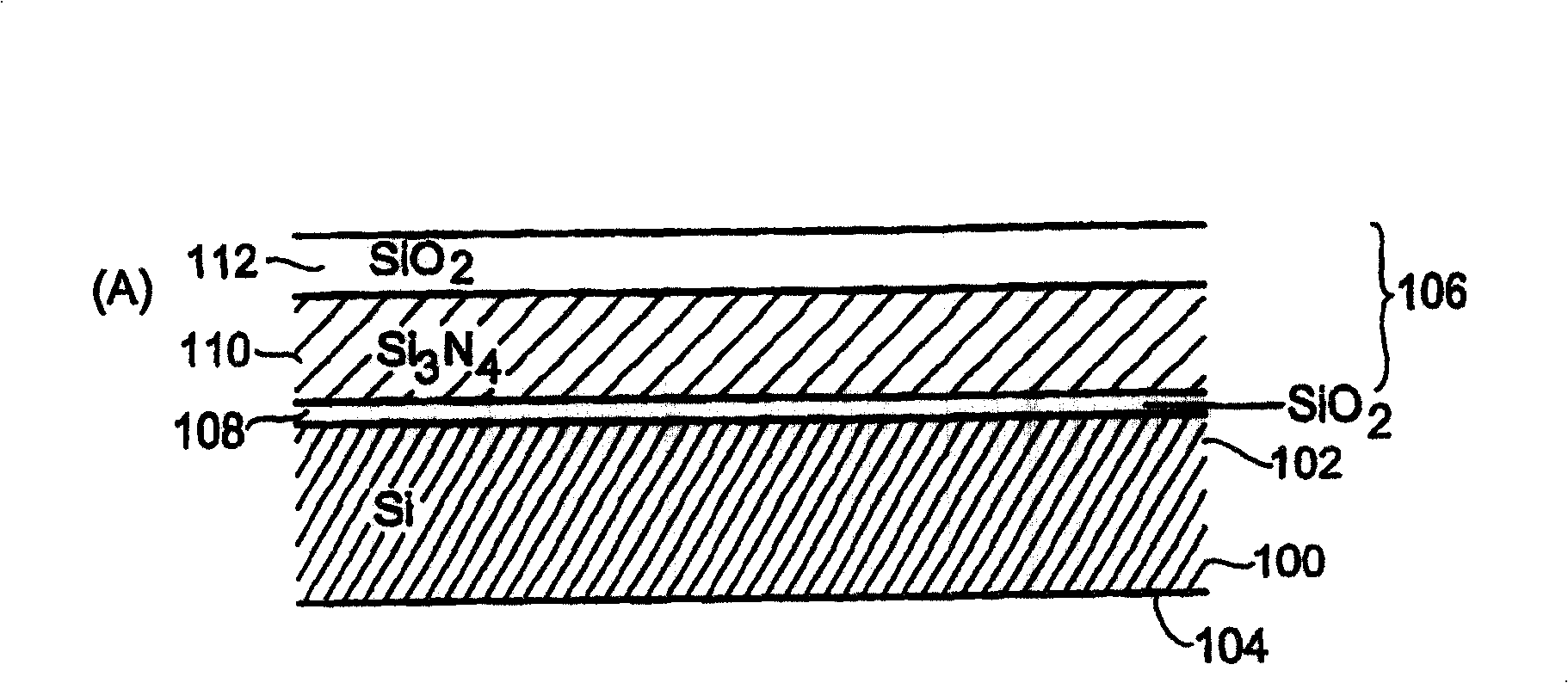

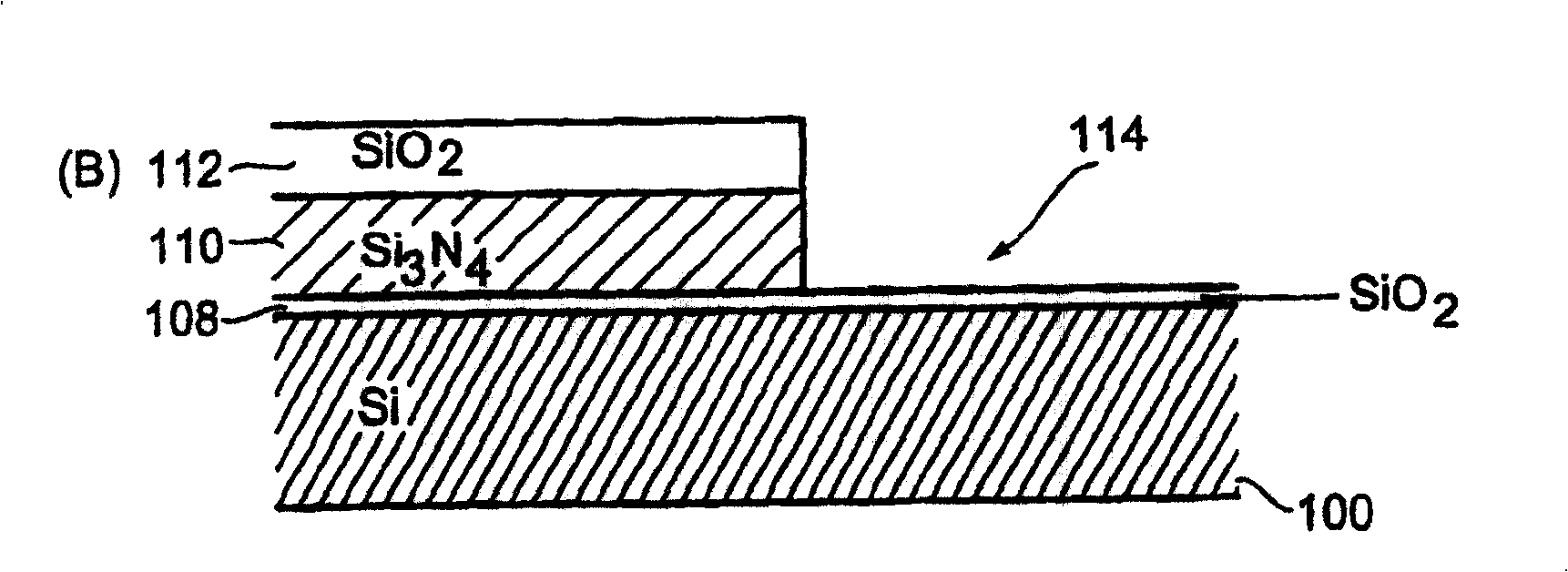

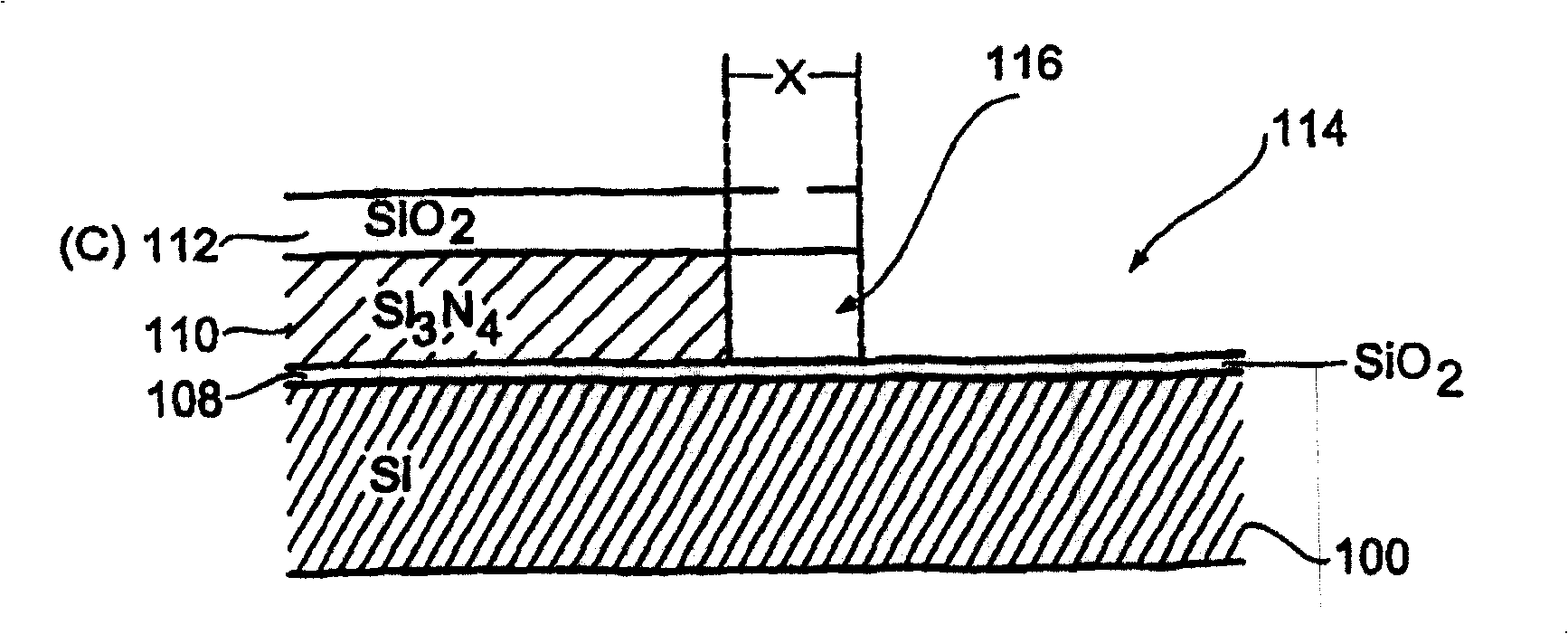

[0021] Now, referring to Fig. 1, a first preferred embodiment of the present invention will be explained in more detail, wherein, using Figure 1A to Figure 1K , the different program steps according to this preferred embodiment will be explained in more detail.

[0022] exist Figure 1A In, a semiconductor structure is illustrated, which includes a substrate 100 having a first major surface 102 and a second major surface 104, and in the illustrated embodiment is a silicon substrate On the first major surface 102 of the substrate 100, a layer sequence 106 is produced, including a first oxide layer 108 disposed on the substrate 100, a first oxide layer 108 disposed on the first oxide layer 108 Nitride layer 110, and a second oxide layer 112 disposed on the nitride layer 110, moreover, in the illustrated embodiment, these oxide layers 108 and 112 are silicon dioxide layers, and The nitride layer 110 is a silicon nitride layer, and, in Figure 1A The silicon oxide / silicon nitri...

PUM

| Property | Measurement | Unit |

|---|---|---|

| etching rate | aaaaa | aaaaa |

| length | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More