A kind of power semiconductor device and its manufacturing method

A technology for power semiconductors and semiconductors, applied in the manufacture of semiconductor/solid-state devices, semiconductor devices, electrical components, etc., can solve the problems of increasing on-resistance, limiting the performance of the split gate VDMOS, limiting the value of the device, etc., to reduce the electric field strength, Optimized switching performance, effect of small gate length

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

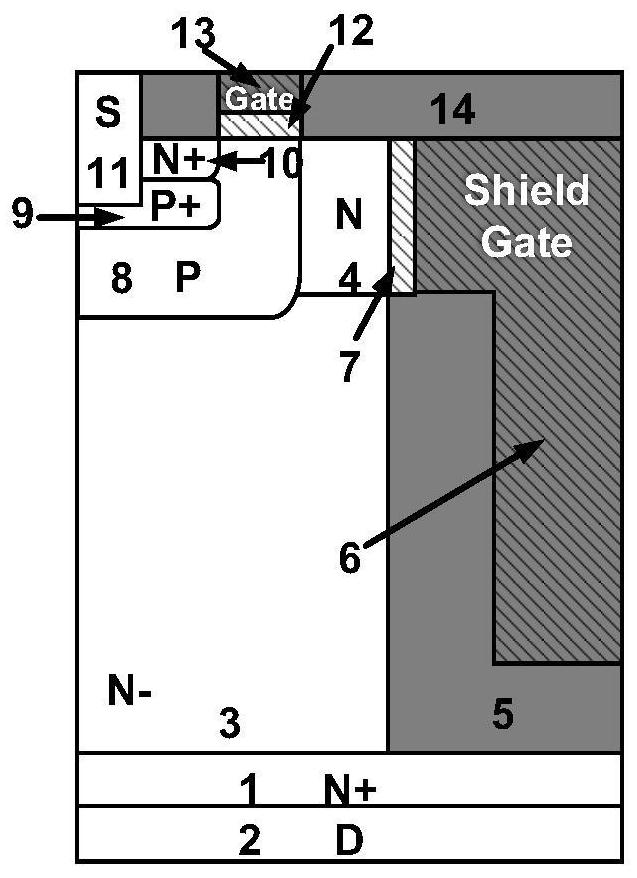

[0041] Such as figure 2As shown, a power semiconductor device includes a first conductivity type semiconductor substrate 1, the bottom of the first conductivity type semiconductor substrate 1 is connected to the drain electrode 2; the upper part of the first conductivity type semiconductor substrate 1 has a first Conductive type semiconductor epitaxial layer 3; the first conductive type semiconductor epitaxial layer 3 has a dielectric groove 5, and the dielectric groove 5 has an isolation gate 6; the upper part of the first conductive type semiconductor epitaxial layer 3 has a second conductive type semiconductor body Region 8, the second conductivity type semiconductor body region 8 has a second conductivity type semiconductor body contact region 9 and a first conductivity type semiconductor source region 10; the second conductivity type semiconductor body contact region 9 and the first conductivity type The semiconductor source regions 10 are all connected to the source ele...

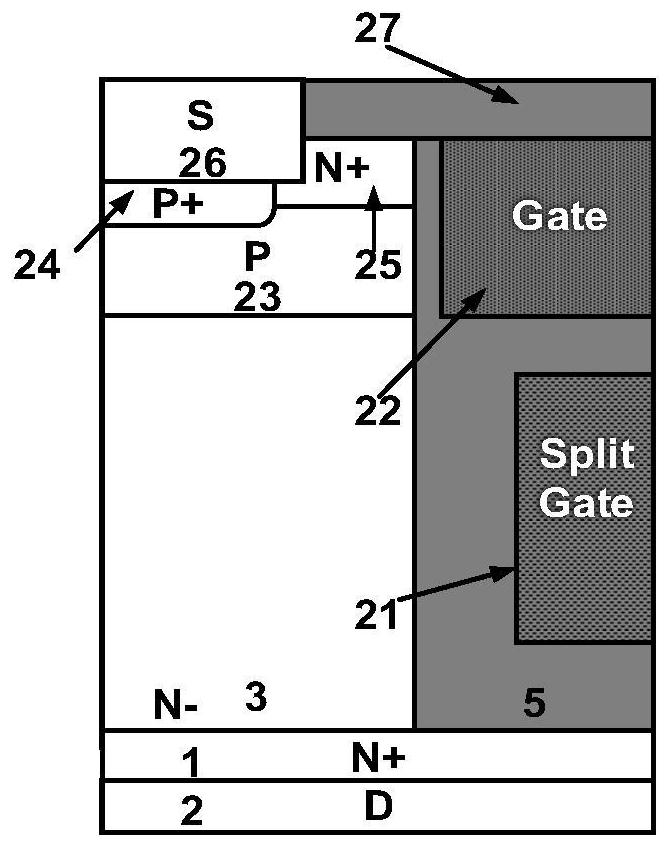

Embodiment 2

[0065] The difference between this embodiment and Embodiment 1 is that the potential of the isolation barrier 6 is not grounded, but connected to a specific potential, which can be provided by other parts of the circuit. All the other structures are the same as in Example 1.

[0066] According to the common knowledge in this field, it can be known that connecting a specific voltage can modulate the electric field distribution in the body, increase the breakdown voltage, and reduce the on-resistance, or connect a point voltage signal or other dynamic voltage that changes synchronously with the gate voltage, which can further increase the switching speed or ratio on-resistance for better device performance.

Embodiment 3

[0068] Such as Figure 4 As shown, the difference between this embodiment and Embodiment 1 is that the medium in the dielectric tank 5 adopts a multilayer variable permittivity structure, including a first dielectric layer 15 with a dielectric constant of K1 and a first dielectric layer 15 with a dielectric constant of K2. Two dielectric layers 16 . All the other structures are the same as in Example 1. In this embodiment, the dielectric constants of the first dielectric layer 15 and the second dielectric layer 16 are optimized, so as to modulate the electric field in the device and introduce a new electric field peak, which can effectively increase the breakdown voltage of the device and further improve the device's performance. The excellent values of breakdown voltage and on-resistance improve the overall performance of the device.

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More