Patents

Literature

41results about How to "Reduce read errors" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

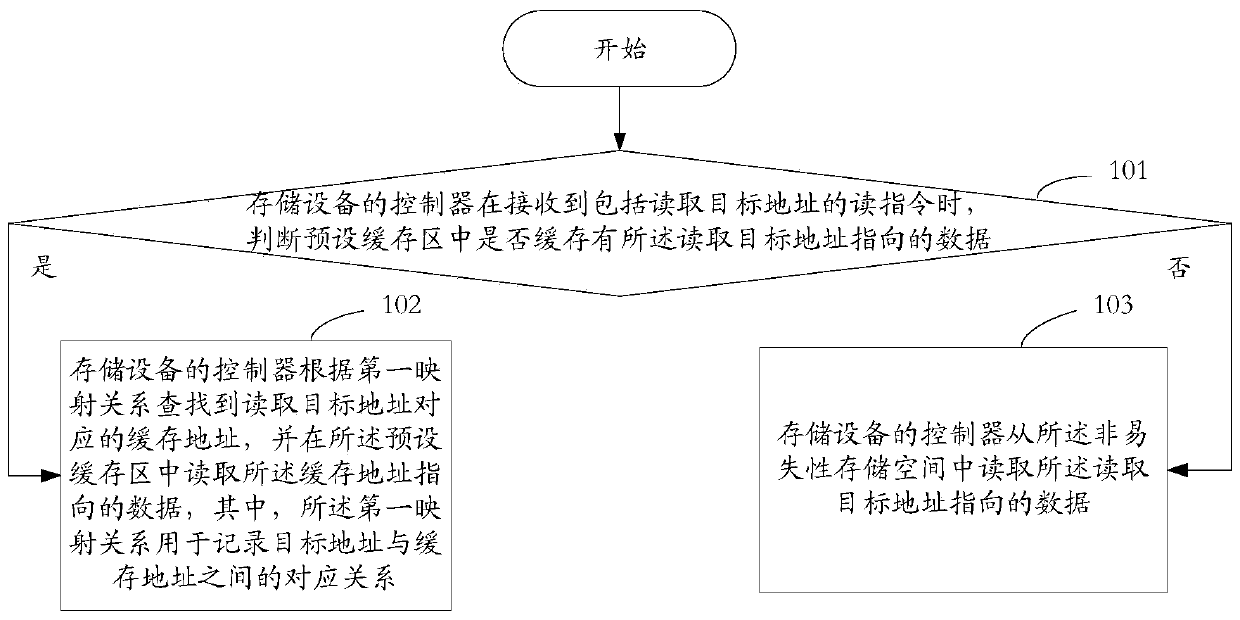

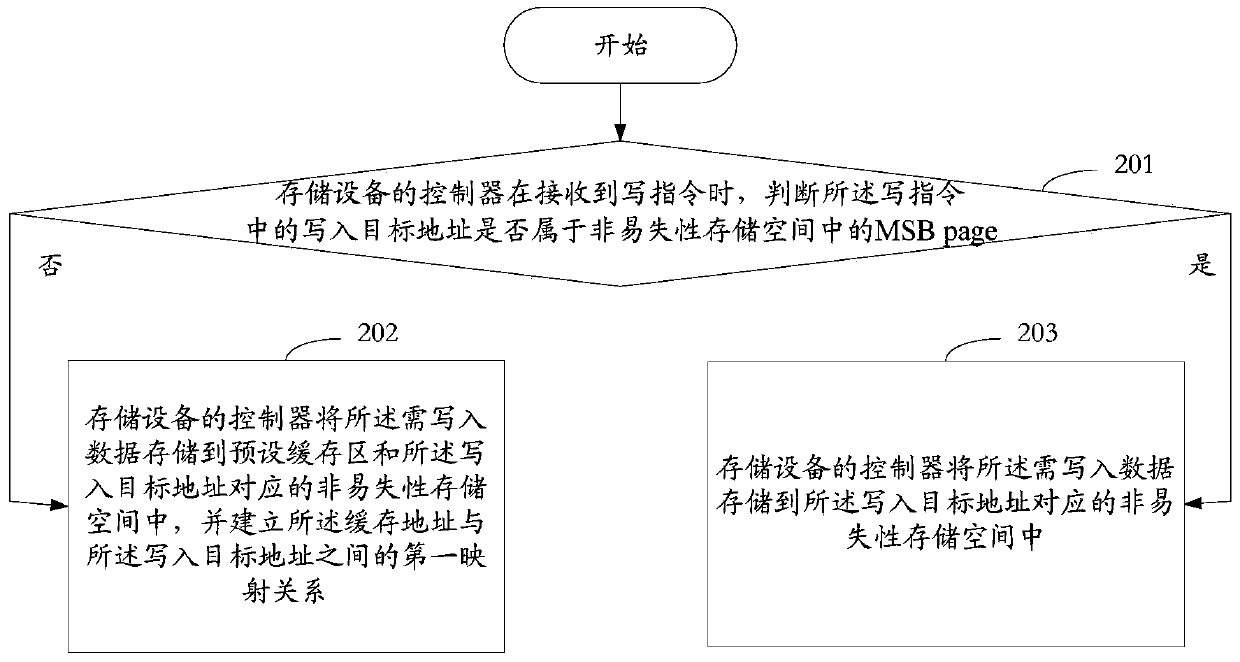

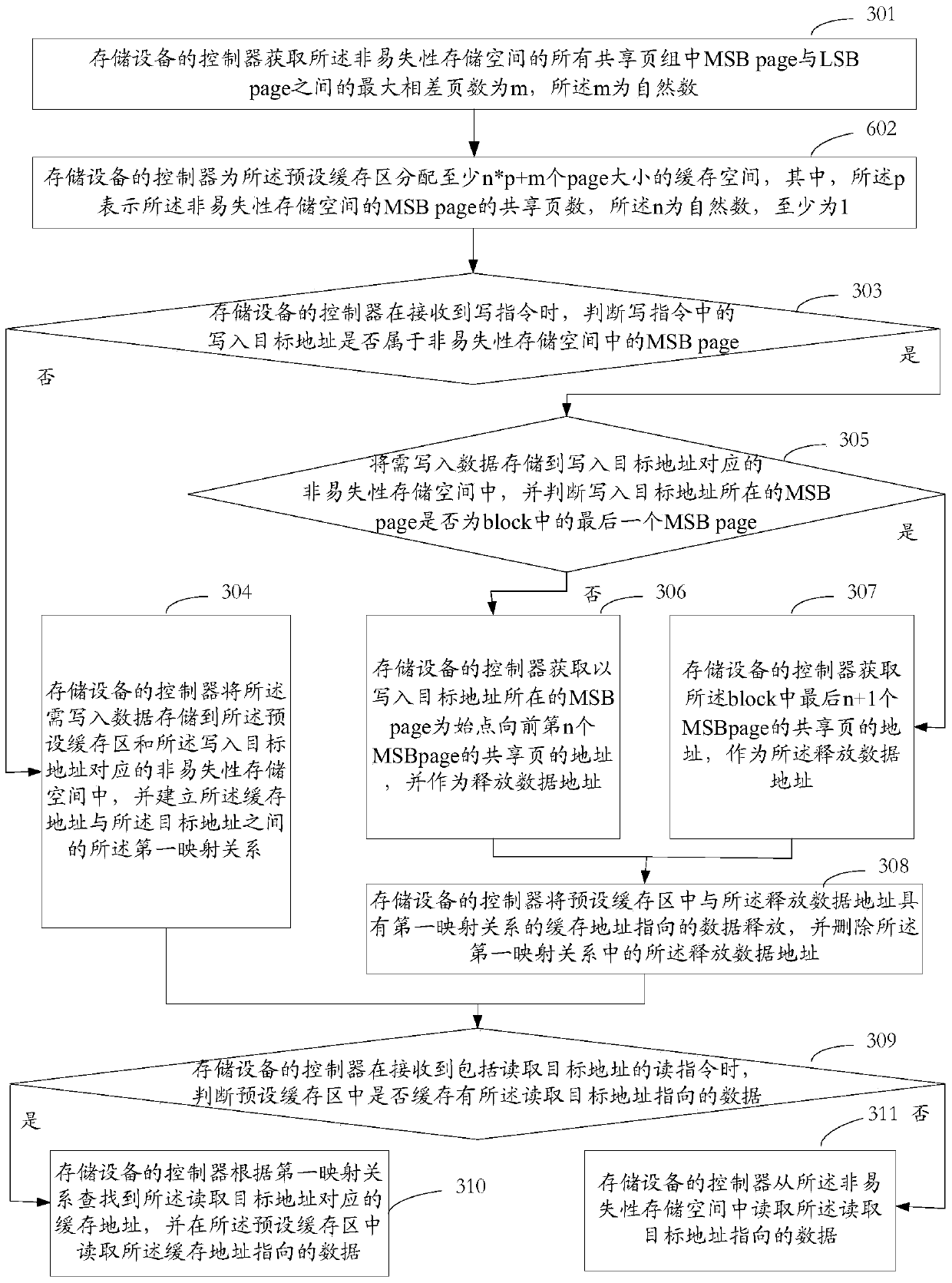

Method and device for reading data

ActiveCN104503707AImprove reliabilityReduce read errorsMemory architecture accessing/allocationInput/output to record carriersData errorOperating system

Owner:HUAWEI TECH CO LTD

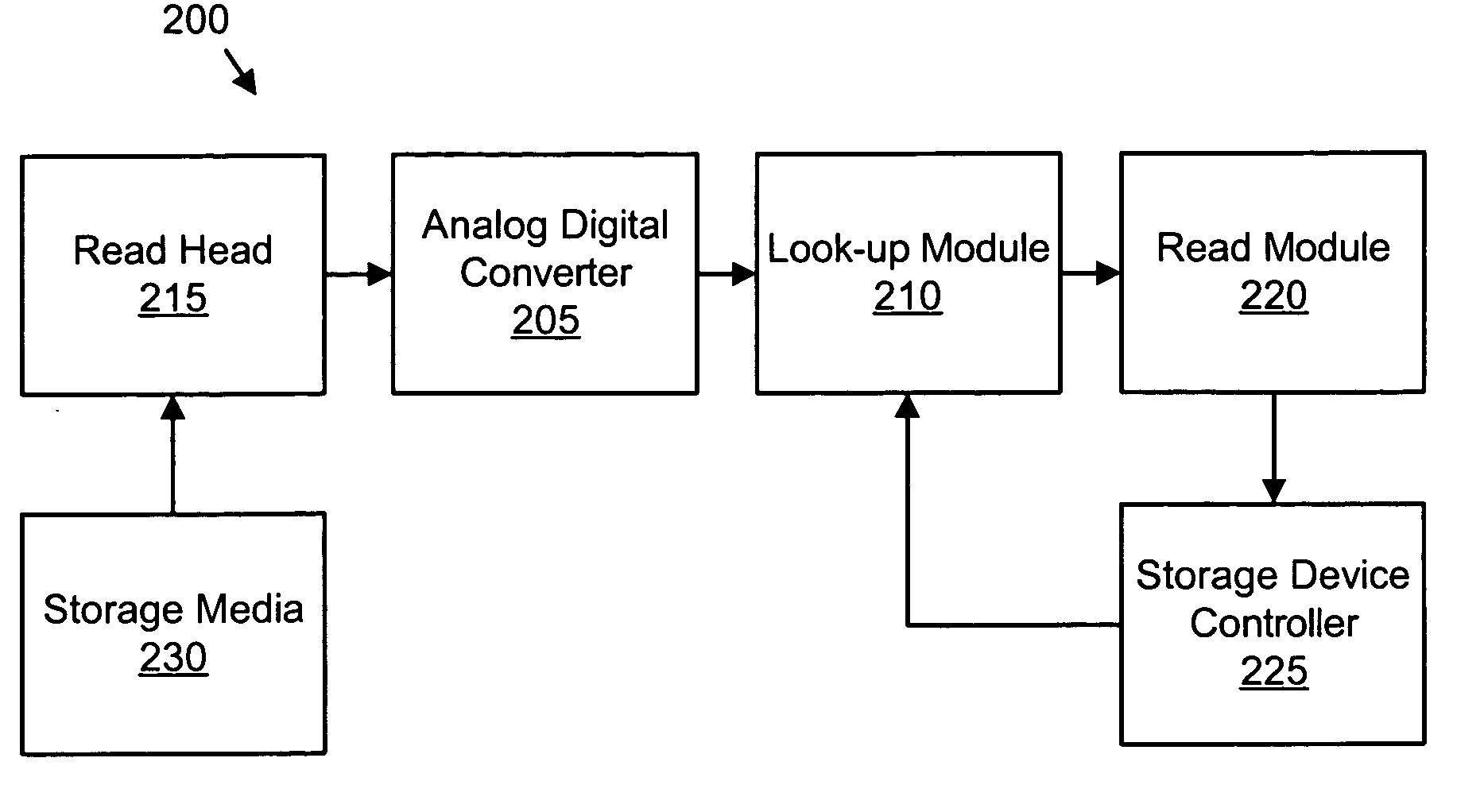

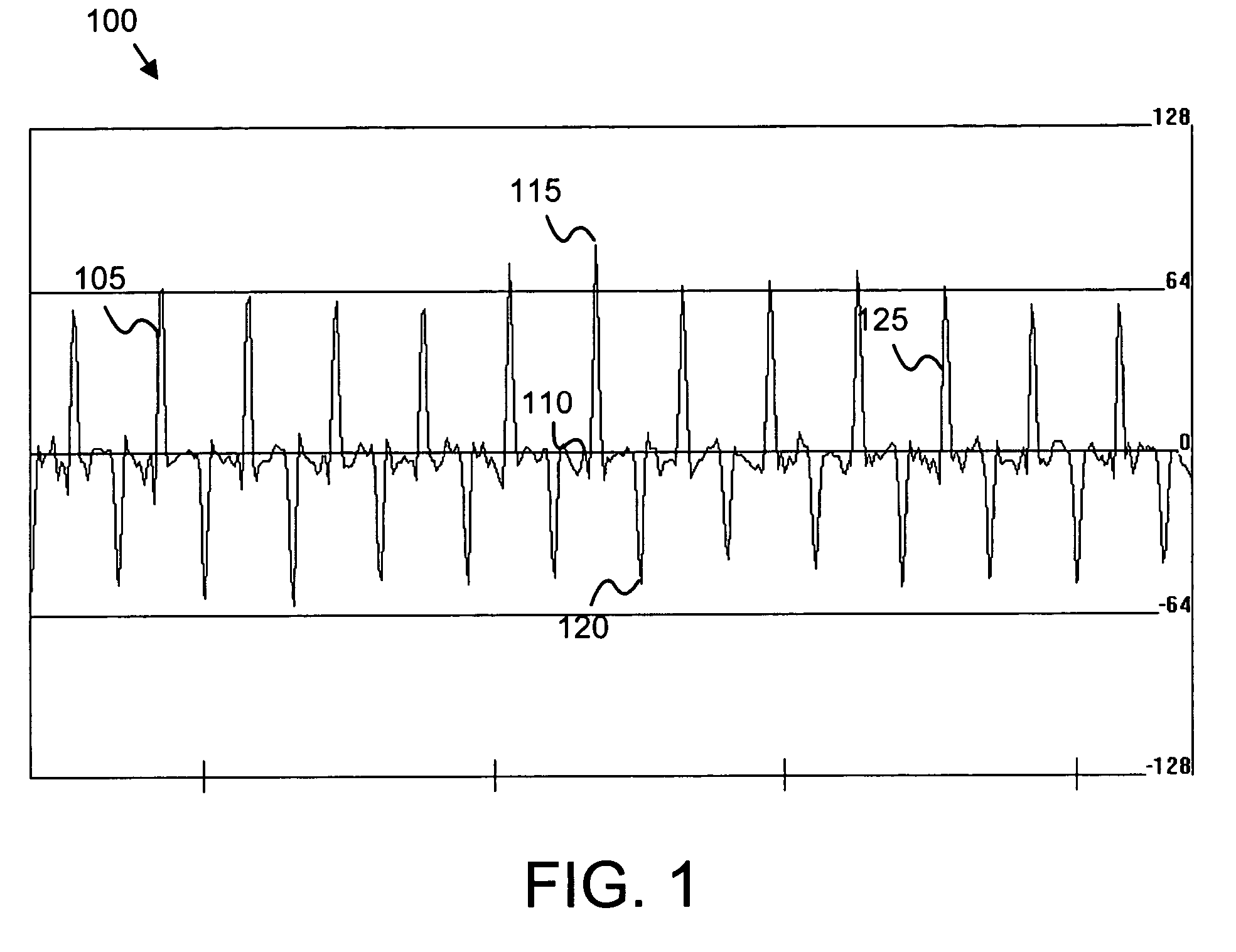

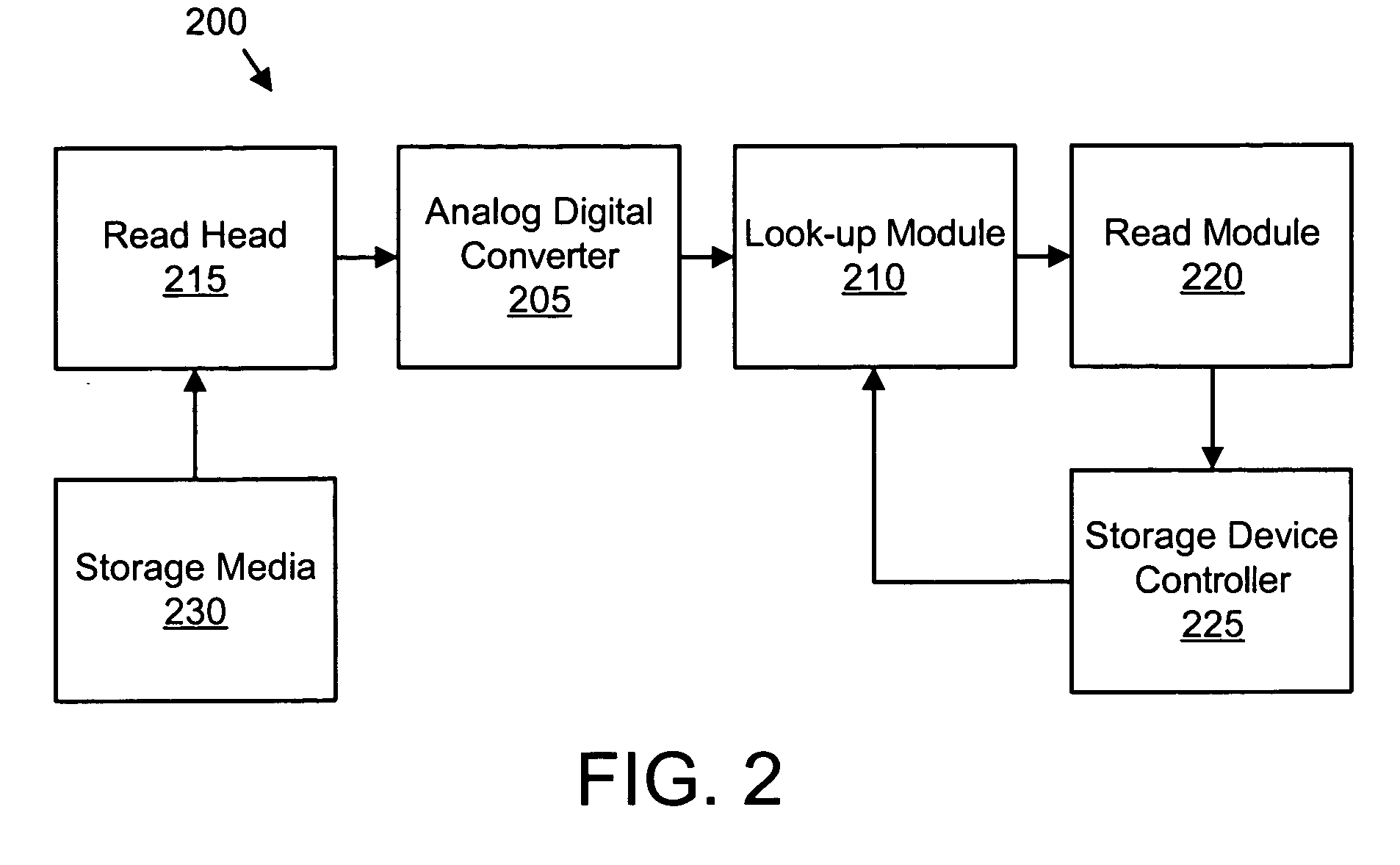

Apparatus, system, and method for mitigating signal asymmetry

InactiveUS20060082915A1Reduce read errorsReduce asymmetryAnalogue/digital conversionDriving/moving recording headsEngineeringAnalog signal

An apparatus, system, and method are disclosed for mitigating signal asymmetry. An analog to digital converter samples an analog signal from a read head and converts the sample to a digital input signal. The digital input signal addresses a look-up module, and the look-up module outputs a modified digital signal. The modified digital signal value is a specified function of the digital input signal value, wherein the specified function is configured to mitigate the asymmetry of the digital input signal. The modified digital signal value may be periodically recalculated to adjust for read head wear.

Owner:IBM CORP

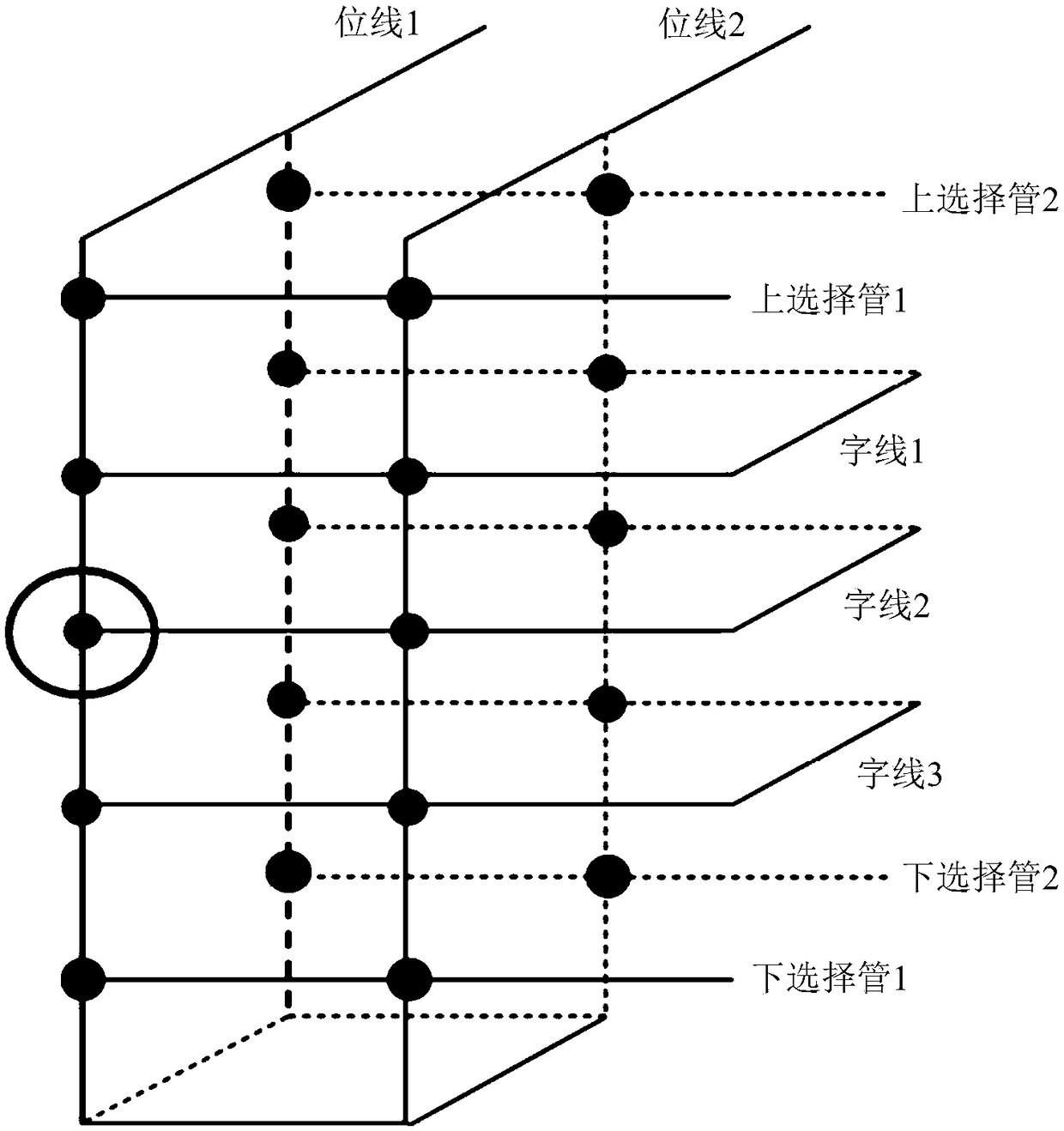

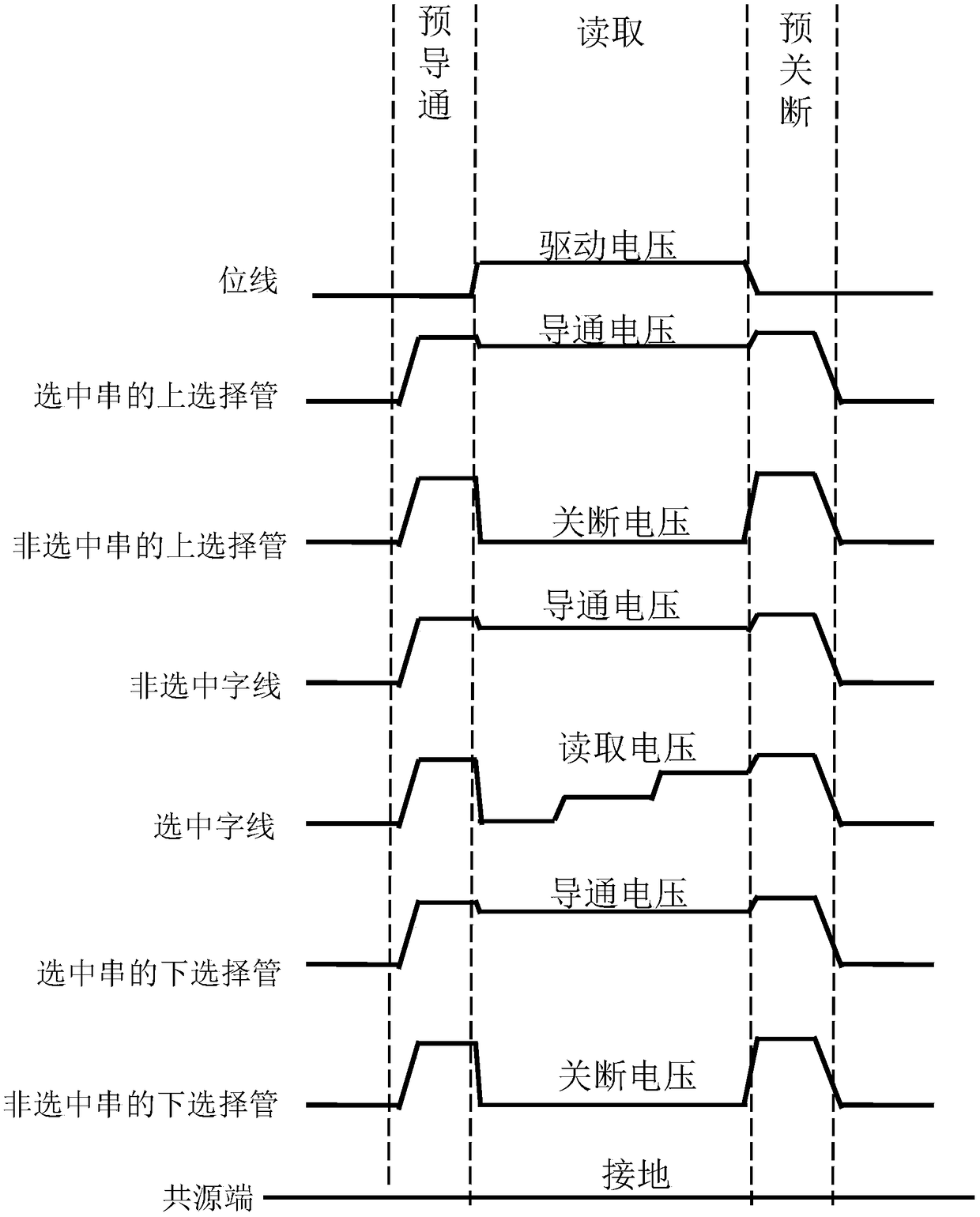

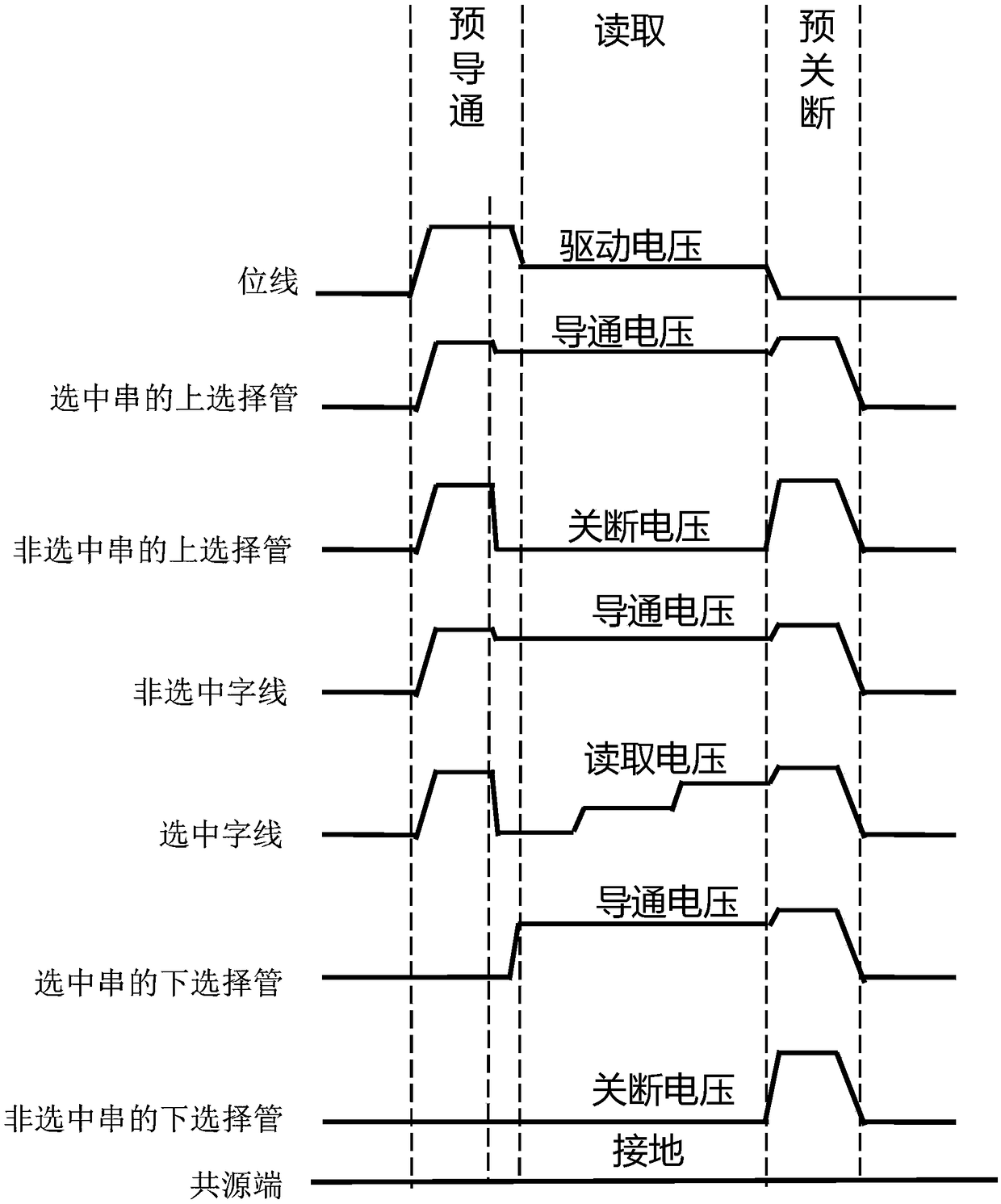

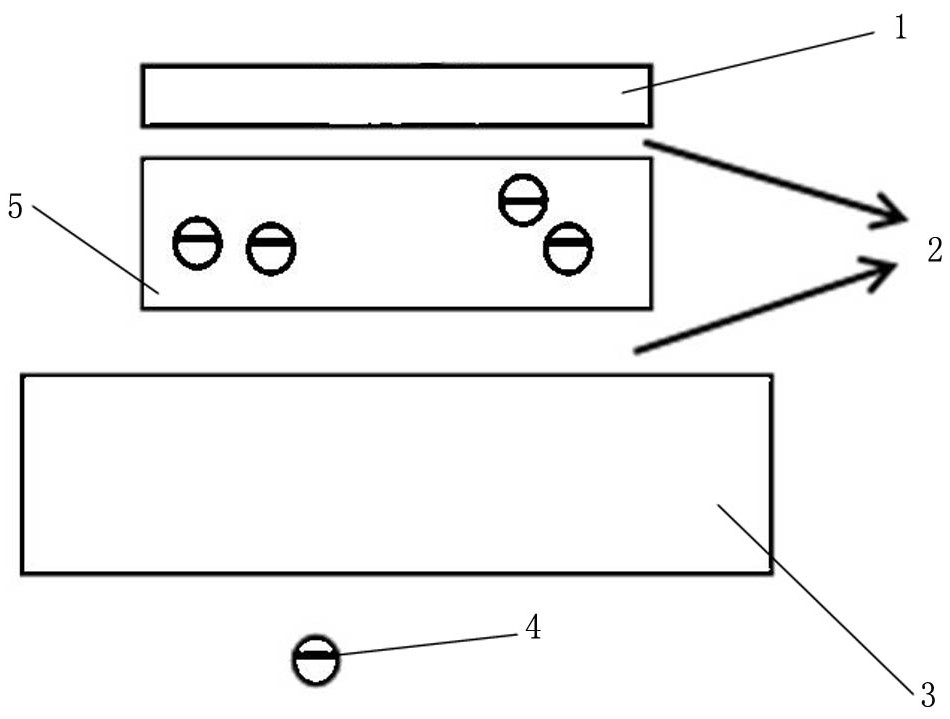

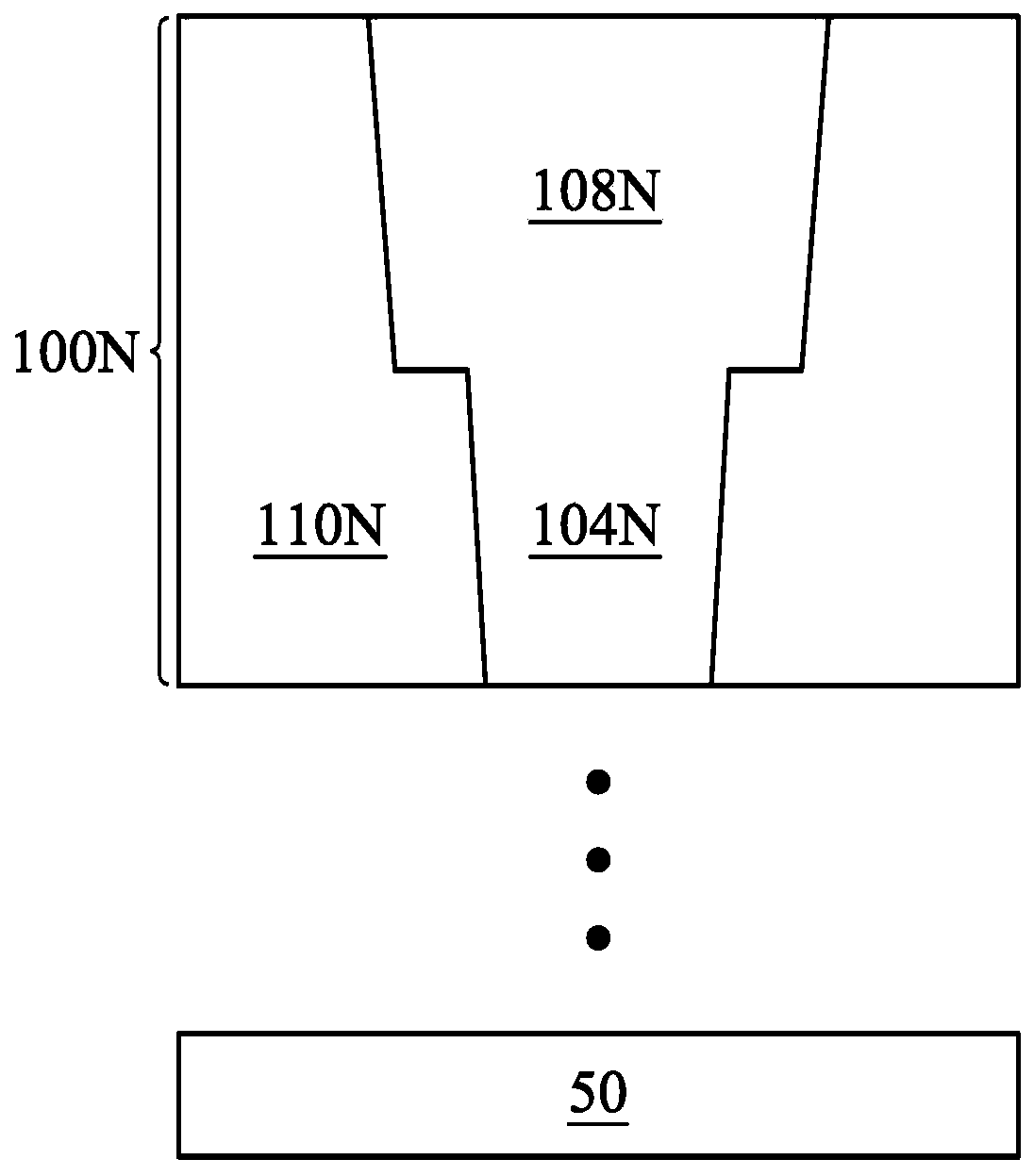

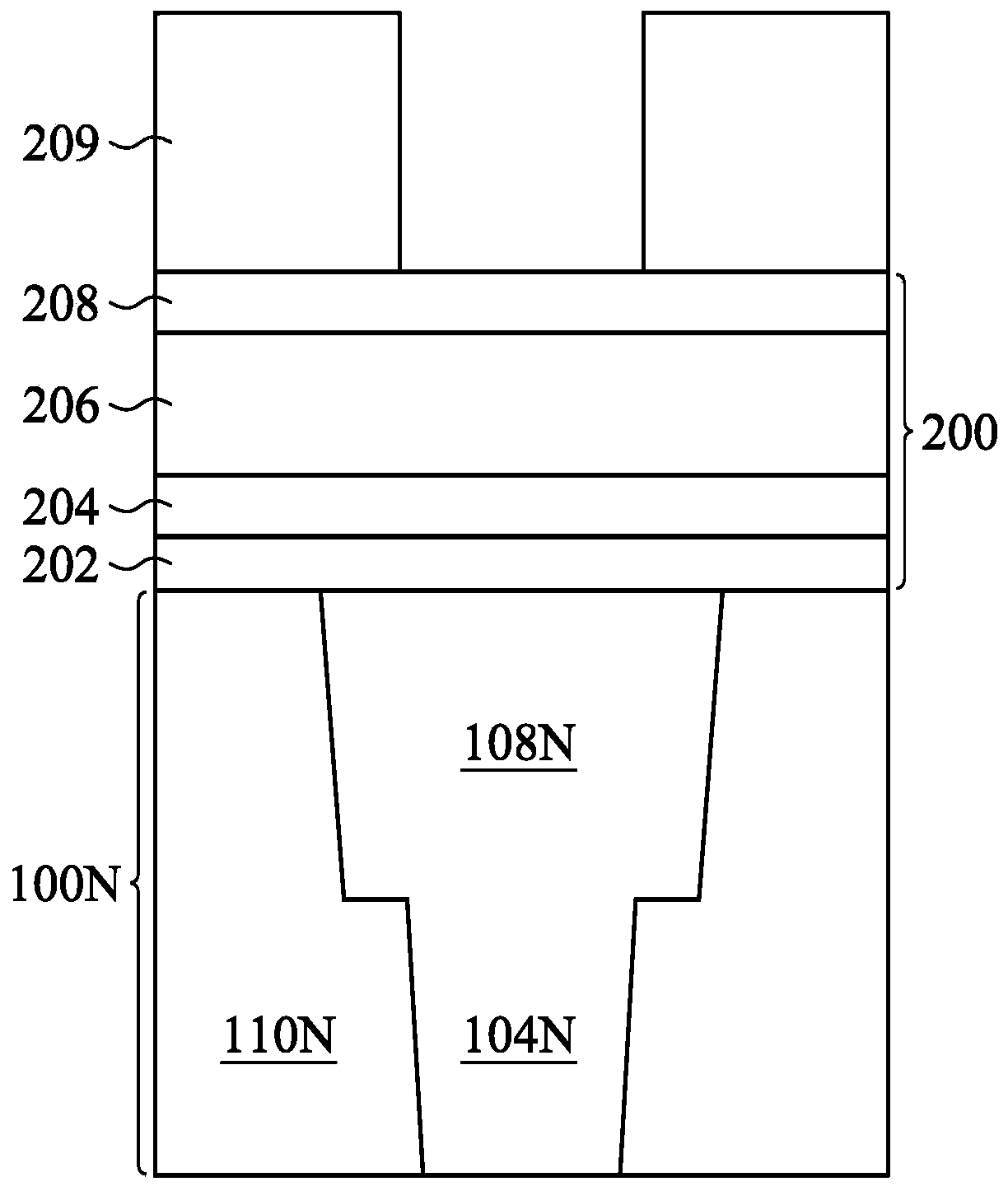

Reading method of 3D NAND flash memory

ActiveCN109065091AReduce read disturbReduce read errorsRead-only memoriesBit lineComputer architecture

The invention relates to a method for reading 3D NAND flash memory, the 3D NAND flash memory includes a plurality of memory cells arranged in an array within a three-dimensional space, forming a plurality of memory strings, the transistor at the top of each memory string is an upper select transistor, the upper selection tube is connected to a bit line, the transistor at the bottom of the string is a lower select transistor, a plurality of memory cells located within the same layer form a memory row, the gates of the memory cells located in the same memory row are all connected to the same word line, and the memory string in which the memory cells are to be read is taken as a selected string. The reading method is characterized in that the reading method comprises the steps of a preconduction stage and a reading stage, wherein a continuous precharge voltage is applied to the bit line in the preconduction stage; at the same time, the upper selection tube of the selected string and the upper selection tube of the unselected string are turned on, and the lower selection tube of the selected string and the lower selection tube of the unselected string are turned off.

Owner:YANGTZE MEMORY TECH CO LTD

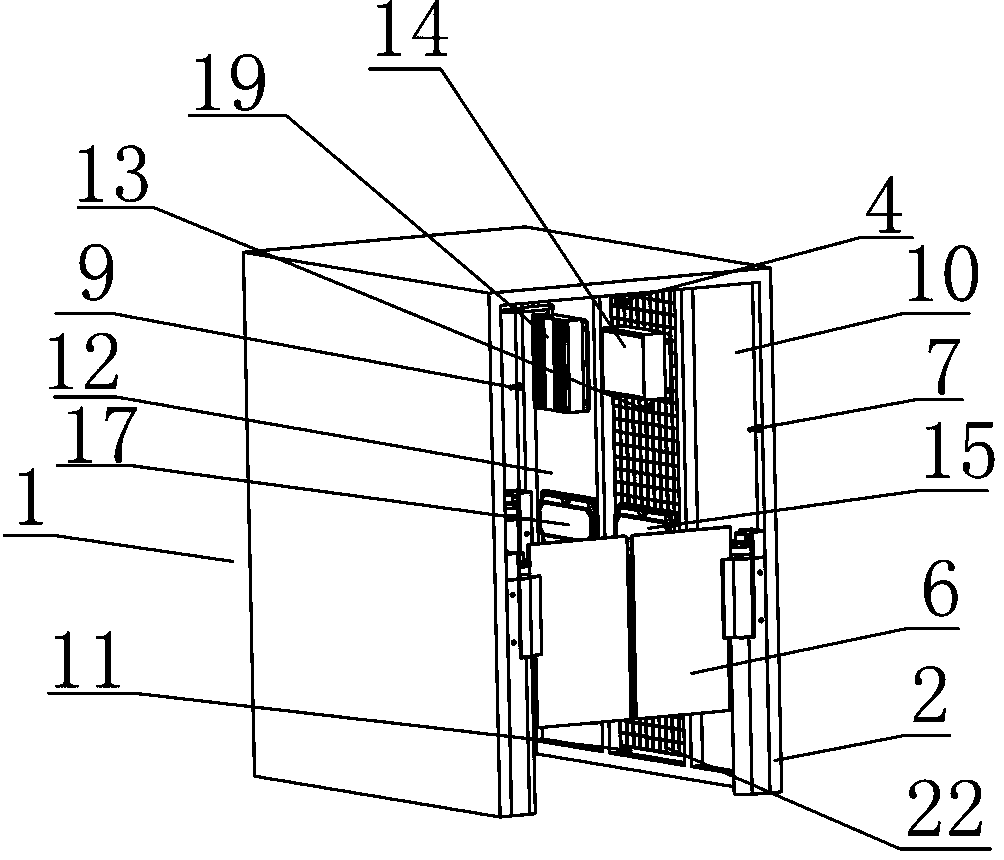

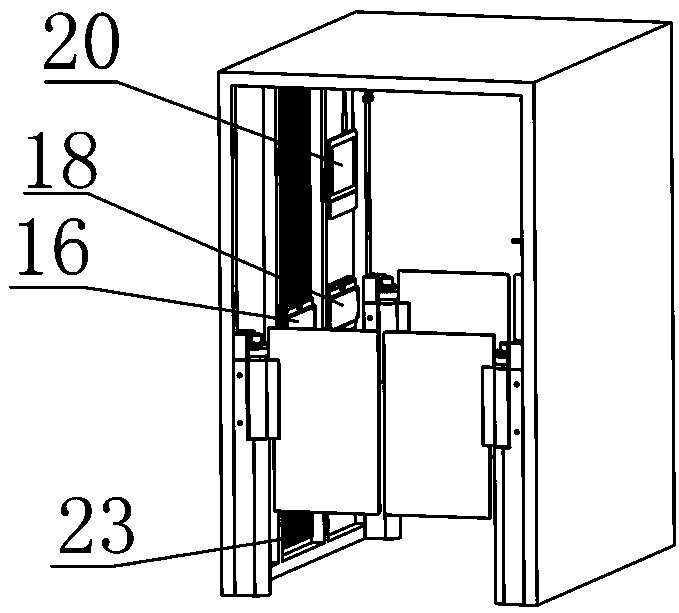

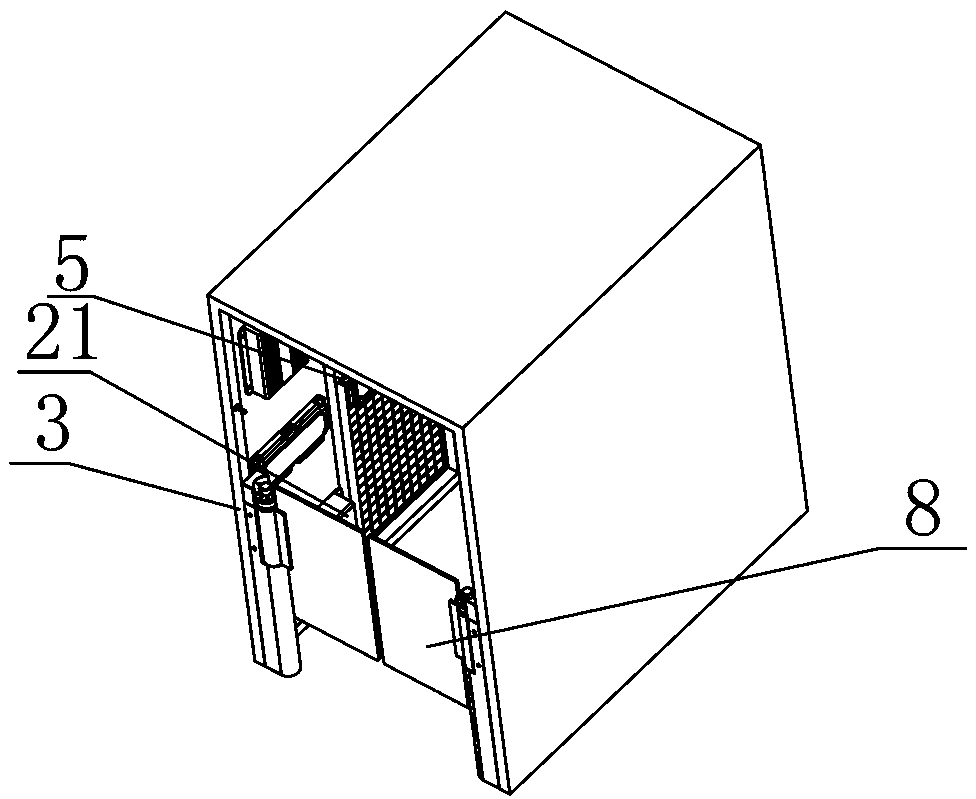

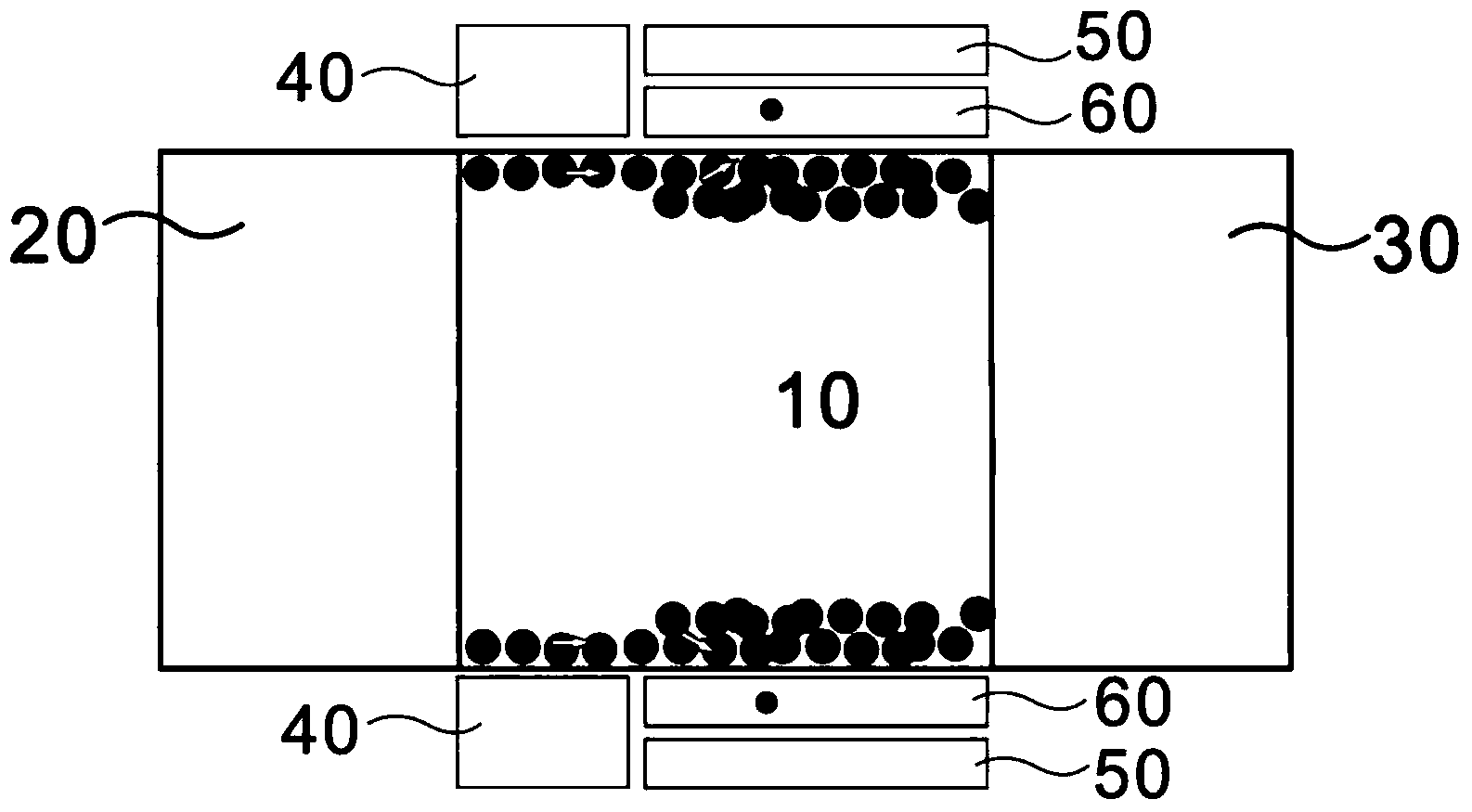

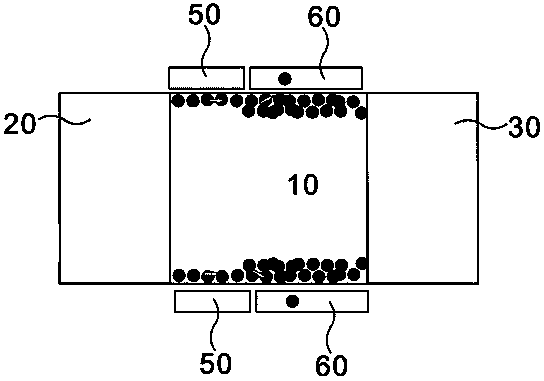

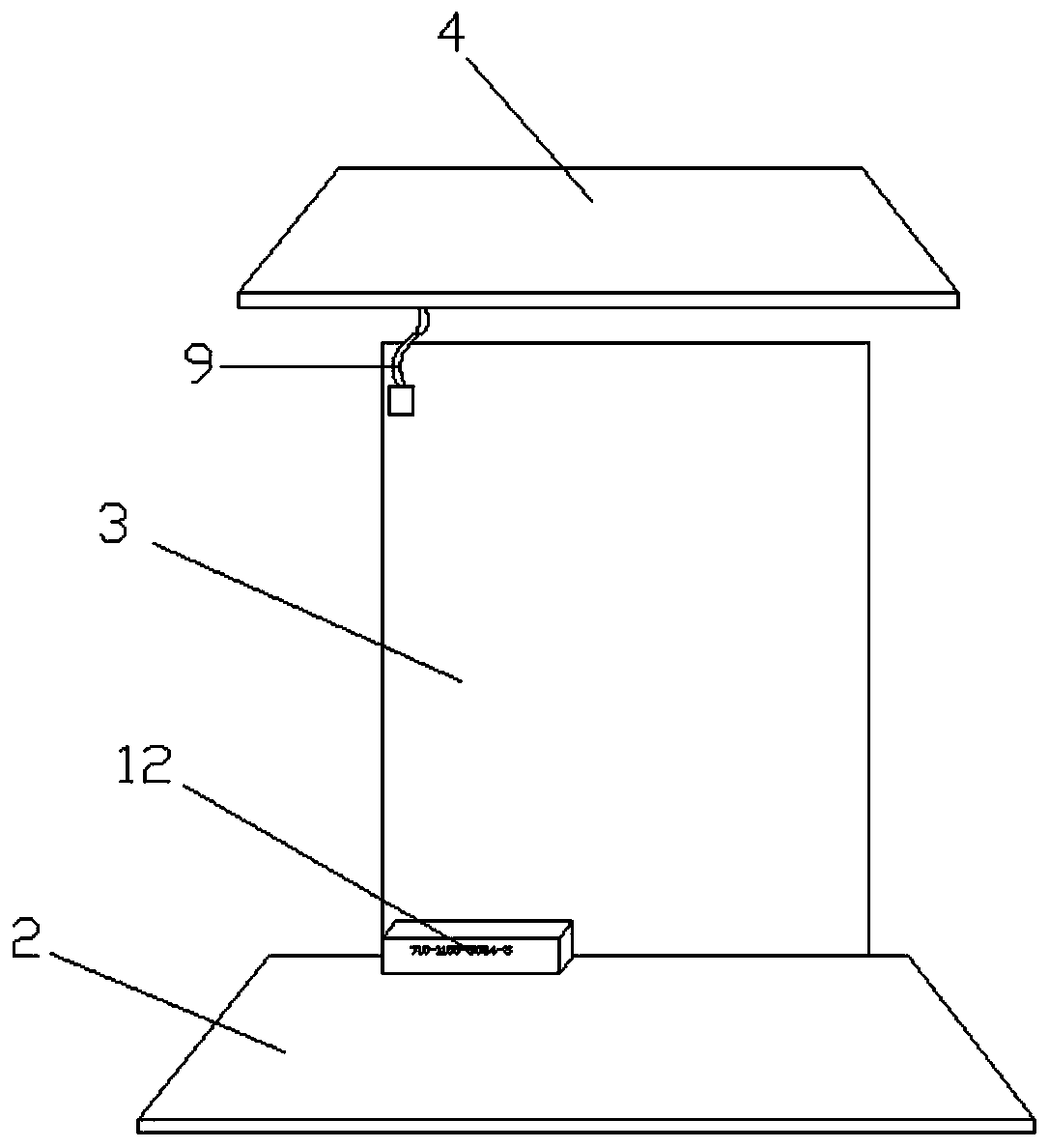

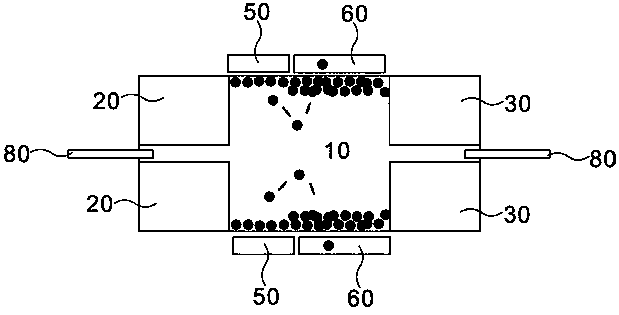

Unmanned on-duty intelligent settlement channel

PendingCN107844969AReduce read errorsReduce duplicationCash registersIndividual entry/exit registersPaymentEngineering

The invention relates to an unmanned on-duty intelligent settlement channel. The unmanned on-duty intelligent settlement channel includes channels, a front release swing gate, a back release swing gate, face identification cameras, an RFID reader-writer, a card reader, a display screen and an entrance guard device, wherein the face identification cameras include a front face identification cameraand a back face identification camera; the channel bodies of the channels include a front channel body, an intermediate channel body and a back channel body; the RFID reader-writer is arranged on theinner wall of one side plate of the intermediate channel body; the card reader and the display screen are arranged on the upper part of the inner wall of the back channel body in an opposite manner; and the entrance guard device is arranged at the lower part of the inner wall of the side plate at the same side of the card reader. The unmanned on-duty intelligent settlement channel has the advantages of being high in the settlement efficiency, being low in the labor cost, being short in the time for queuing for payment, being high in the payment speed, being good in the shopping experience, guaranteeing that no signal interference exists, greatly reducing the information reading error and repetition of information reading, and being able to realize comprehensive automatic authentication andautomatic settlement and payment.

Owner:广东优信无限网络股份有限公司

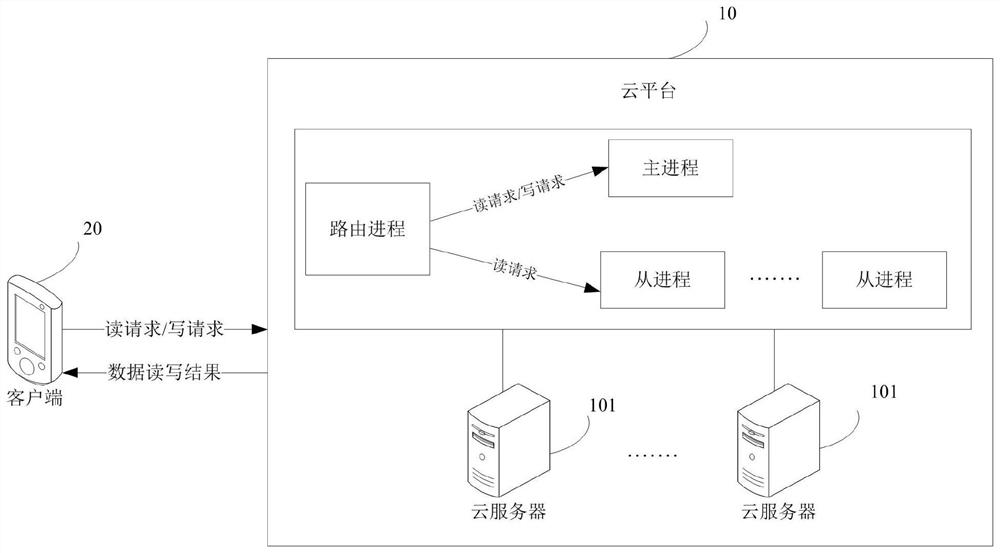

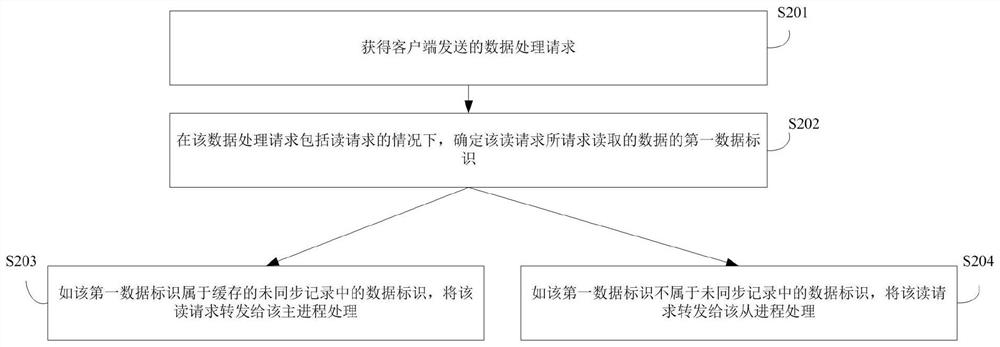

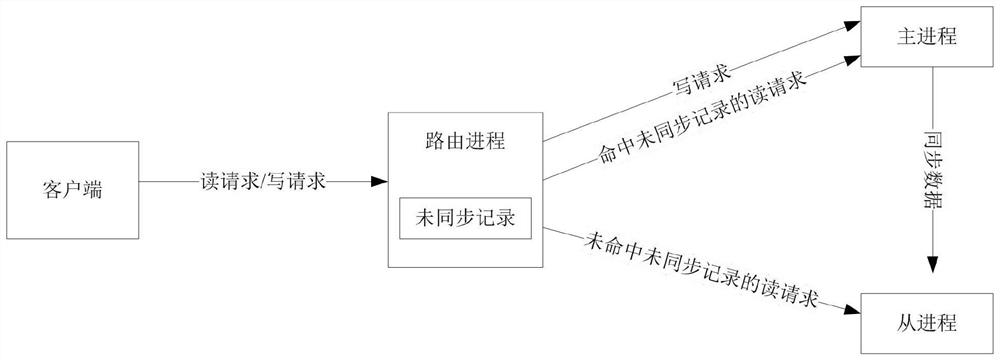

Data processing method and device, server and storage medium

PendingCN111813550AReduce read errorsReduce exceptionDigital data information retrievalResource allocationEngineeringData request

The invention discloses a data processing method and device, a server and a storage medium, the scheme of the invention is applied to a business service platform, the business service platform runs amaster process and at least one slave process. The method comprises the following steps: obtaining a data processing request sent by a client; under the condition that the data processing request comprises a reading request, determining a first data identifier of data requested to be read by the reading request; if the first data identifier belongs to a data identifier in a cached non-synchronousrecord, forwarding the read request to the master process for processing, the non-synchronous record recording a data identifier corresponding to data which is not synchronized from the master processto the slave process; and if the first data identifier does not belong to the data identifier in the non-synchronous record, forwarding the read request to the slave process for processing. Accordingto the scheme, the data request processing efficiency can be improved, Meanwhile, the situation of data reading errors or abnormalities caused by inconsistency of the master process data and the slave process data can be reduced.

Owner:深圳市腾讯网域计算机网络有限公司

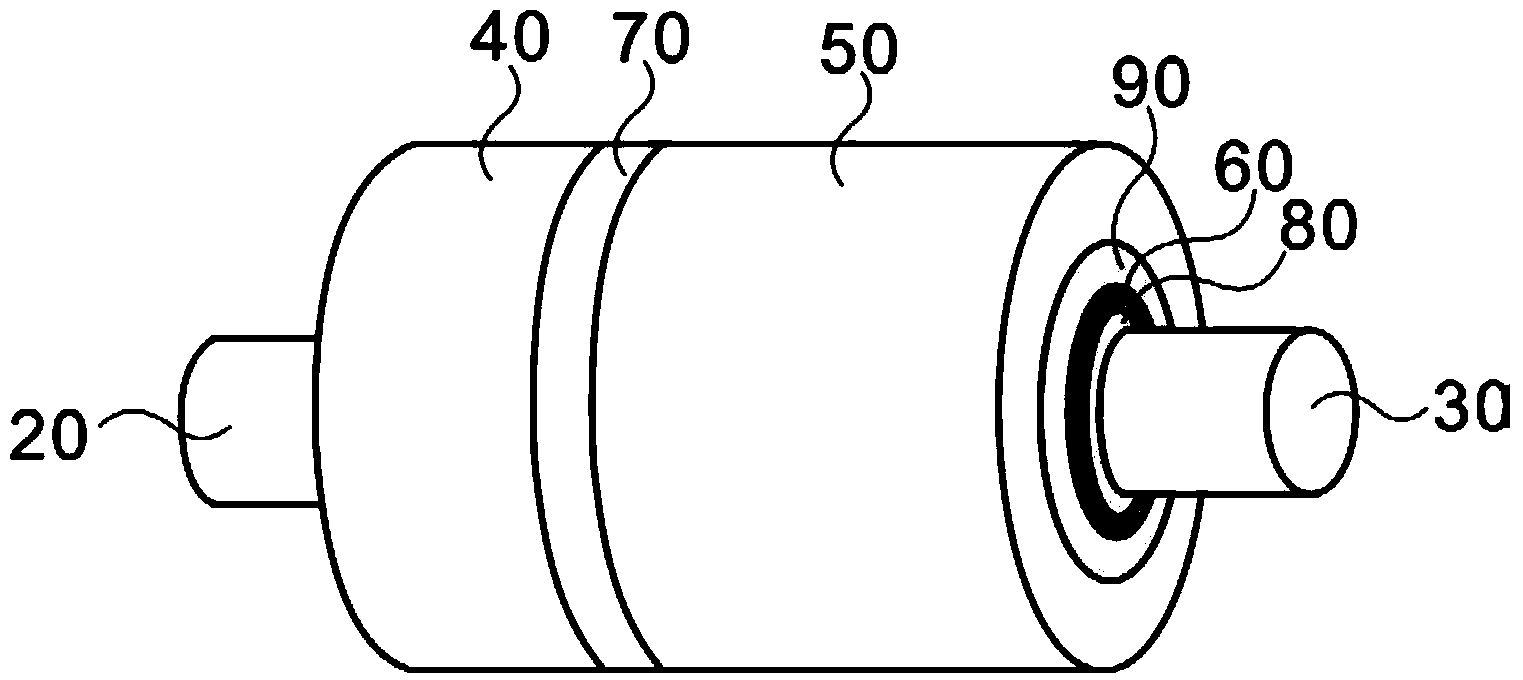

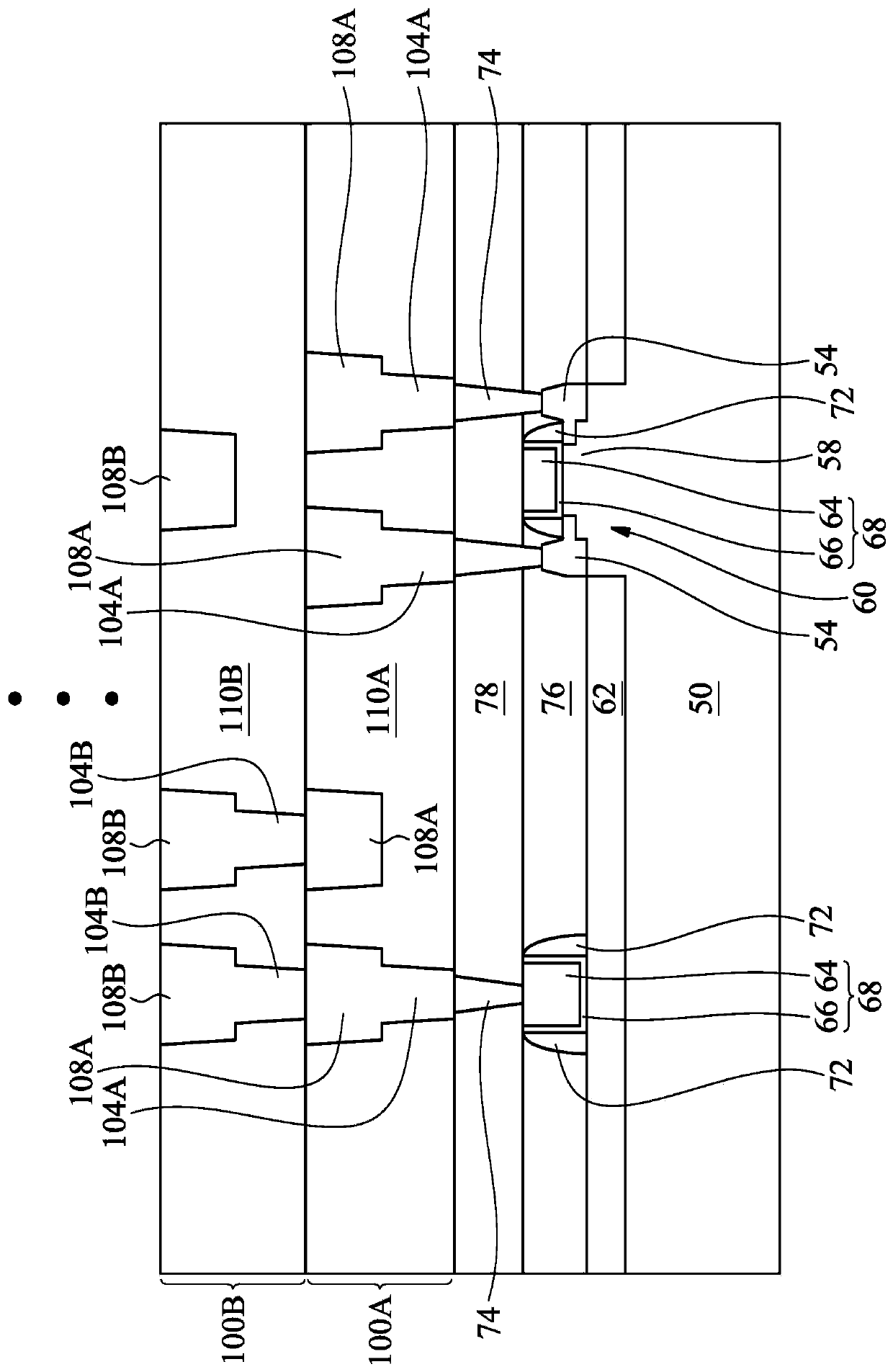

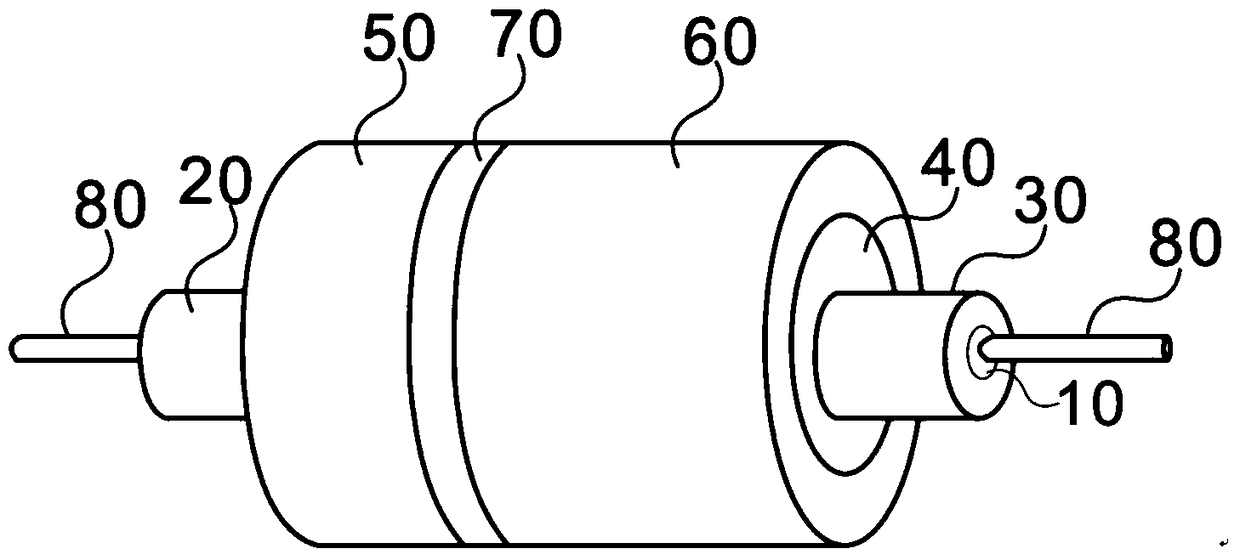

SONOS (silicon oxide nitride oxide silicon) flash memory device and compiling method thereof

ActiveCN104332471AReduce read errorsReduce critical sizeSolid-state devicesSemiconductor/solid-state device manufacturingSilicon oxideNitride

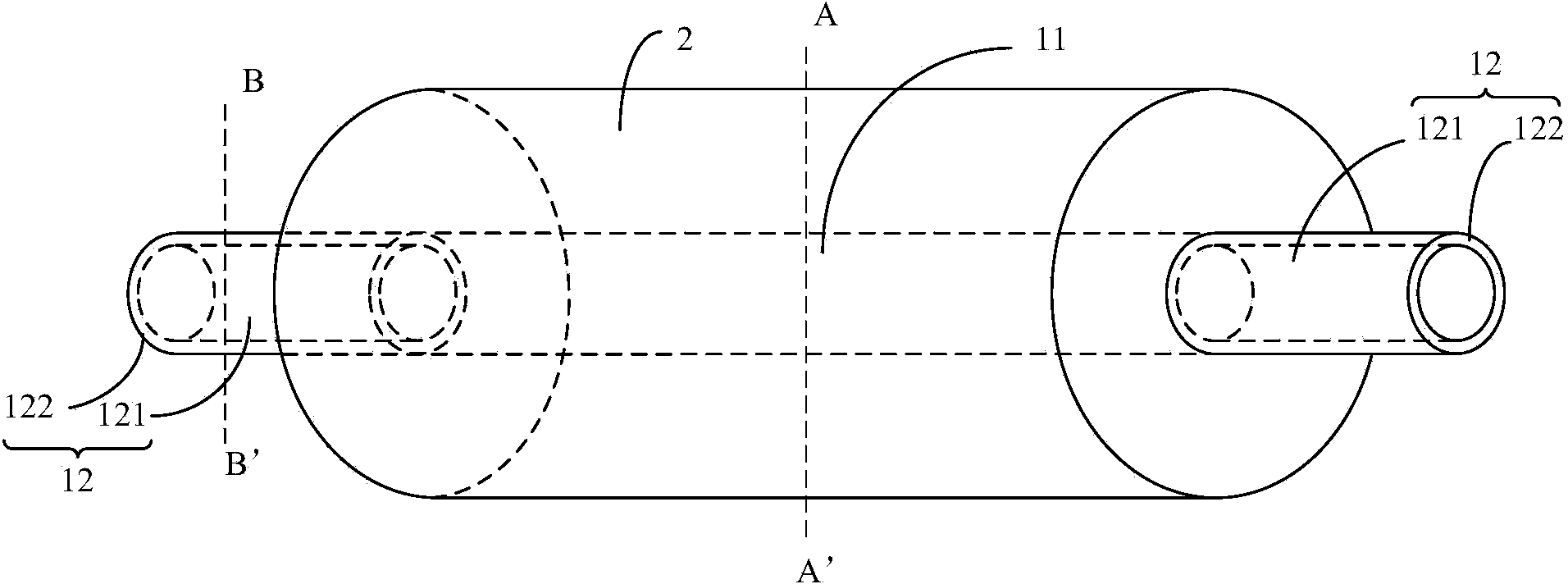

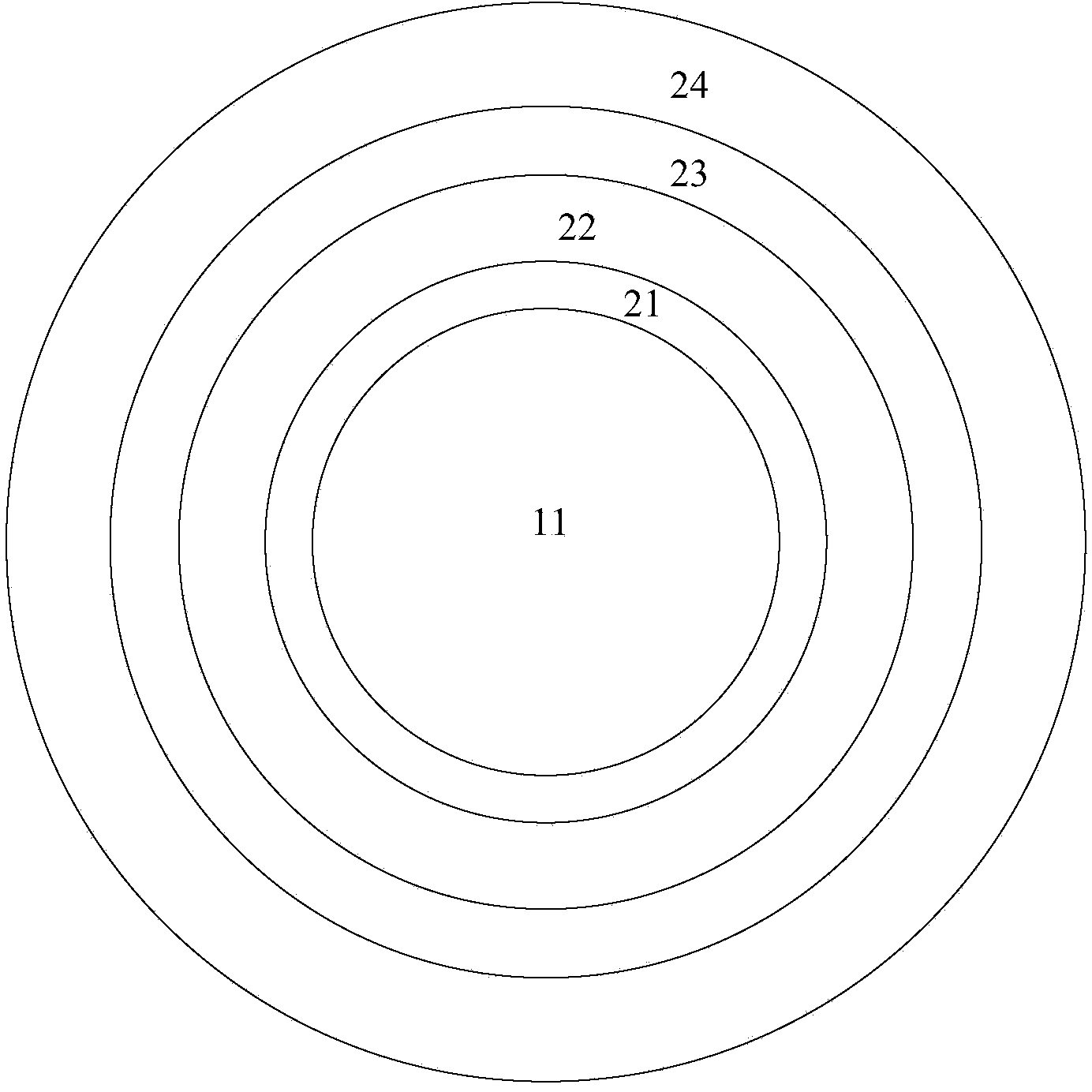

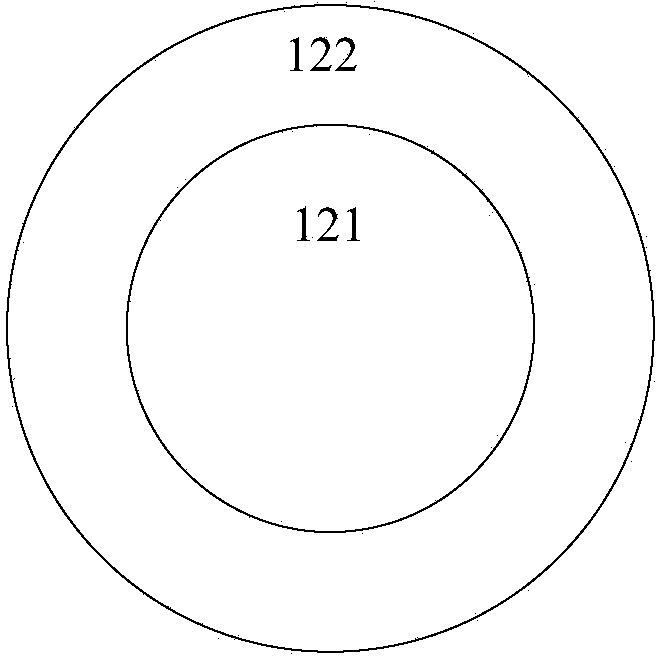

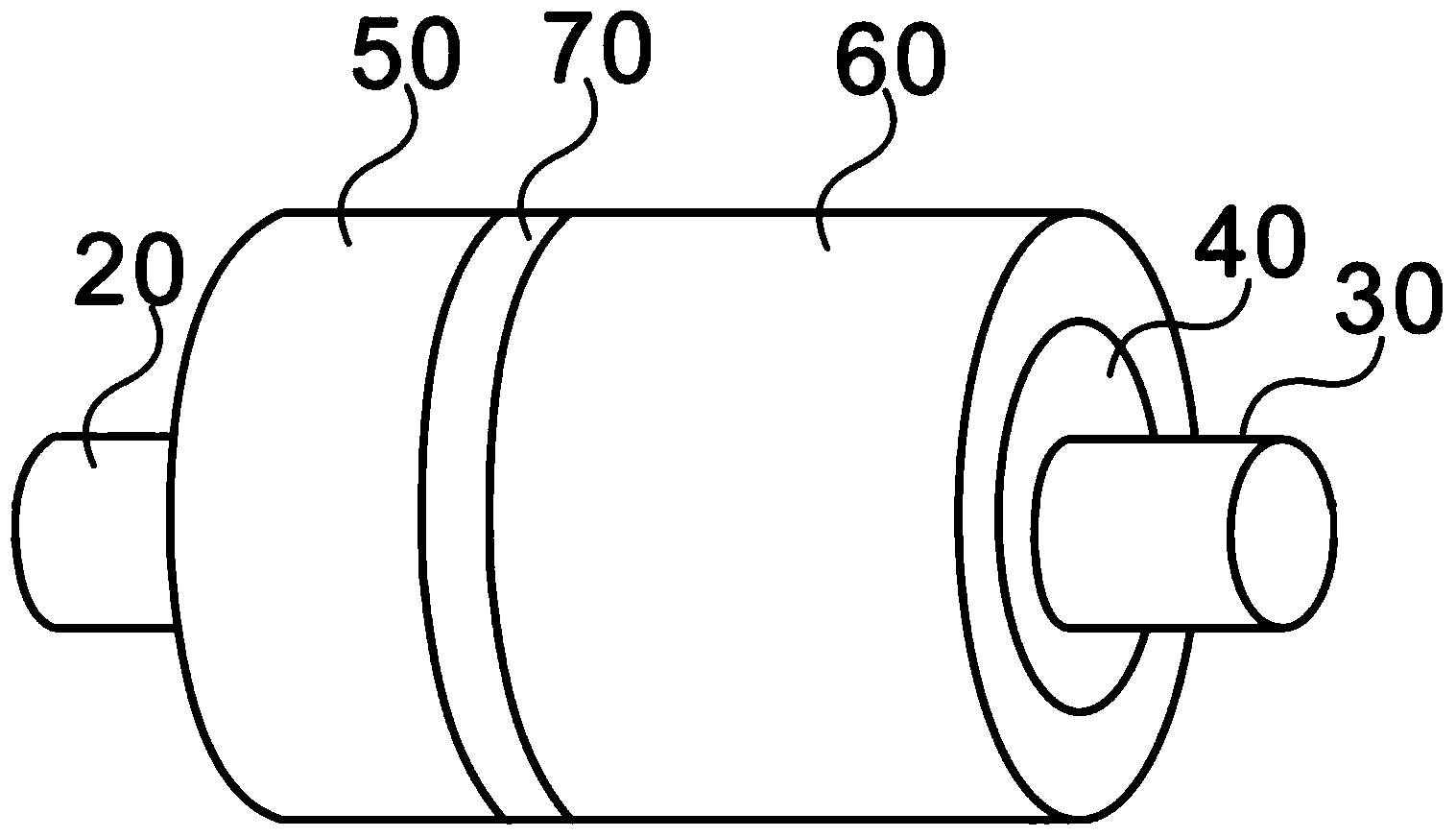

The invention provides an SONOS (silicon oxide nitride oxide silicon) flash memory device and a compiling method thereof. The SONOS flash memory device comprises a substrate of a cylinder structure and a grid electrode which wraps the middle of the substrate, wherein a source terminal and a drain terminal are respectively arranged at two ends of the substrate, the grid electrode comprises a first silicon gate and a second silicon gate which are parallel, a first oxidation layer is arranged between the first silicon gate and the second silicon gate, and a second oxidation layer arranged on the substrate, a silicon nitride layer arranged on the second oxidation layer and used to store electric charges and a third oxidation layer arranged on the silicon nitride layer are sequentially arranged between the second silicon gate and the substrate. The above structure of the SONOS flash memory device can restrain short channel effects and resist threshold voltage drifts, and simultaneously can effectively reduce the critical size of the SONOS flash memory device. The compiling method of the SONOS flash memory device assists in movement of thermion by adjusting voltage of the grid electrode and the drain terminal, provides sufficient oxidation layer crossing energy to complete compiling, improves compiling efficiency of the SONOS flash memory device, and reduces compiling electric current power consumption.

Owner:SHANGHAI HUALI MICROELECTRONICS CORP

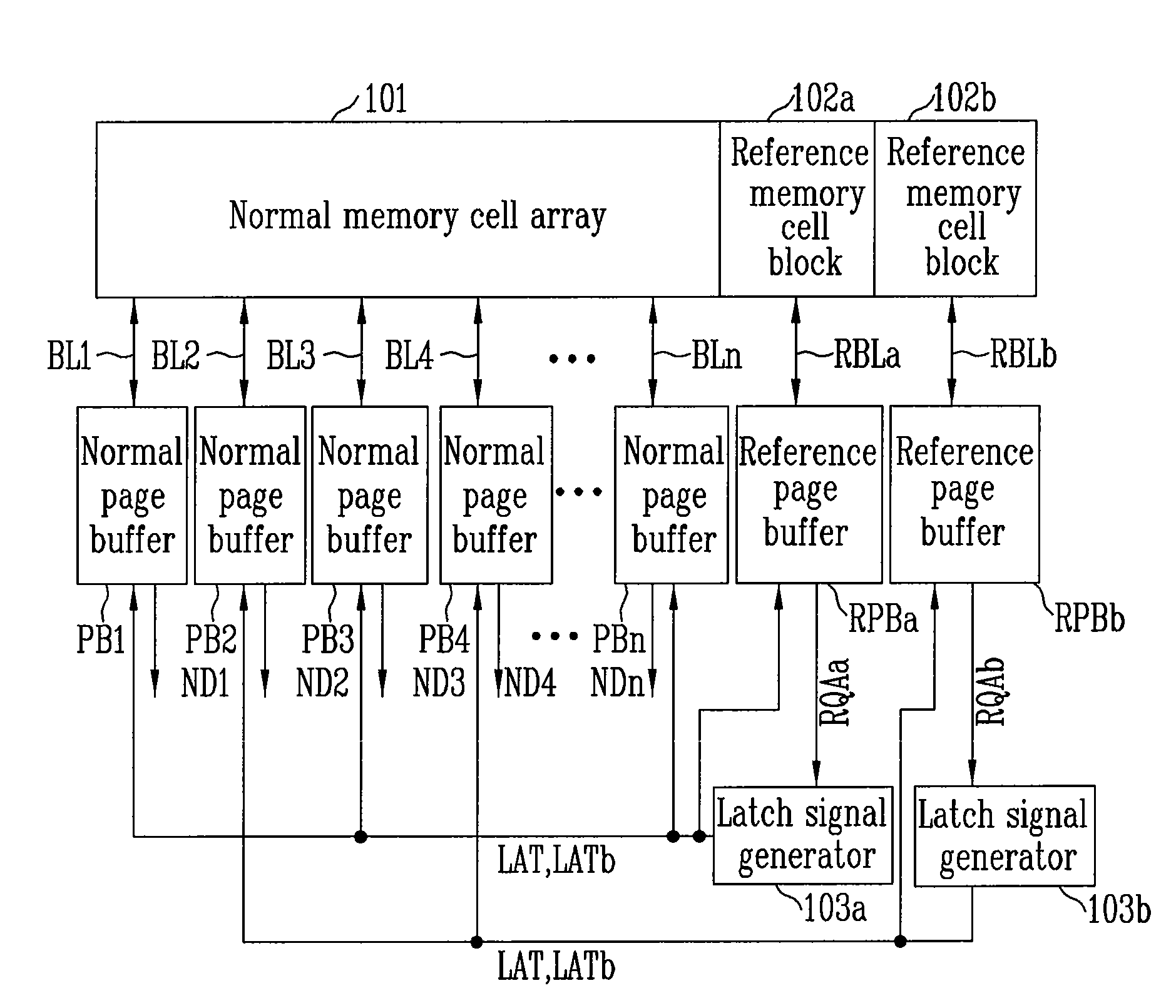

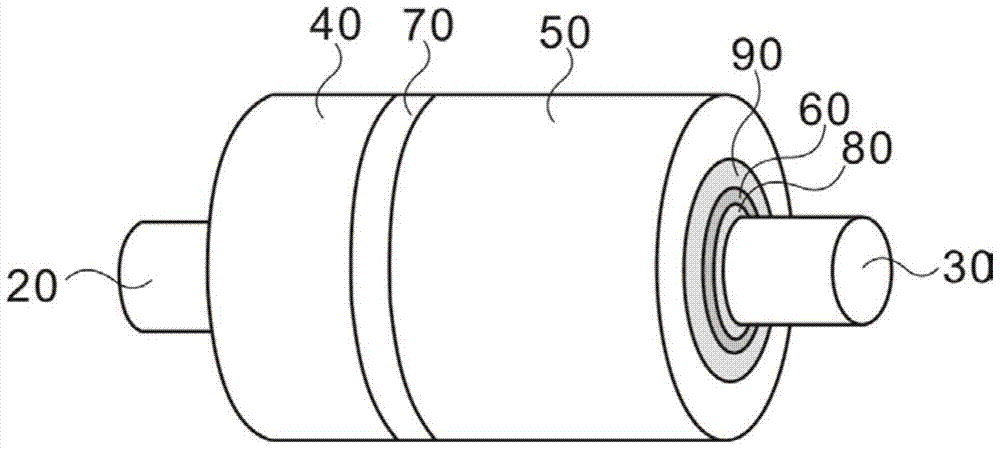

Flash memory device

Owner:SK HYNIX INC

Flash memorizer

ActiveCN103915442AReduce read errorsEasy to controlSolid-state devicesSemiconductor devicesEngineeringContact line

The invention discloses a flash memorizer. The flash memorizer comprises a cylindrical body structure serving as a substrate, wherein the body structure is of an N type silicon structure and comprises a middle portion and two end portions on the two sides of the middle portion, a grid electrode is wrapped on the middle portion in a surrounding mode to form a surrounding grid. The two end portions serve as a source electrode and a drain electrode and respectively comprise a layer of P type doped area. The portion, surrounded by the corresponding P type doped area, of each end portion is led out through a contact line and used for exerting a substrate voltage. A smaller grid length can be obtained, the voltages used for controlling the grid and a floating grid can well control a groove, the percentage of the portion, occupied by a source and drain depletion region through extension, of the total size of the depletion region can be lowered, the short-channel effect can be restrained, threshold voltage drift can be resisted, and reading mistakes of the flash can be reduced.

Owner:SHANGHAI HUALI MICROELECTRONICS CORP

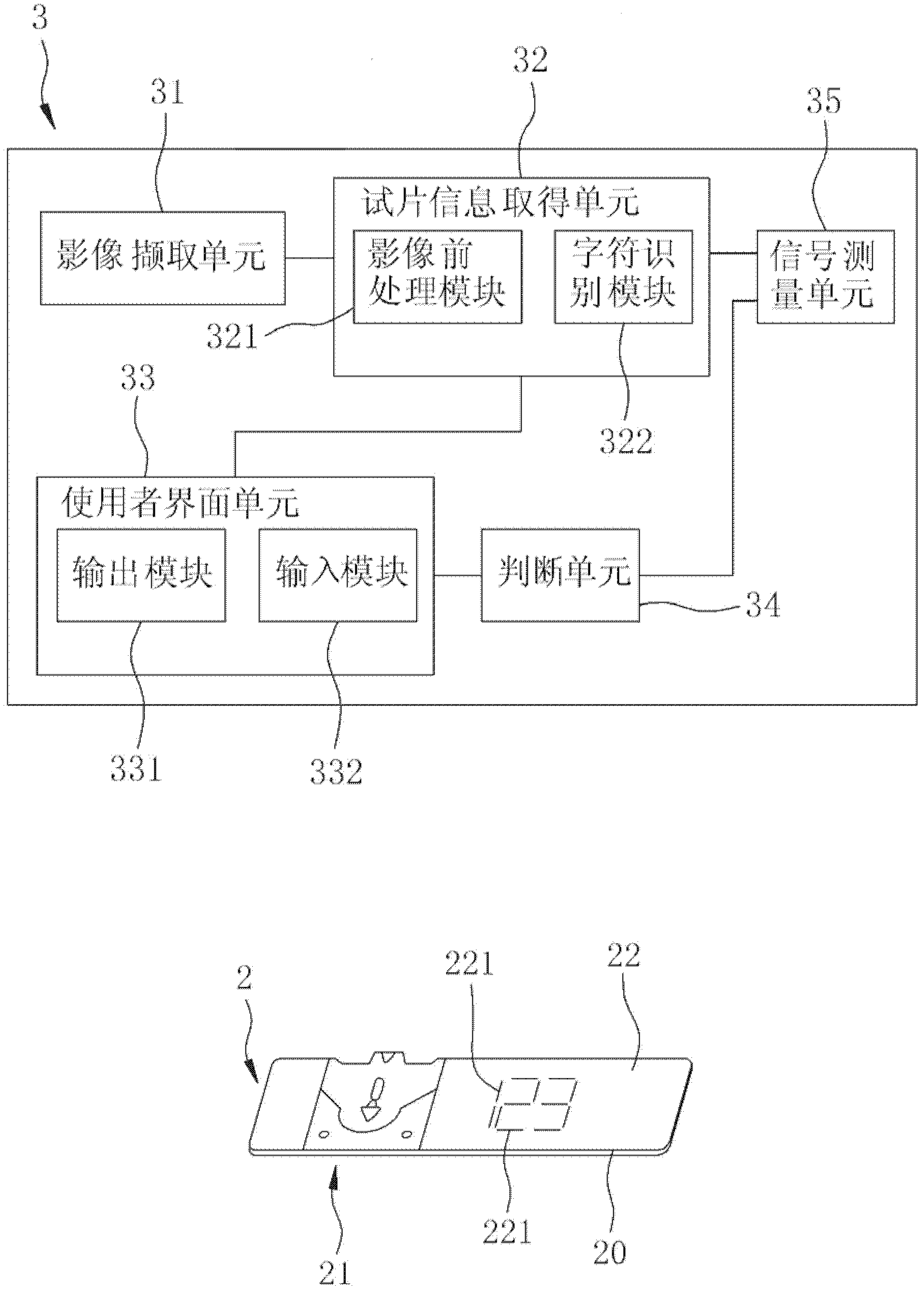

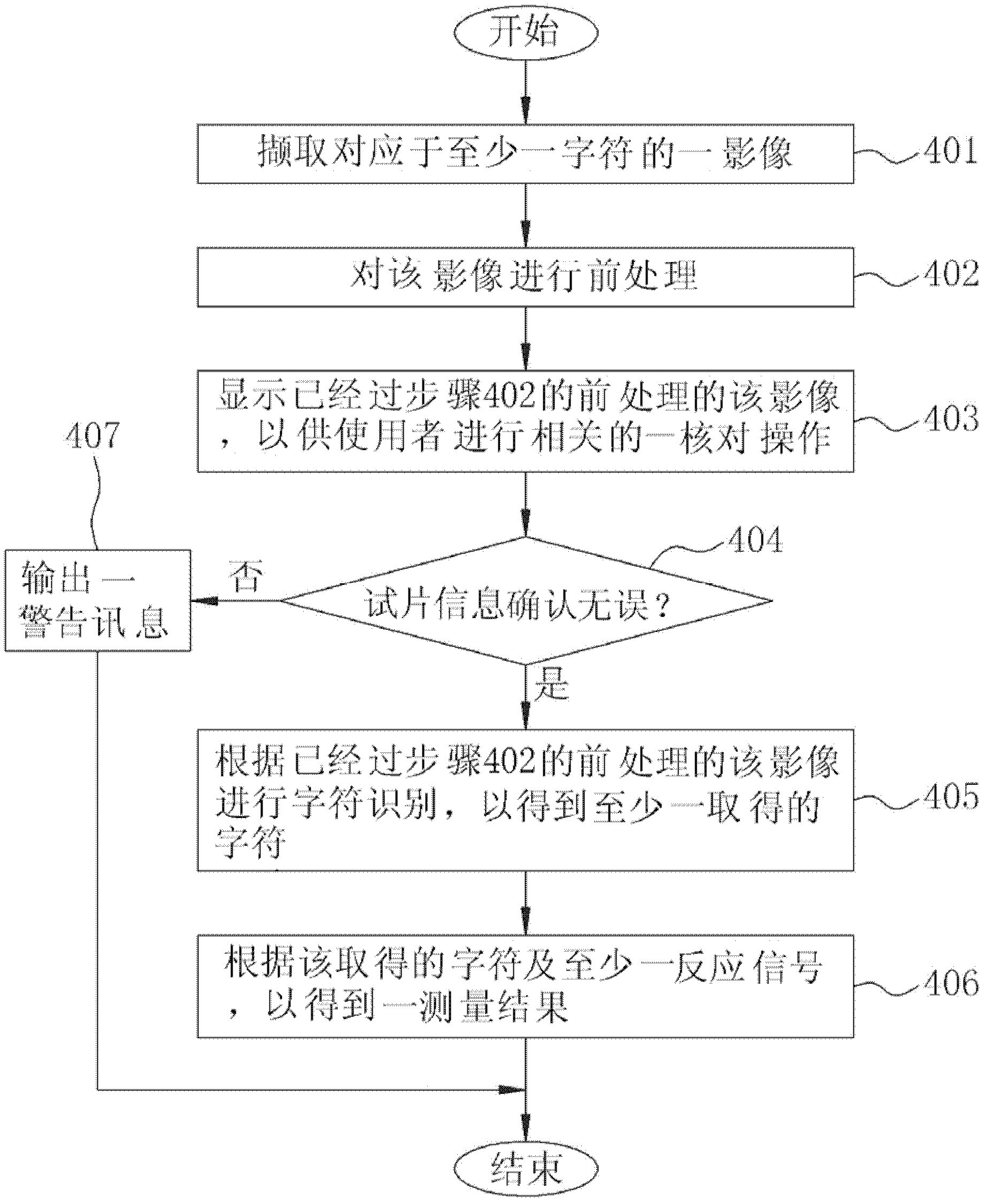

Biosensor measuring system with bidirectionally checkable test piece information and detection test piece structure

ActiveCN103076441AReduce read errorsReduce the chance of misjudgmentBiological testingMeasurement deviceIdentifiability

The invention provides a biosensor measuring system with bidirectionally checkable test piece information and a detection test piece structure. The biosensor measuring system comprises the detection test piece structure and a measuring device. The detection test piece structure comprises a biosensor unit generating at least one reaction signal, a detection test piece of a surface and a character with identifiability arranged on the surface. The measuring device comprises an image acquisition unit used for acquiring an image, a test piece information acquisition unit used for acquiring an obtained character based on the image, a user interface unit for correspondence to output of the image and checking operation, a determination unit used for receiving a check operation signal to carry out determination and a signal measuring unit which obtains a measuring result based on the obtained character and a reaction signal when it is confirmed that the test piece information has no error.

Owner:BIONIME

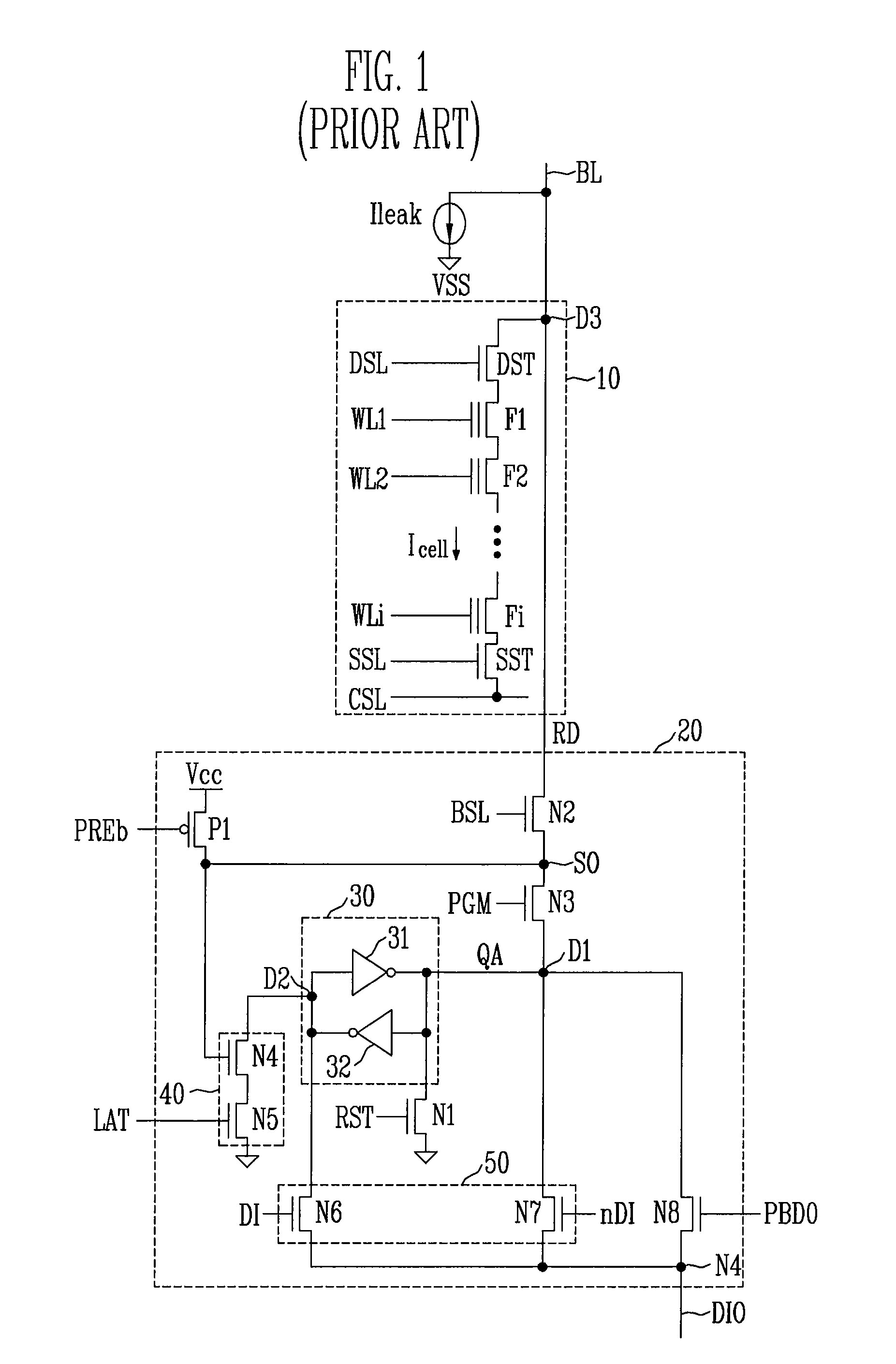

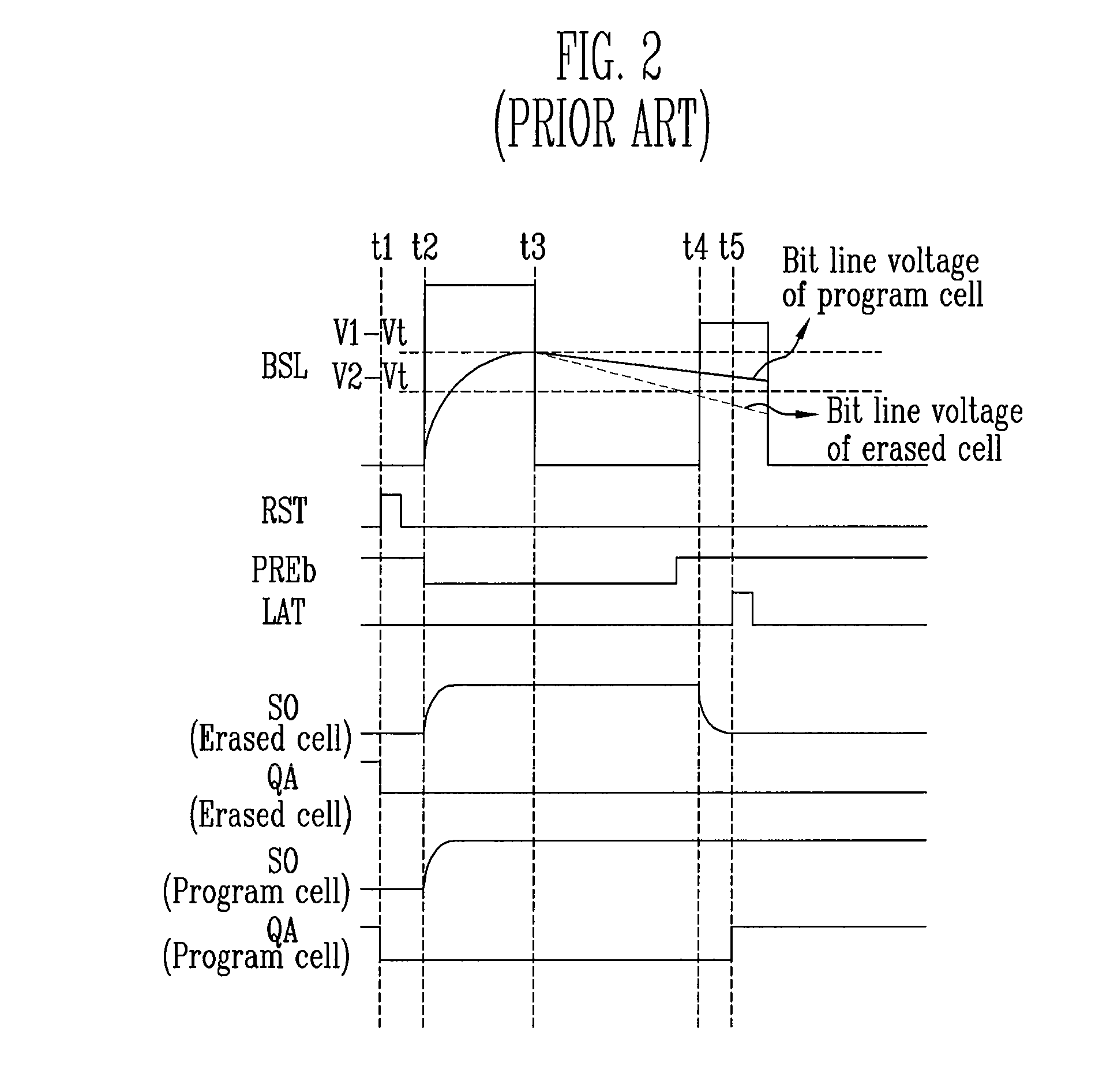

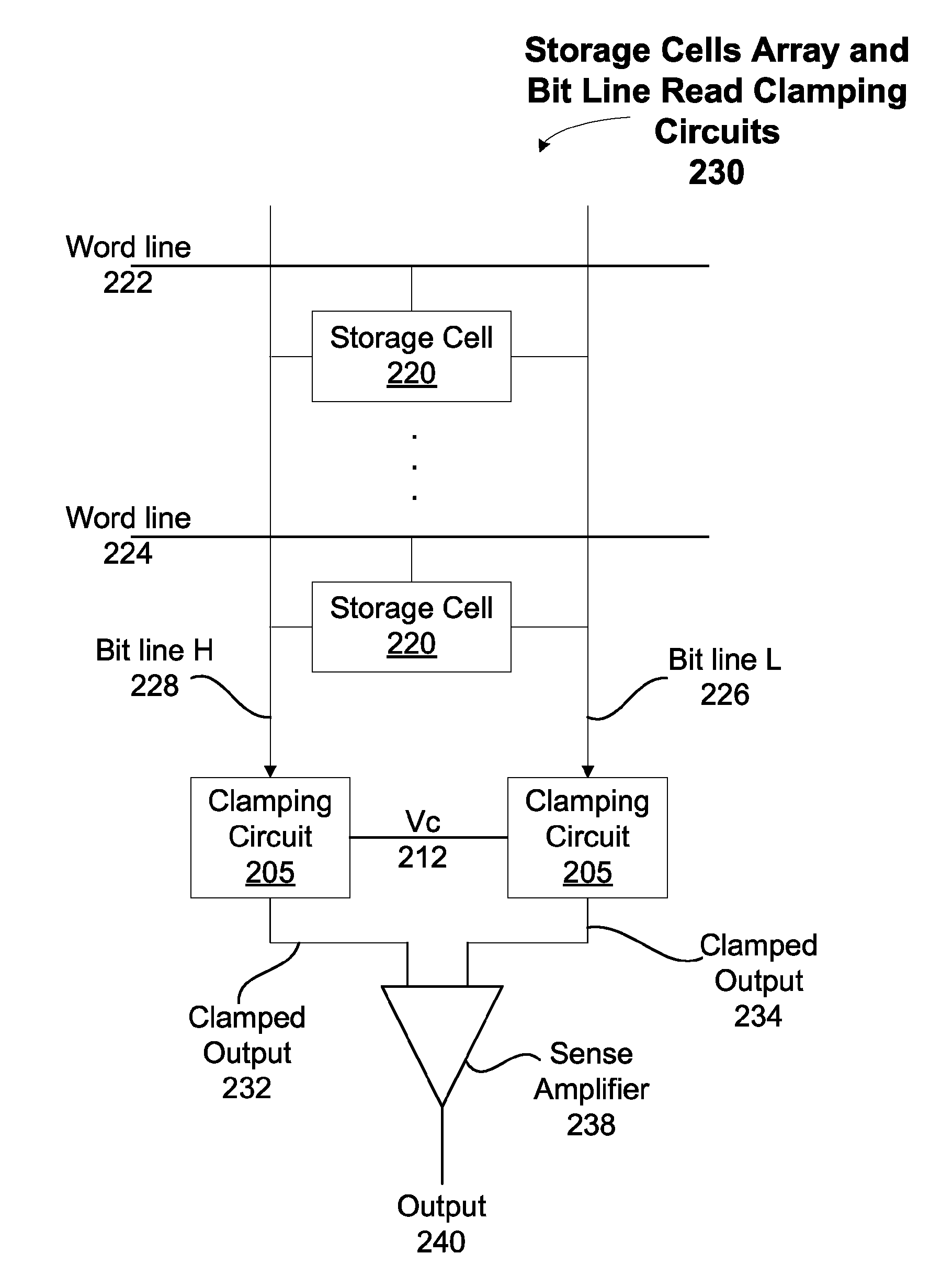

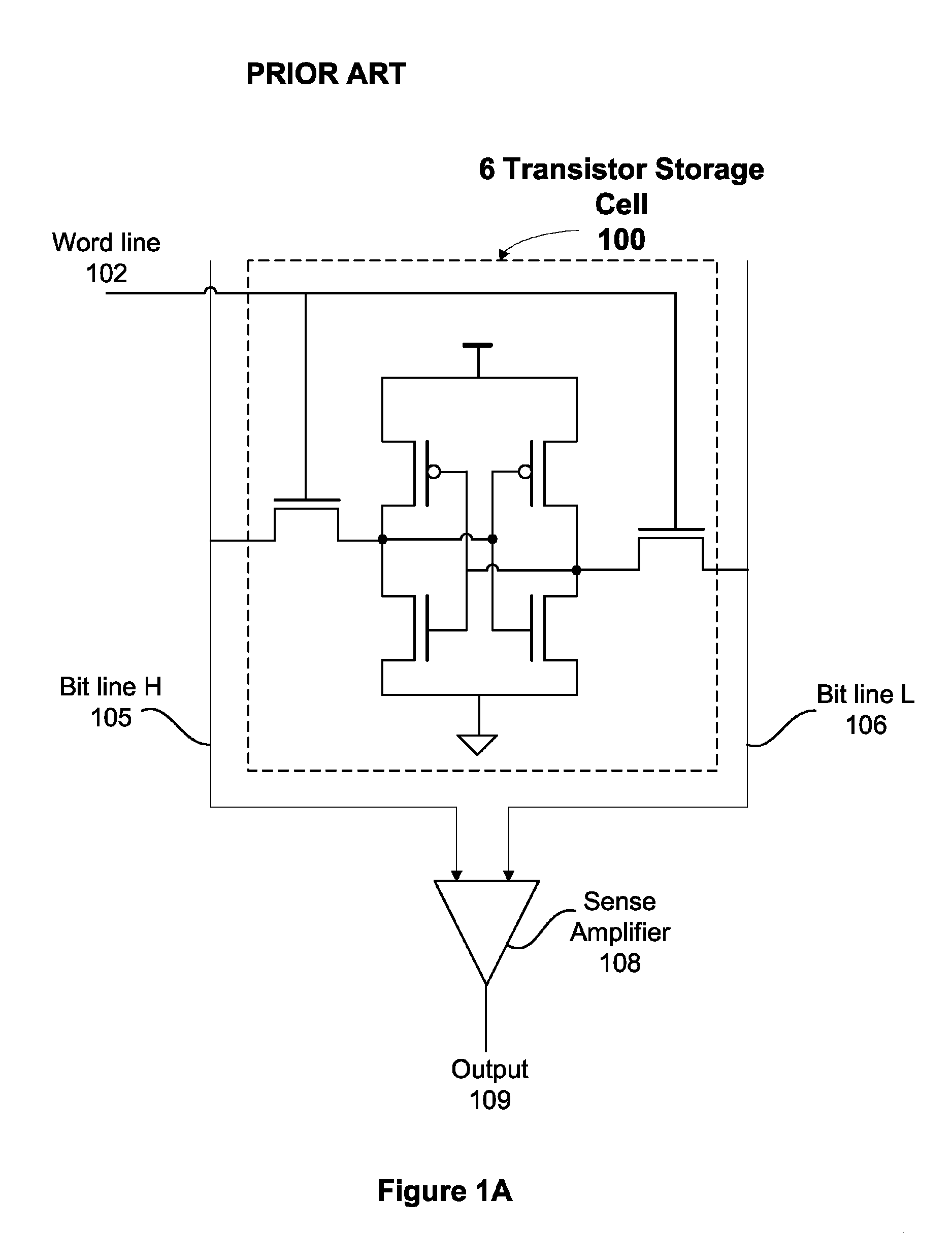

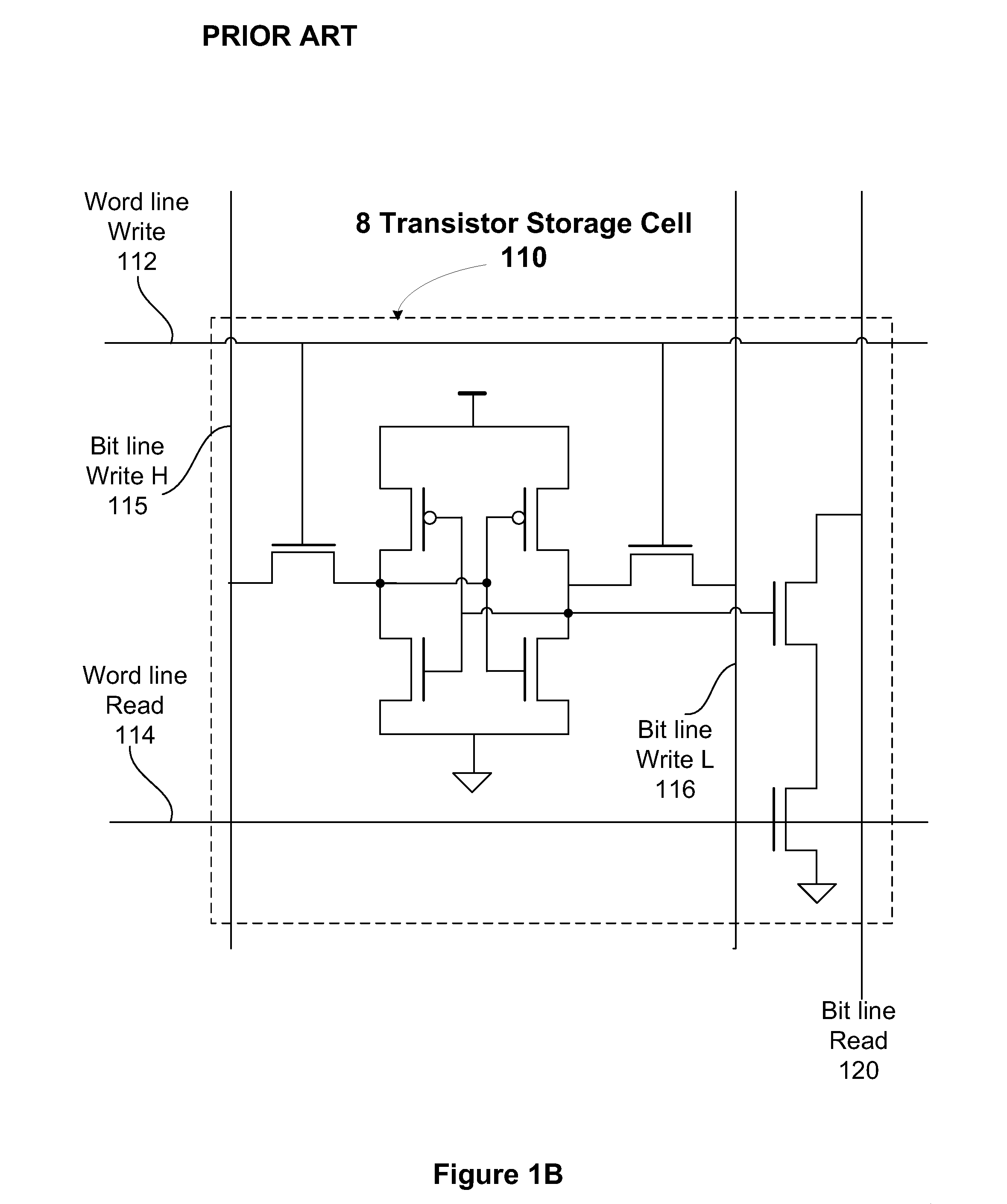

Clamped bit line read circuit

ActiveUS8559248B2Reduce generationReduce dynamic power consumptionRead-only memoriesDigital storageBit lineHemt circuits

One embodiment of the present invention sets forth a clamping circuit that is used to maintain a bit line of a storage cell in a memory array at a nearly constant clamp voltage. During read operations the bit line is pulled high or low from the clamp voltage by the storage cell and a change in current on the bit line is converted by the clamping circuit to produce an amplified voltage that may be sampled to read a value stored in the storage cell. The clamping circuit maintains the nearly constant clamp voltage on the bit line. Clamping the bit line to the nearly constant clamp voltage reduces the occurrence of read disturb faults. Additionally, the clamping circuit functions with a variety of storage cells and does not require that the bit lines be precharged prior to each read operation.

Owner:NVIDIA CORP

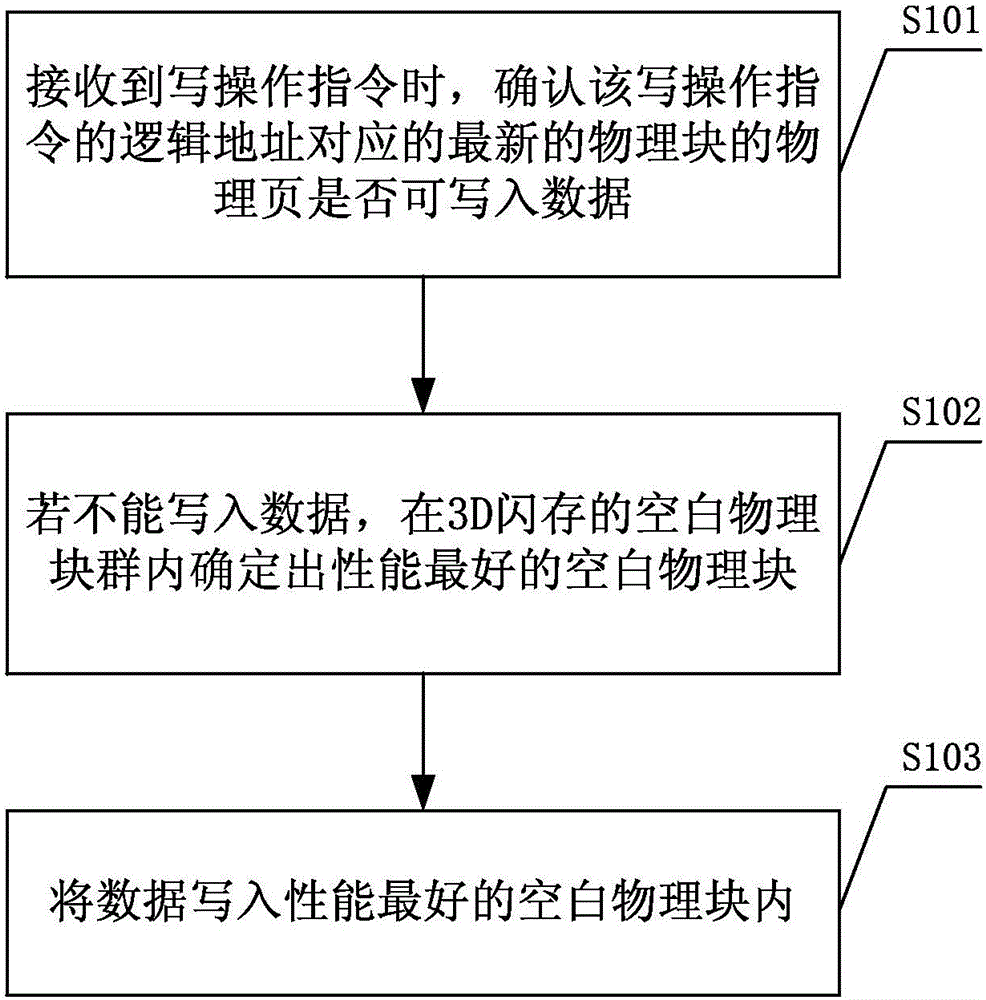

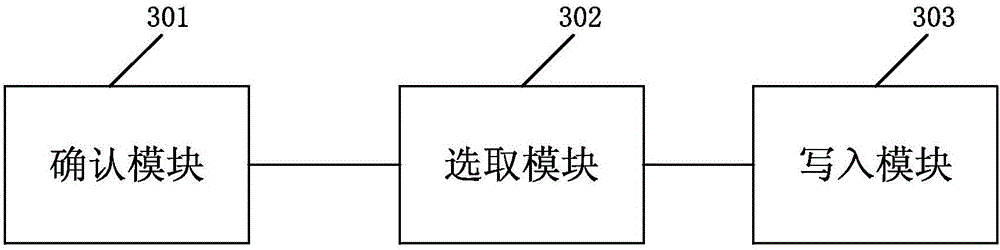

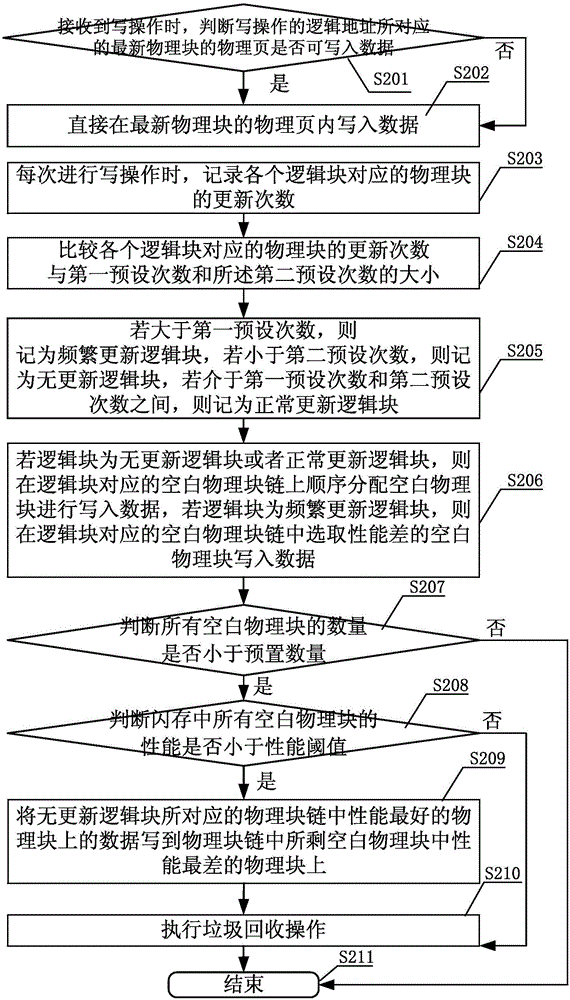

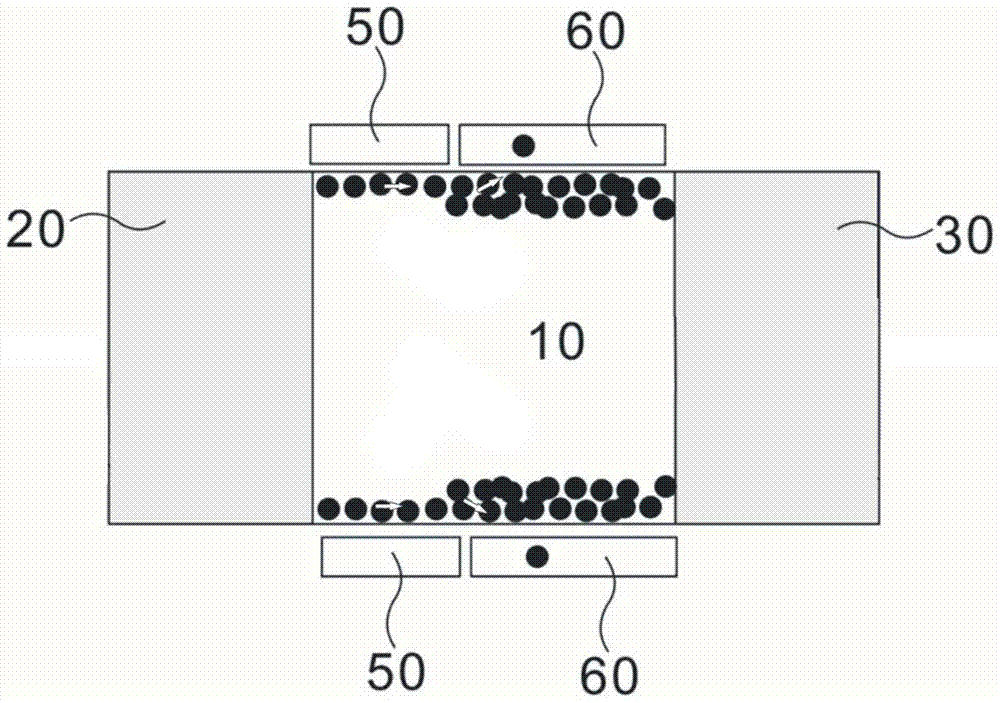

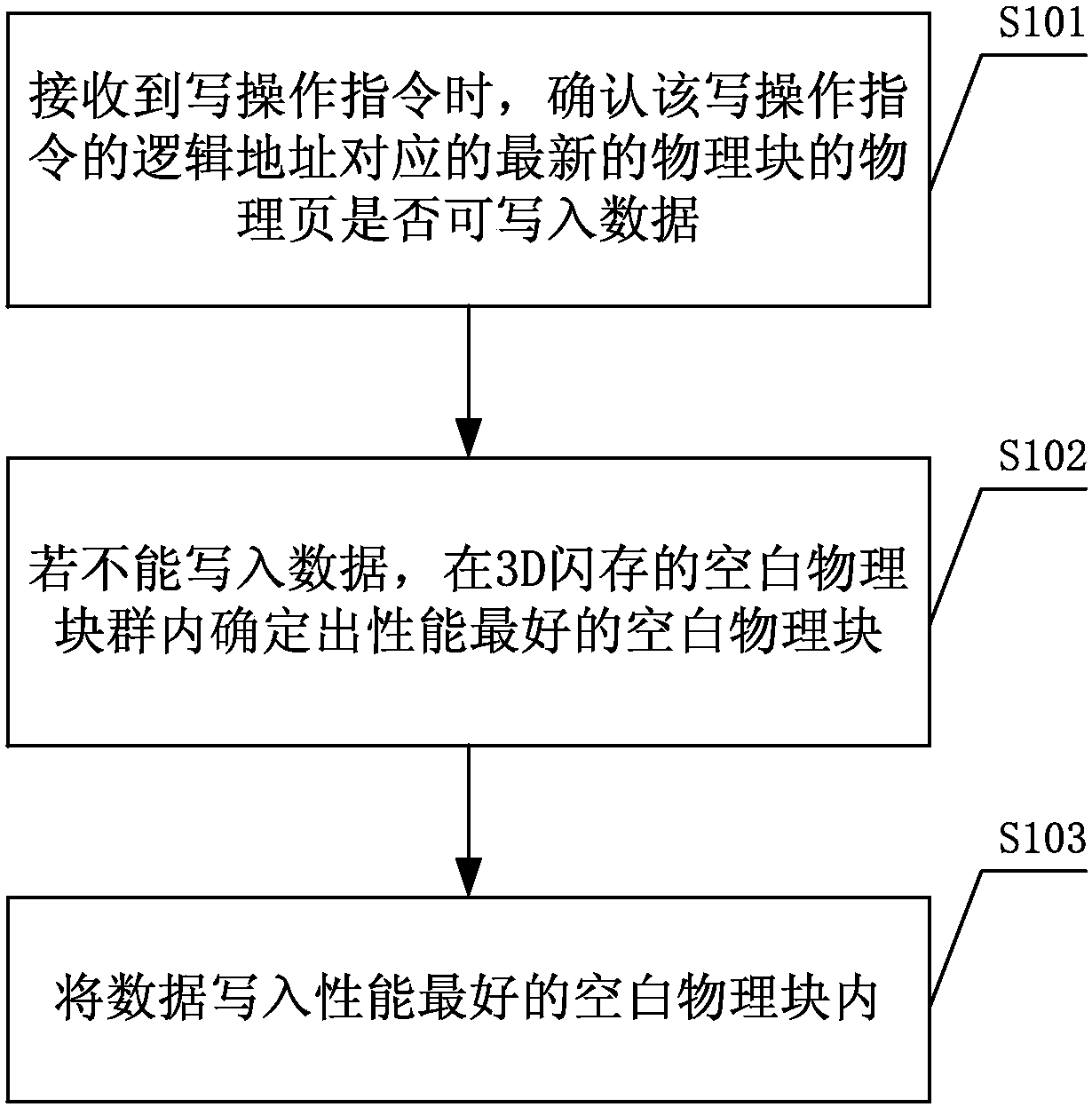

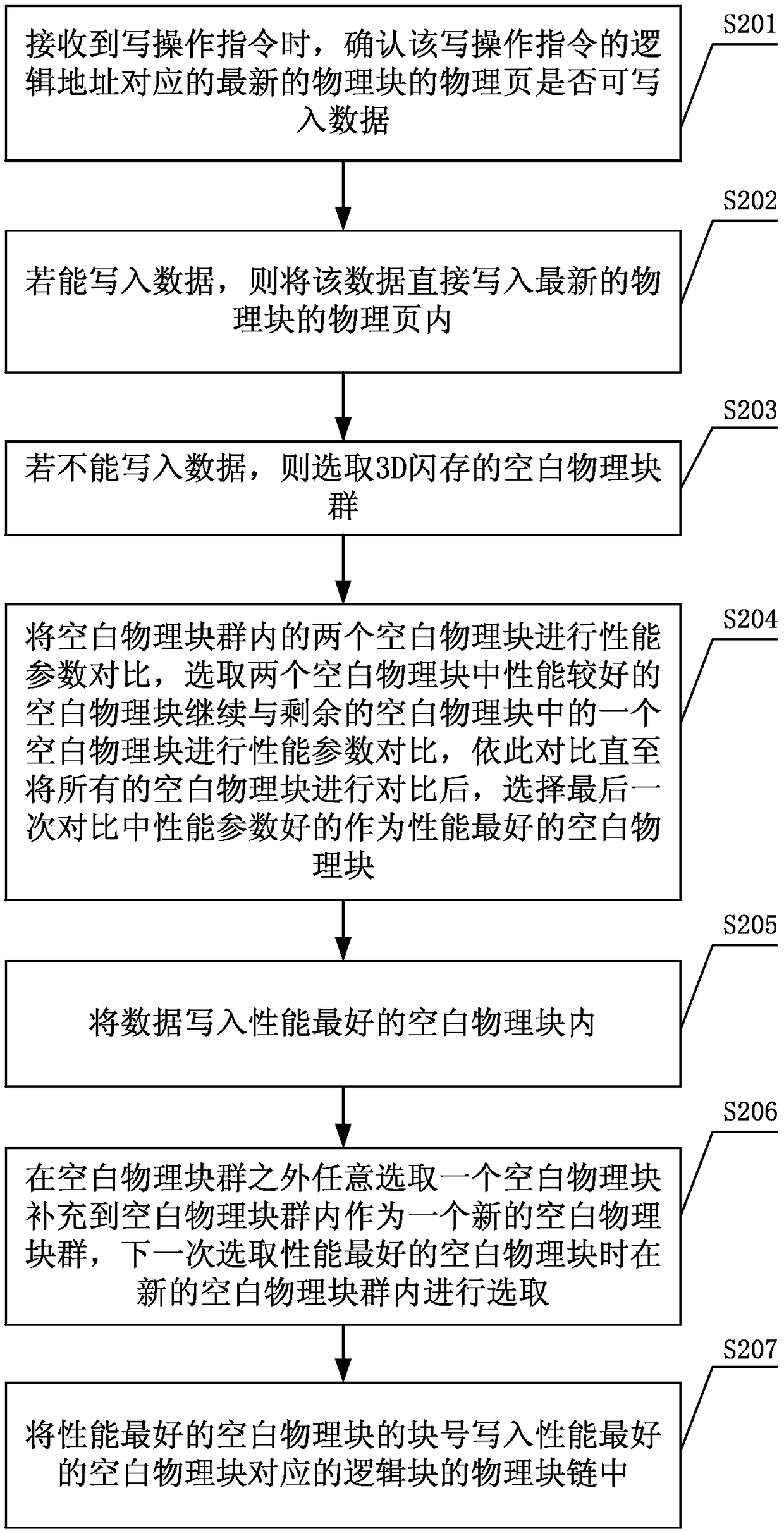

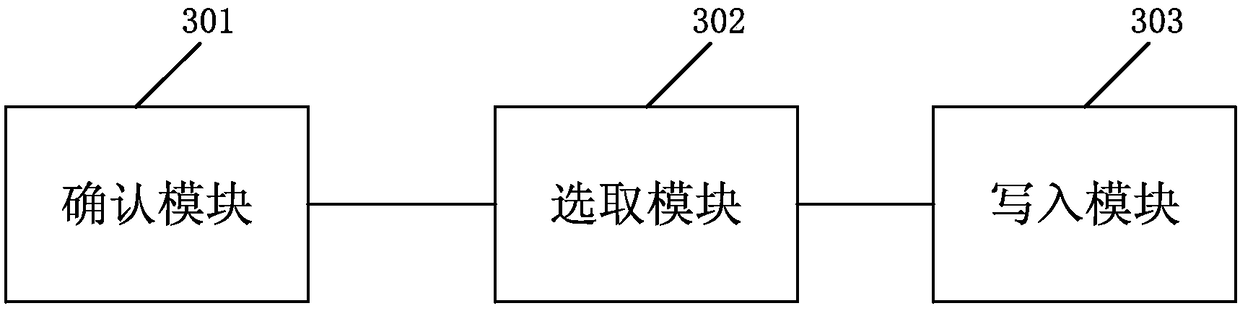

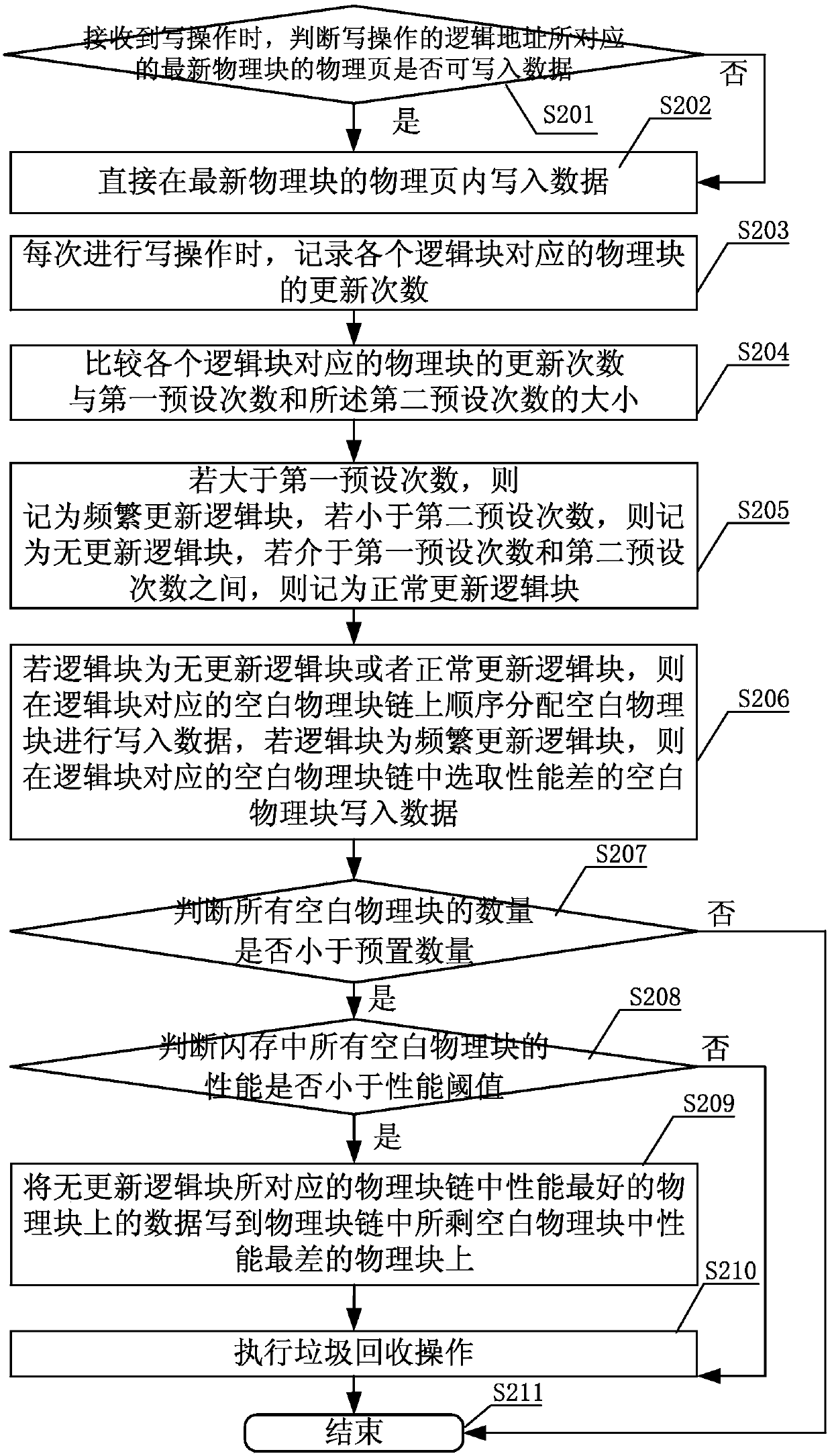

Selection method and selection system for physical blocks of 3D flash memory

ActiveCN106021123AGuaranteed correctnessReduce workloadMemory adressing/allocation/relocationWorkloadSelection system

The invention is suitable for the technical field of storage and provides a selection method and a selection system for physical blocks of a 3D flash memory. The selection method comprises the following steps of confirming whether data can be written in a physical page of a latest physical block corresponding to a logic address of a writing operation instruction or not when the writing operation instruction is received; if the data cannot be written in the physical page, determining a blank physical block with the best performance from a blank physical block group of the 3D flash memory; and writing the data in the blank physical block with the best performance. According to the selection method, the performance of each blank physical block is considered in a data writing process, so that the generation of writing errors and read errors can be reduced, the data correctness can be ensured to the maximum extent, and the workload of ECC (Error Correcting Code) error correction is reduced.

Owner:SHENZHEN UNIV

Optical recording medium and process for production thereof

InactiveUS20020106475A1Reduce leakageReduce error rateLayered productsGroove/land recordingSolventOptical recording

In an optical recording medium, a recording layer is formed by coating a substrate with a solution of coloring matter comprising a coloring matter dissolved in a solvent comprising a mixture of cyclooctane and at least one hydrocarbon having 6 to 9 carbon atoms other than cyclooctane. The obtained optical recording medium enables suppressing the leakage of land prepit signal for address information into RF signal for recorded data at the time of recorded data reproduction, thereby attaining a lowering of error rate.

Owner:MITSUI CHEM INC

Floating gate flash memory device and programming method thereof

ActiveCN104377248AReduce the numberShorten the acceleration distanceTransistorSolid-state devicesGate oxideVoltage

The invention provides a floating gate flash memory device and a programming method of the floating gate flash memory device. The floating gate flash memory device comprise a substrate of a cylindrical structure, and a source end and a drain end are arranged at the two ends of the substrate; the middle of the substrate is covered with a grid, a gate oxide layer is arranged between the grid and the substrate, and the grid comprises a control gate and a floating gate. According to the programming method of the floating gate flash memory device, movement of hot electrons is assisted by applying bias voltage to provide sufficient energy to cross the gate oxide layer to complete compiling, the compiling efficiency of the flash memory is improved, and power consumption of compiling current is reduced; in addition, the floating gate flash memory device and the programming method of the floating gate flash memory device can effectively reduce the key size of the floating gate flash memory of a parse gate, increase the cell density of a flash memory array and namely increases the storage capacity and density of the flash memory.

Owner:SHANGHAI HUALI MICROELECTRONICS CORP

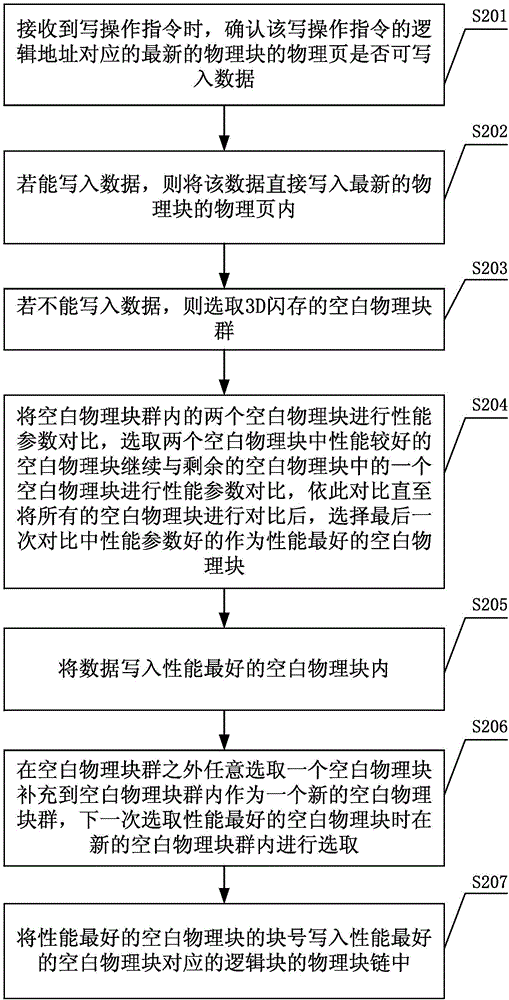

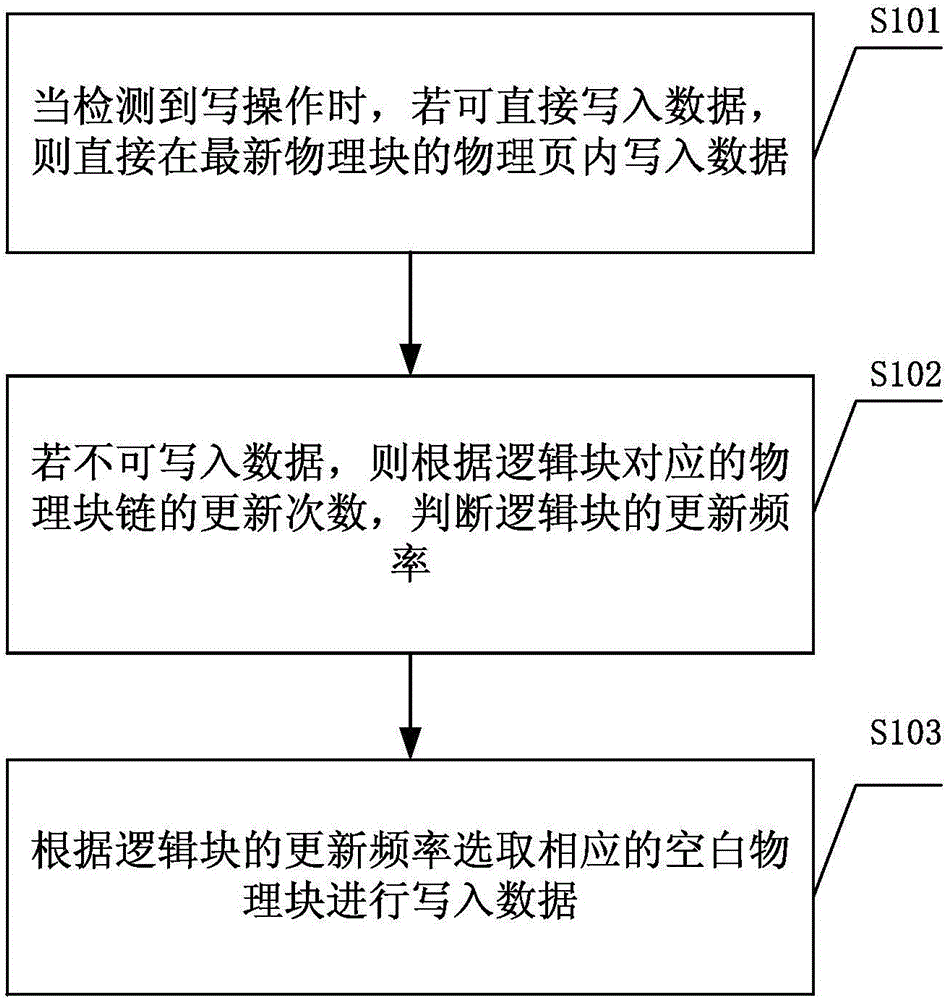

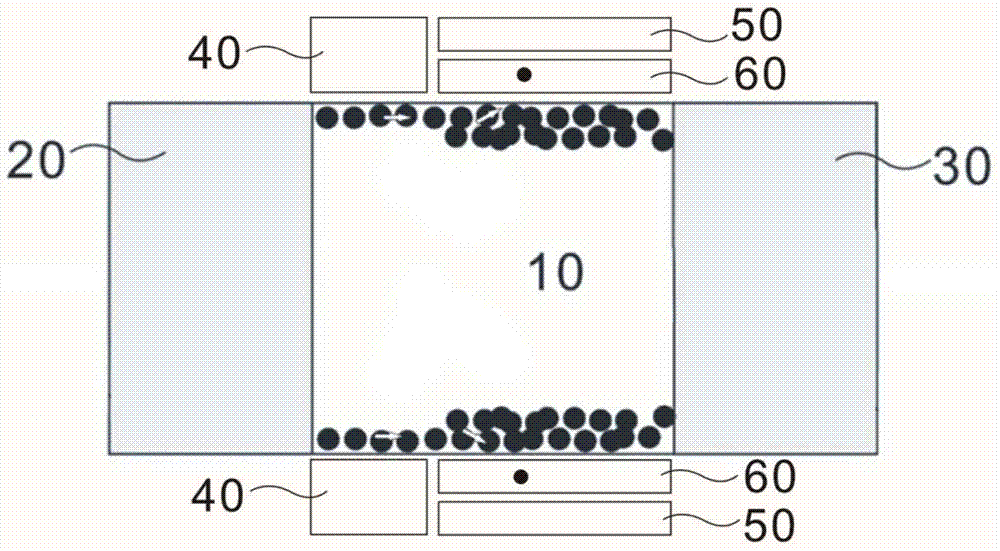

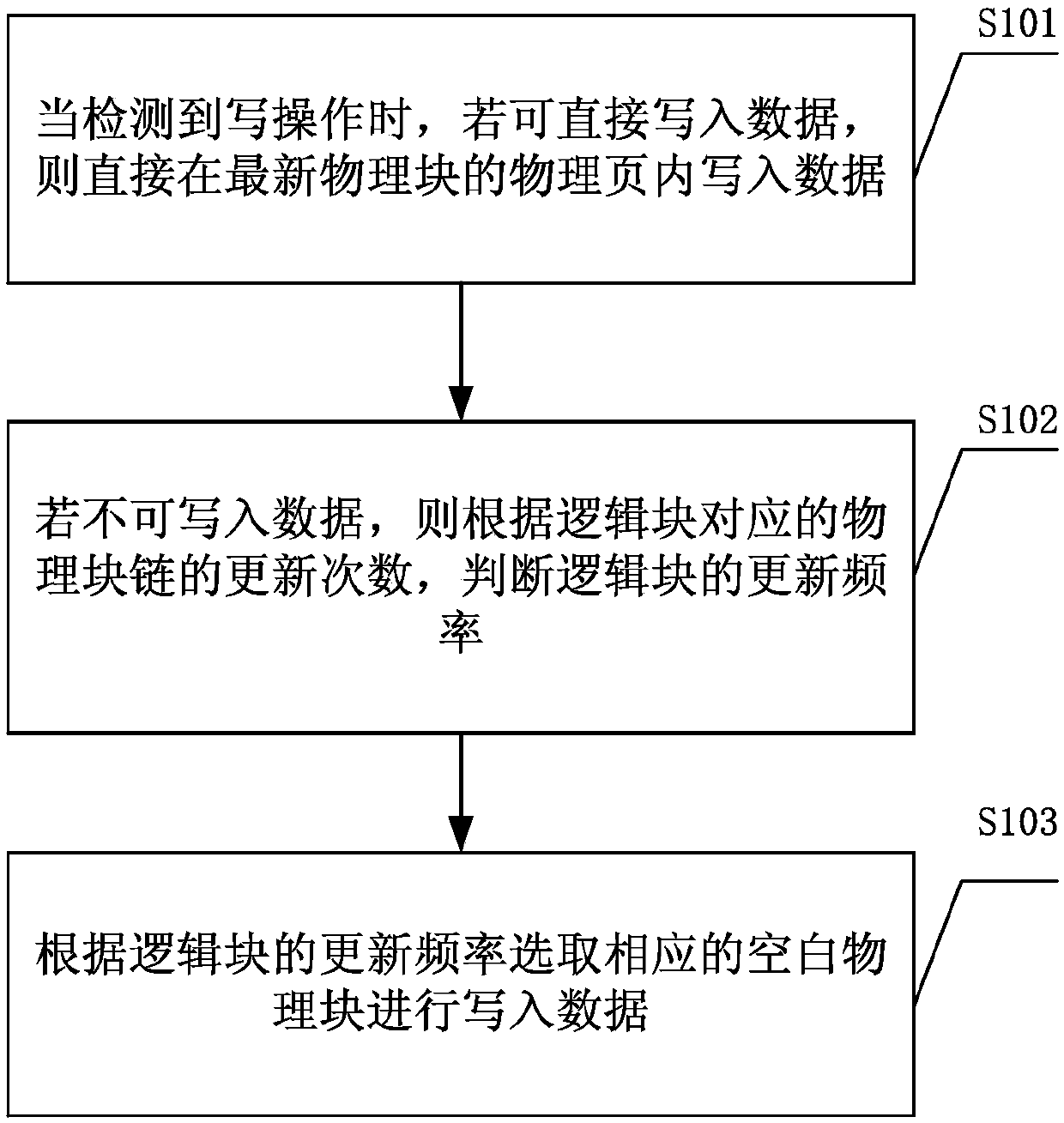

Data storage method and data storage system

ActiveCN106021124AGuaranteed correctnessReduce workloadMemory adressing/allocation/relocationComputer hardwarePaper data storage

The invention is suitable for the technical field of memories and provides a data storage method and a data storage system. The storage method comprises the following steps of directly writing data in a physical page of a latest physical block if the data can be written in the physical page when a writing operation is detected; if the data cannot be written in the physical page, judging the updating frequency of a logic block according to the updating frequency of a physical block chain corresponding to the logic block; and selecting a corresponding blank physical block according to the updating frequency of the logic block, and performing data writing. According to the storage method, the generation of writing errors and read errors can be reduced, the data correctness can be ensured to the maximum extent, and the workload of ECC (Error Correcting Code) error correction is reduced.

Owner:SHENZHEN UNIV

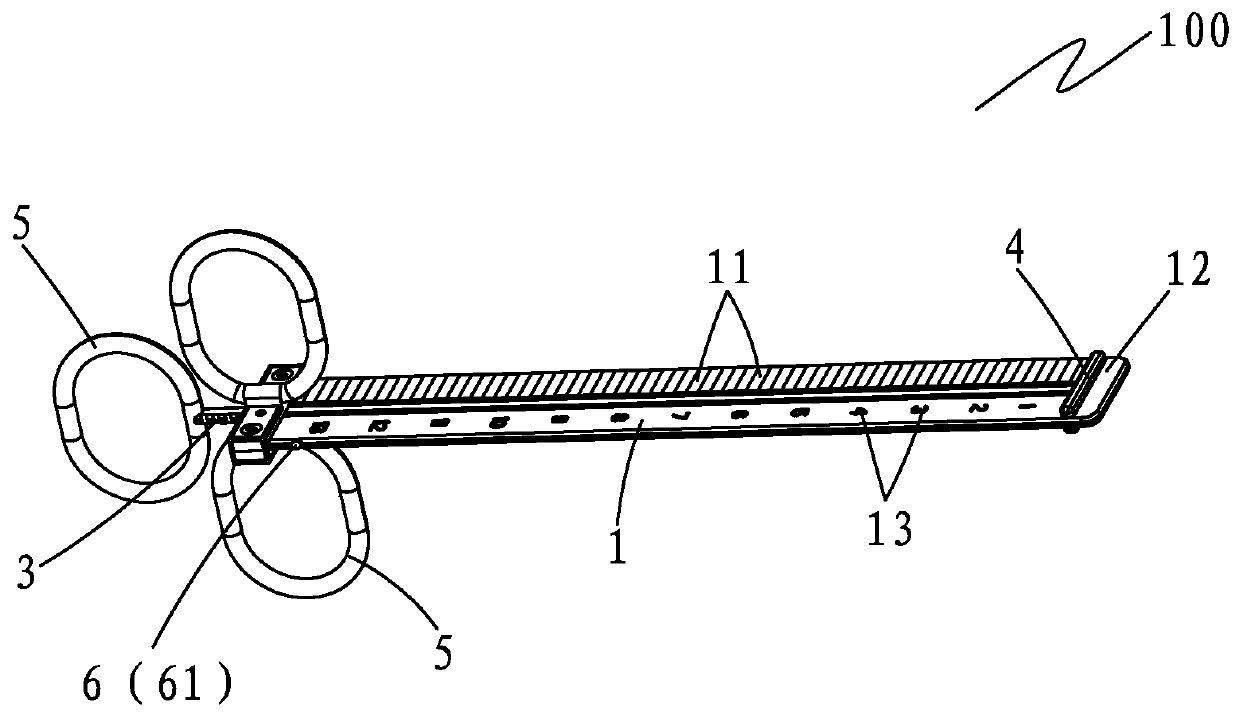

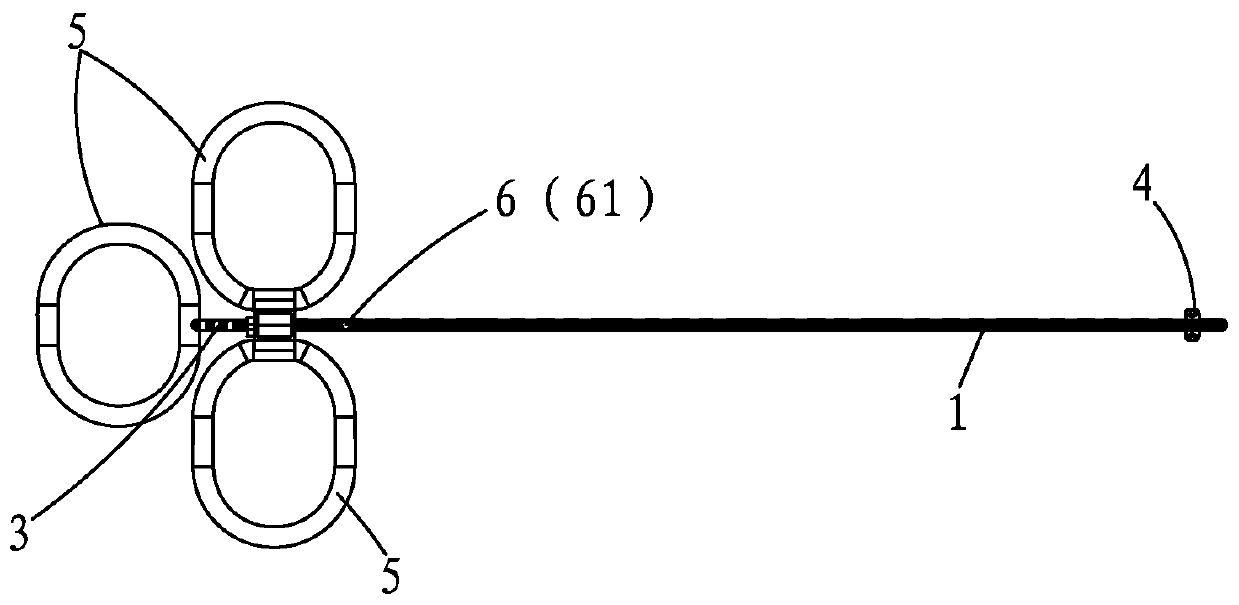

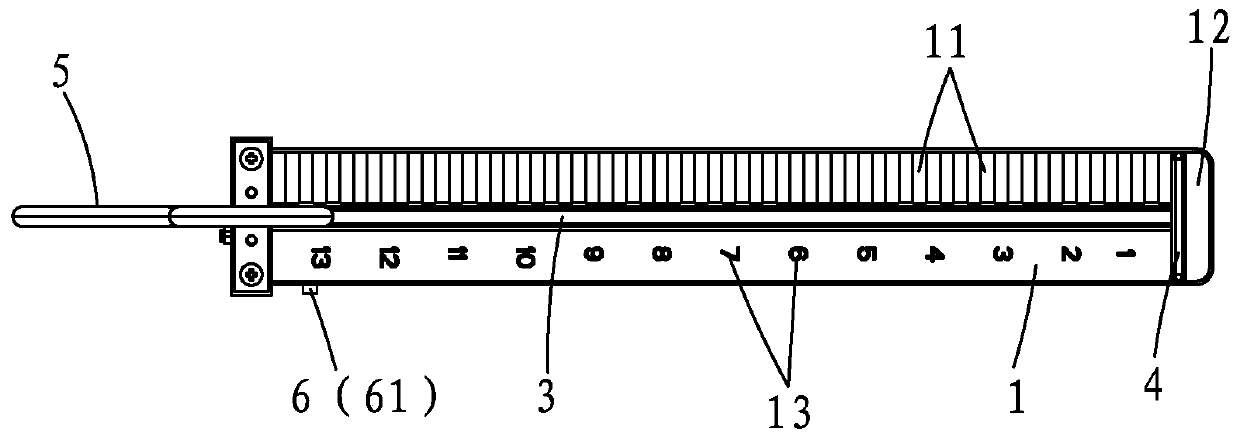

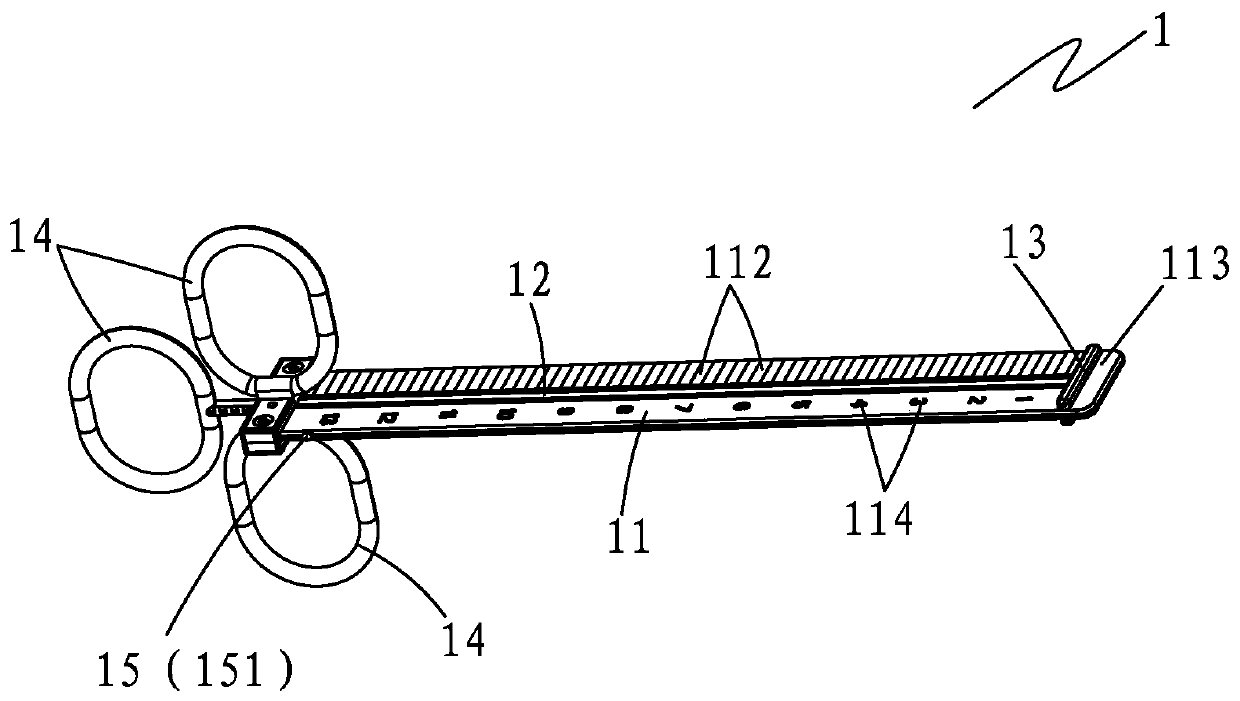

Measuring instrument for pelvic organ prolapsed

PendingCN110731780AConvenience to workReduce read errorsCatheterDiagnostic recording/measuringMeasuring instrumentEngineering

The invention provides a measuring instrument for pelvic organ prolapsed. The instrument includes a graduated scale body, a pull rod and a vernier; the graduated scale body is axially provided with alimiting groove or a limiting hole, the pull rod is inserted into the limiting groove or the limiting hole, and the vernier is fixedly arranged on the front end of the pull rod; and when the pull rodis stressed, the pull rod drives the vernier to move axially. The instrument has the following advantages: the instrument provided by the invention can facilitate the work of clinical operators and reduce reading errors.

Owner:沈平

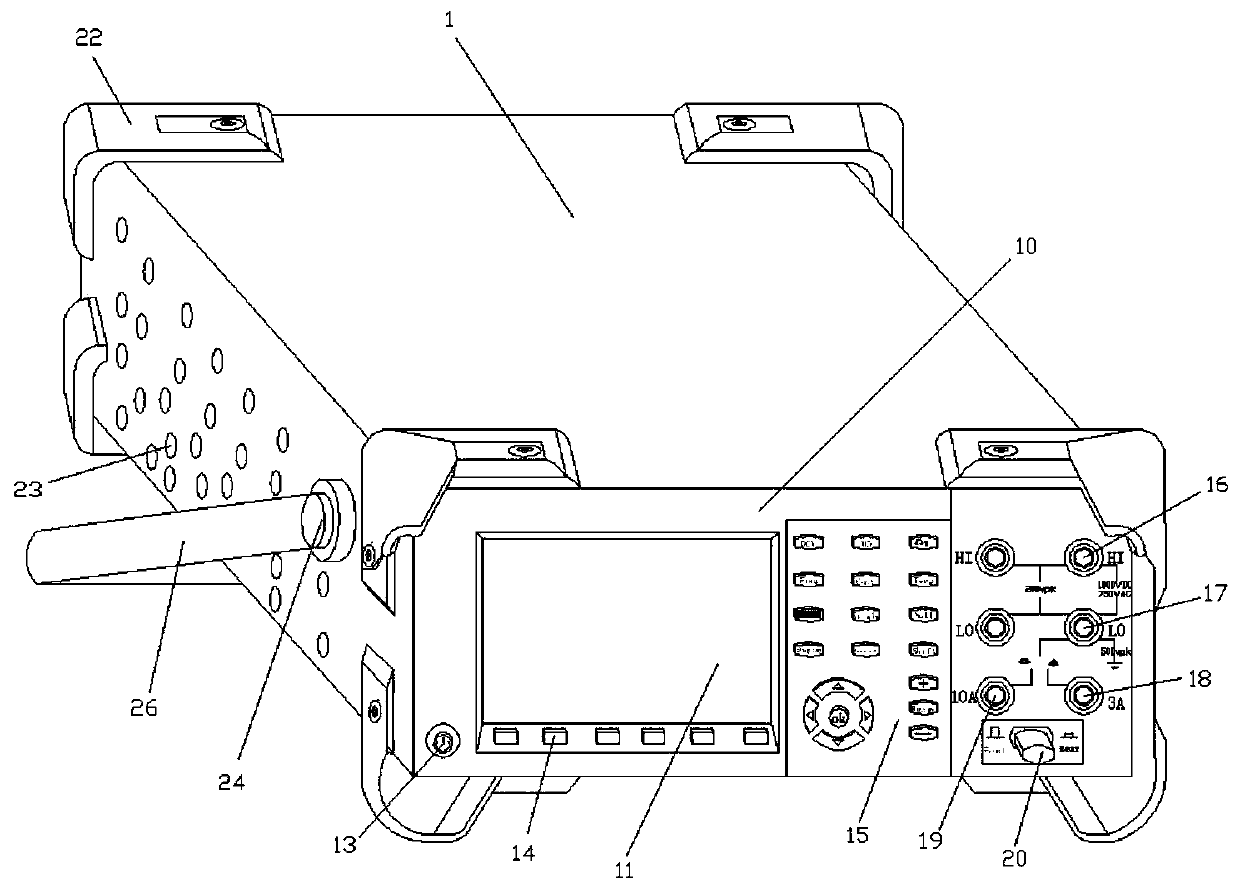

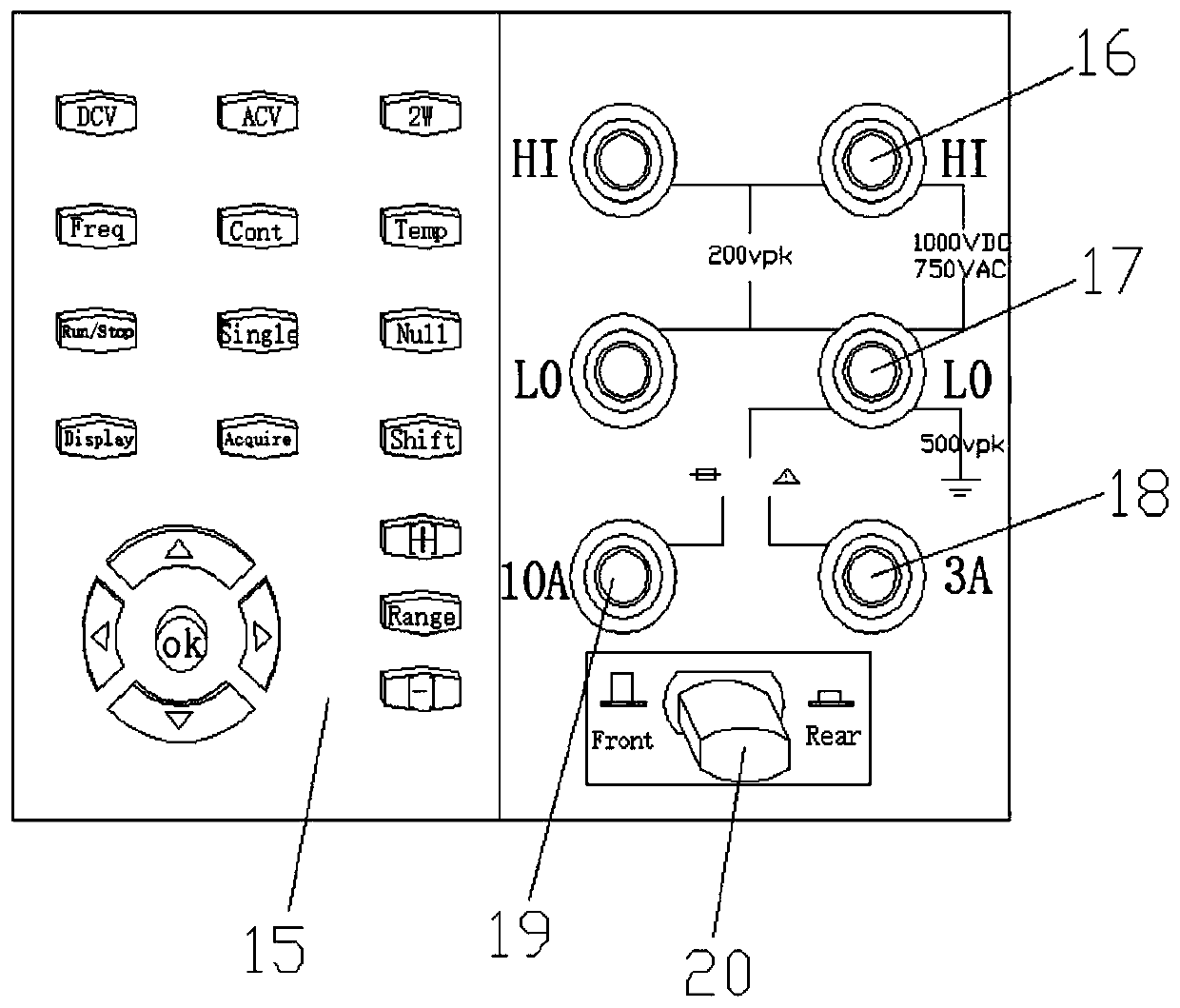

Multimeter and resistance and capacitance measuring method

InactiveCN110456128AAvoid using fatigueReduce read errorsCapacitance measurementsMulti-tester circuitsElectrical resistance and conductanceEngineering

The invention provides a multimeter and a resistance and capacitance measuring method. The multimeter comprises a reference source, an analog switch, a buffer and a one-way module and also comprises an FPGA (field programmable gate array), a controllable current source, a protection module, a gear selection circuit, a resistance measurement circuit, a capacitance measurement circuit and a threshold comparator, wherein the protection module comprises an a-way protection circuit and a b-way protection circuit, the controllable current source receives reference signals sent by the reference source and selects actual measurement object gear according to the gear selection circuit, the FPGA controls to produce corresponding current, the current is outwards output through the a-way protection module, and resistance and capacitance are measured by use of the same circuit.

Owner:QINGDAO HANTEK ELECTRONICS

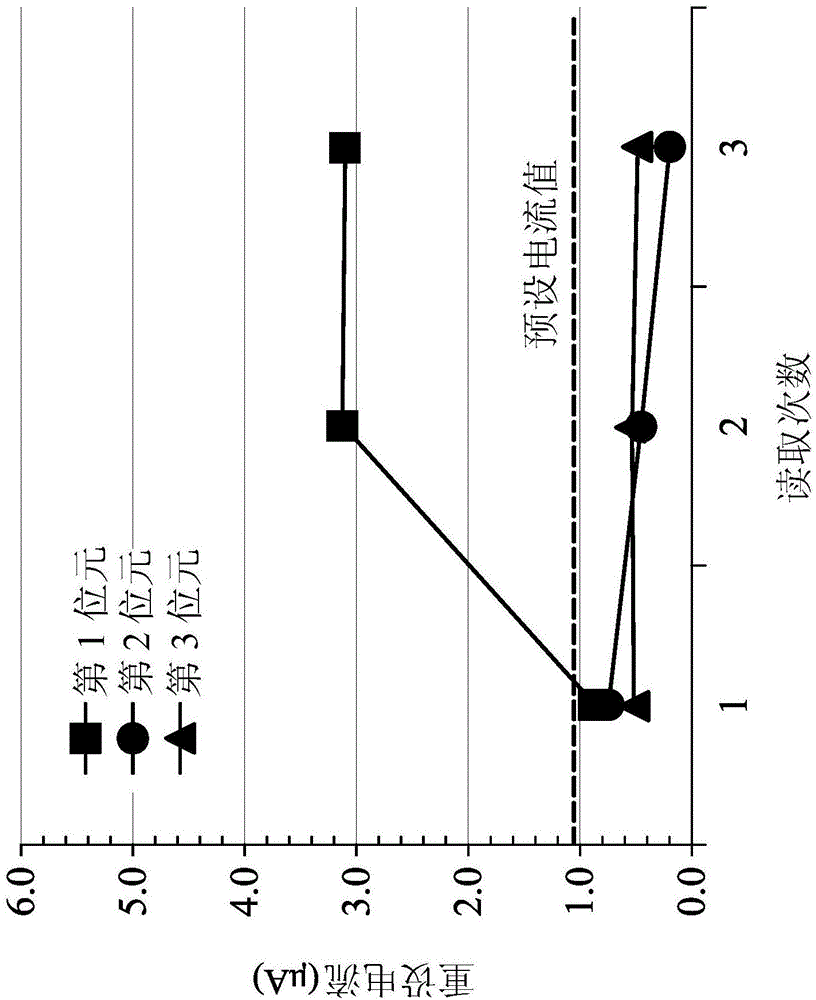

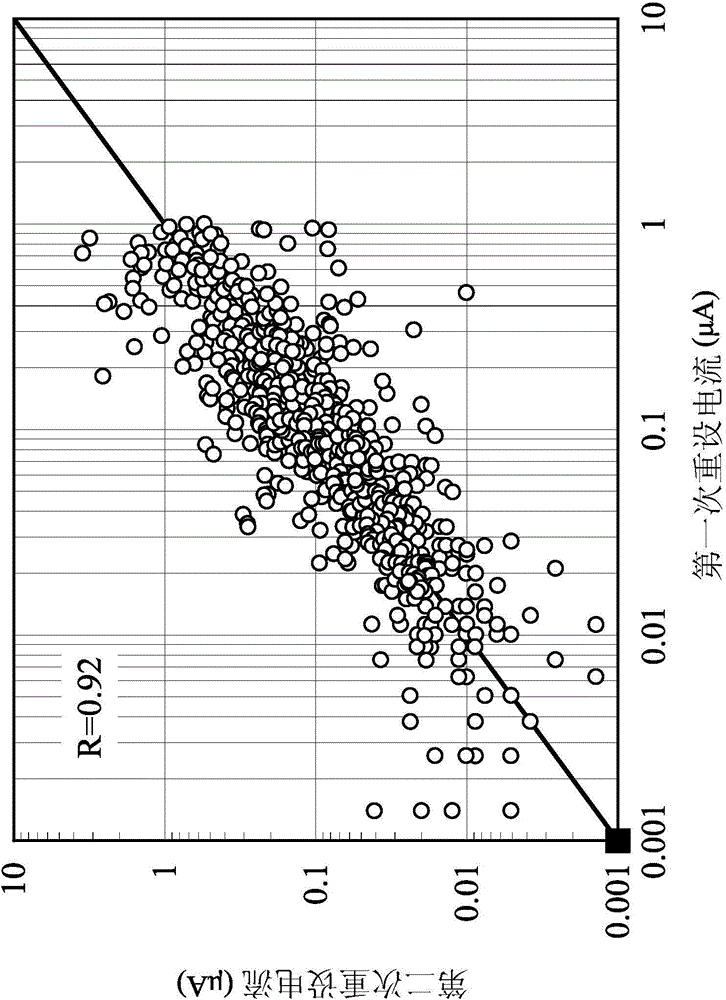

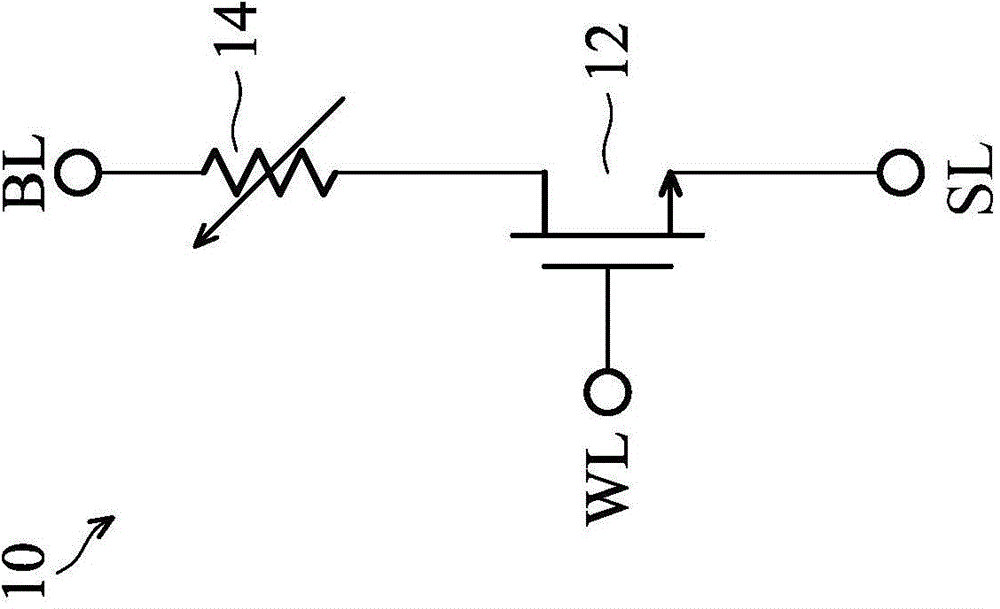

Resistor type random access memory operation method

The present invention provides a resistor type random access memory operation method, which comprises: providing a reset voltage pulse to a resistor type random access memory; providing an emulated voltage pulse to the resistor type random access memory; and providing an acknowledgment voltage pulse to the resistor type random access memory, and reading the reset current of the resistor type random access memory when the acknowledgment voltage pulse is provided, wherein the voltage level of the acknowledgment voltage pulse is greater than the voltage level of the provided reading voltage pulse for reading the resistor type random access memory. With the method of the present invention, the confirmation failure during the reading can be reduced, and the reading stability can be increased.

Owner:WINBOND ELECTRONICS CORP

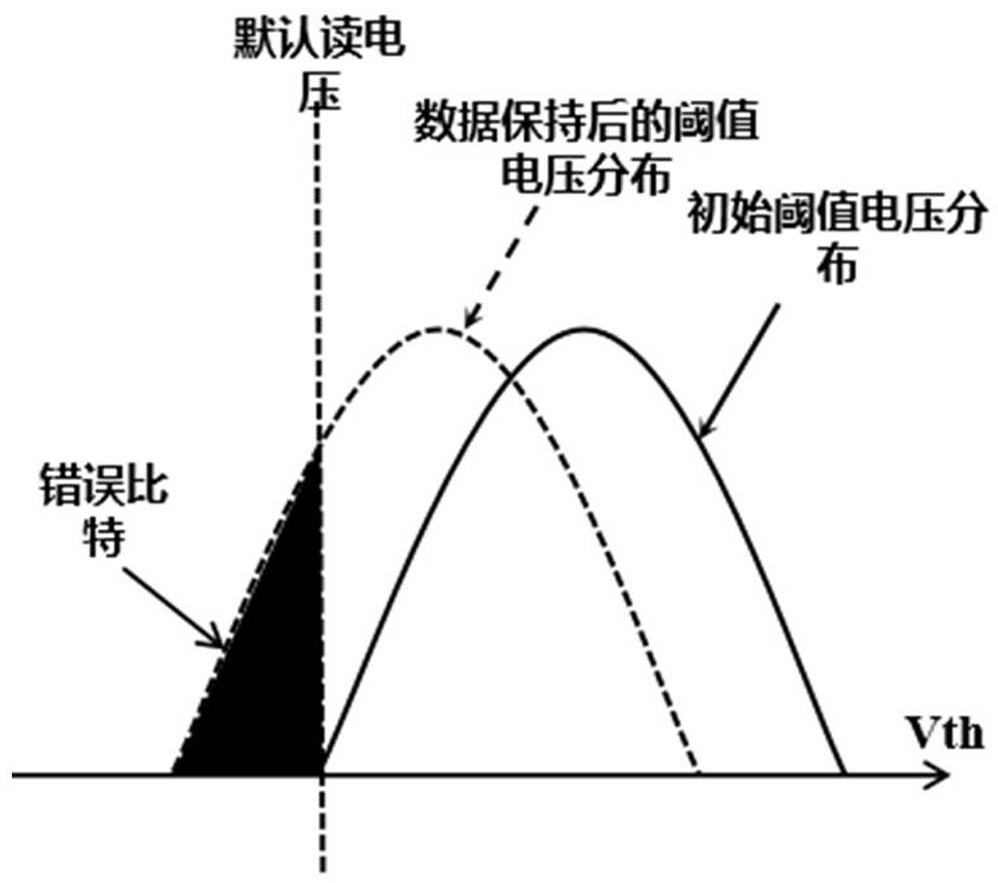

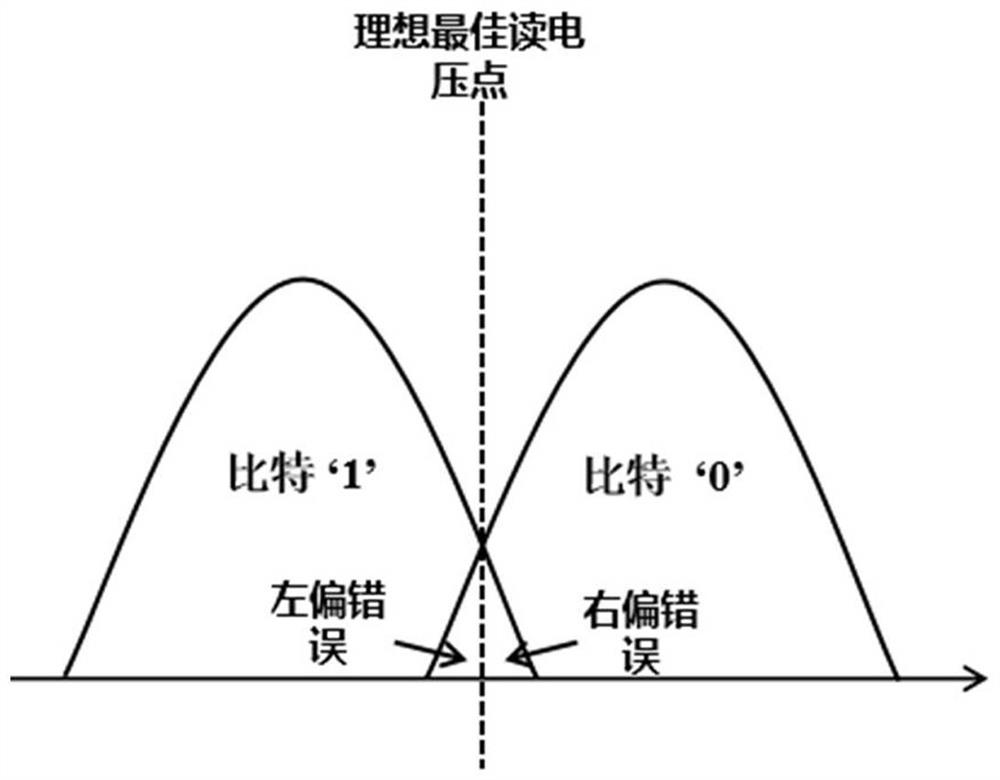

Method for determining optimal read voltage of memory

ActiveCN113192550AReduce biasImprove reliabilityRead-only memoriesEnergy efficient computingEngineeringControl theory

The invention discloses a method for determining optimal read voltage of memory, which comprises the following steps of: firstly, setting an optimal read voltage point as an intersection point of adjacent threshold voltage states of a memory, and defaulting a read voltage point as a read voltage point set when the memory leaves a factory; and then calculating drift distances offset 1 and offset 2 of two adjacent threshold voltage states relative to the initial state, and an offset distance offset = (offset 1 + offset 2) / 2 of the optimal voltage reading point relative to the default voltage reading point, and determining the optimal voltage reading point according to the offset distance and the default voltage reading point. According to the method, the position of the optimal read voltage is determined through fewer read times, so that the read error of the memory is greatly reduced, and the efficiency and reliability of a memory system are improved.

Owner:SHANDONG UNIV

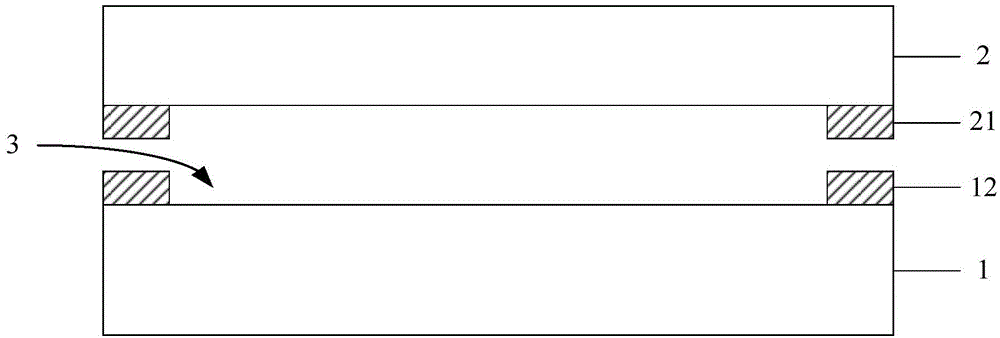

Encapsulating method

InactiveCN104535084AEfficient removalIncrease vacuumGyroscopes/turn-sensitive devicesMicrostructural device manufactureWafer dicingWafer bonding

An encapsulating method comprises the steps that a substrate is formed, a micro mechanical device is arranged in the substrate; a first graphical metal layer is formed on the surface of the substrate; exhaust-gas disposal is carried out on the substrate; a handle wafer is arranged, and a second graphical metal layer is formed on the surface of the handle wafer; the first graphical metal layer of the substrate is correspondingly attached to the second graphical metal layer of the handle wafer to achieve wafer bonding. According to the encapsulating method, the vacuum degree in an encapsulated encapsulating cavity can be effectively improved, therefore the read errors of the device in the encapsulating cavity are reduced, the energy loss of the device is reduced, the stability of the device is improved, the sensitivity of the device is improved, and the quality factor of the device is improved.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

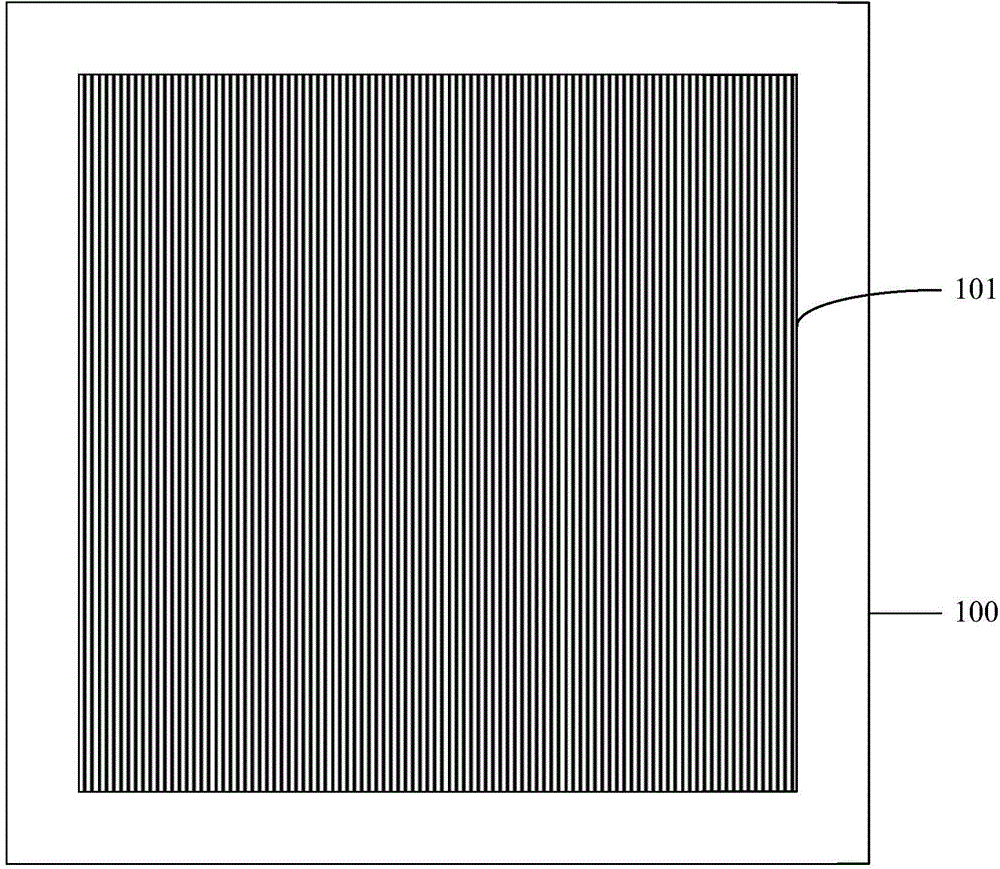

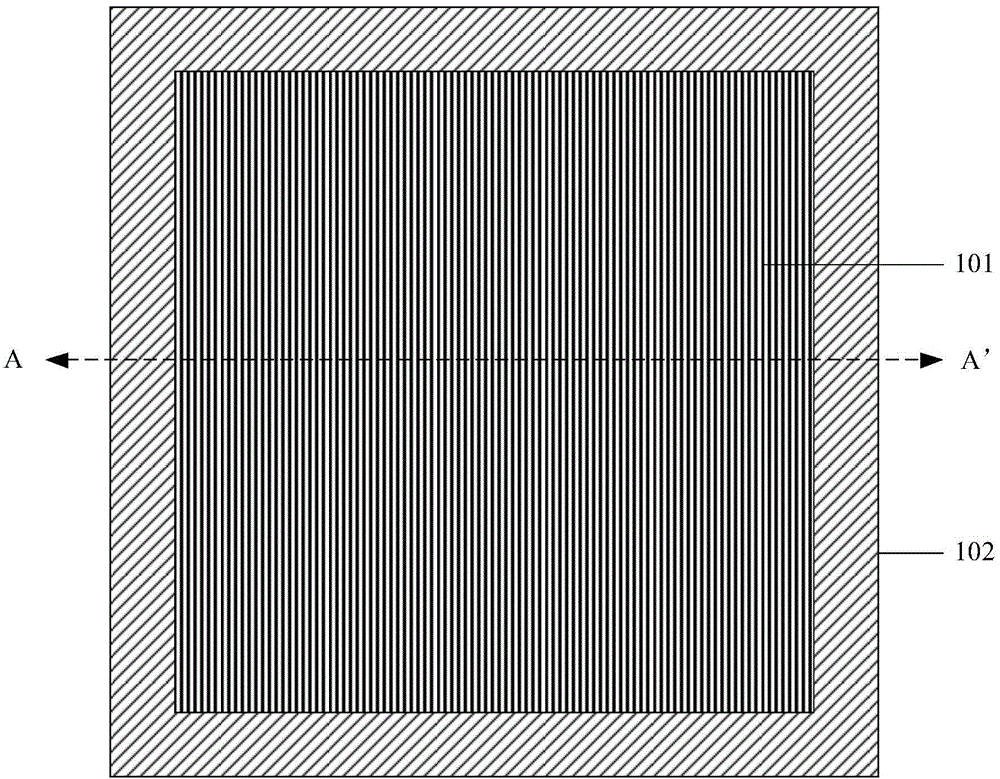

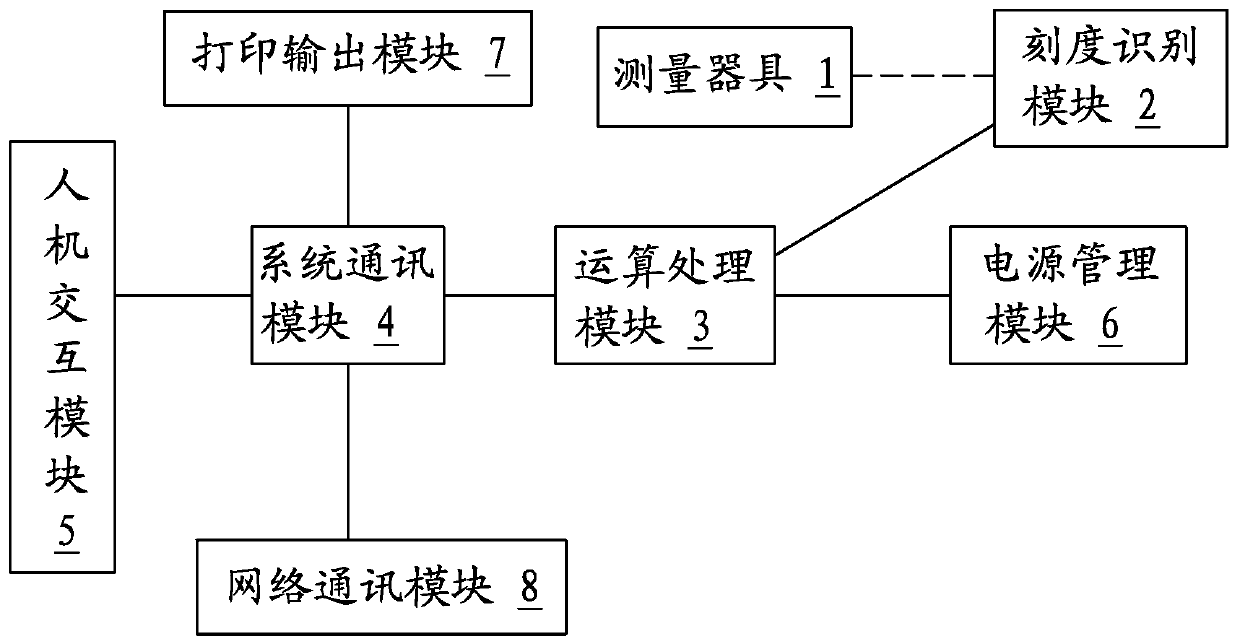

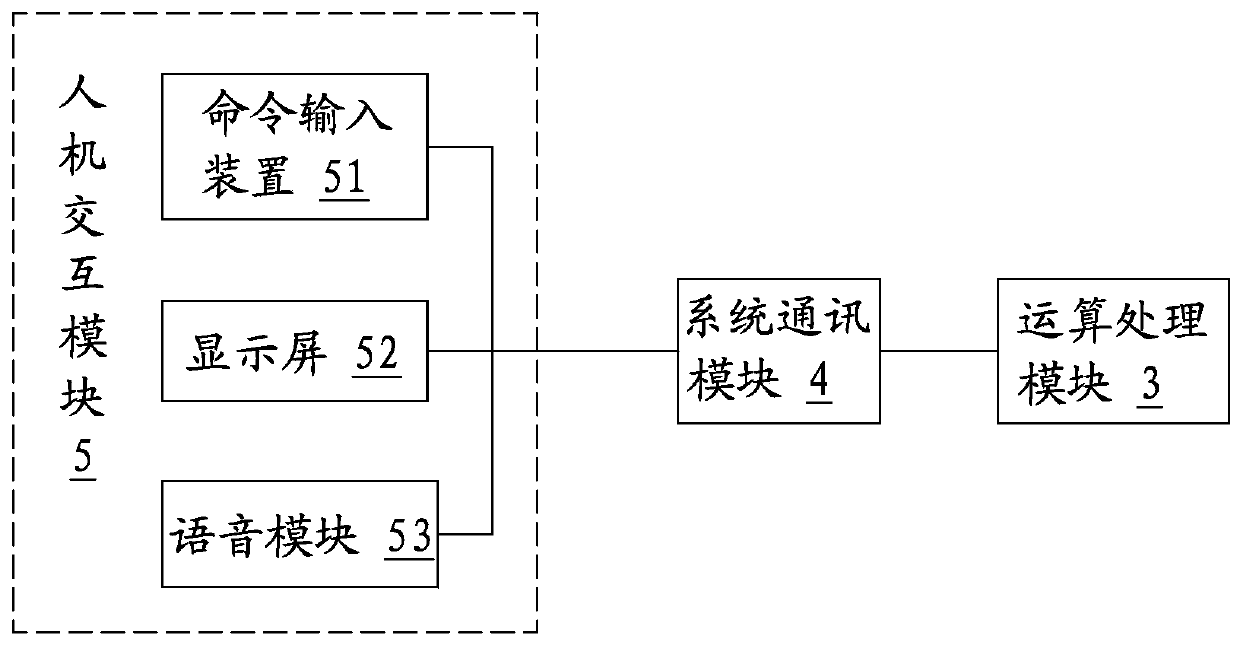

Pelvic organ prolapse measuring system

PendingCN110731781AConvenience to workHigh degree of automationCatheterDiagnostic recording/measuringMeasuring instrumentPelvic organs

The invention provides a pelvic organ prolapse measuring system. The system comprises: a measuring instrument, wherein the measuring instrument comprises a graduated scale body, and the graduated scale body is axially provided with a limiting groove or a limiting hole; a pull rod, wherein the pull rod is inserted into the limiting groove or the limiting hole; a vernier, wherein the vernier is fixedly arranged at the front end of the pull rod, and when the pull rod is stressed, the pull rod drives the vernier to move axially; a scale identification module, wherein the scale identification module is used for acquiring and identifying a scale image of the measuring instrument; and an operation processing module, wherein the operation processing module is connected to the scale identificationmodule, and transmits the identified image data to the operation processing module through the scale identification module. The system has the advantages that: compared with existing manual recordingmodes, the system is high in automation degree and operation efficiency, great convenience can be brought to work of clinical operators, and reading errors can be reduced.

Owner:沈平

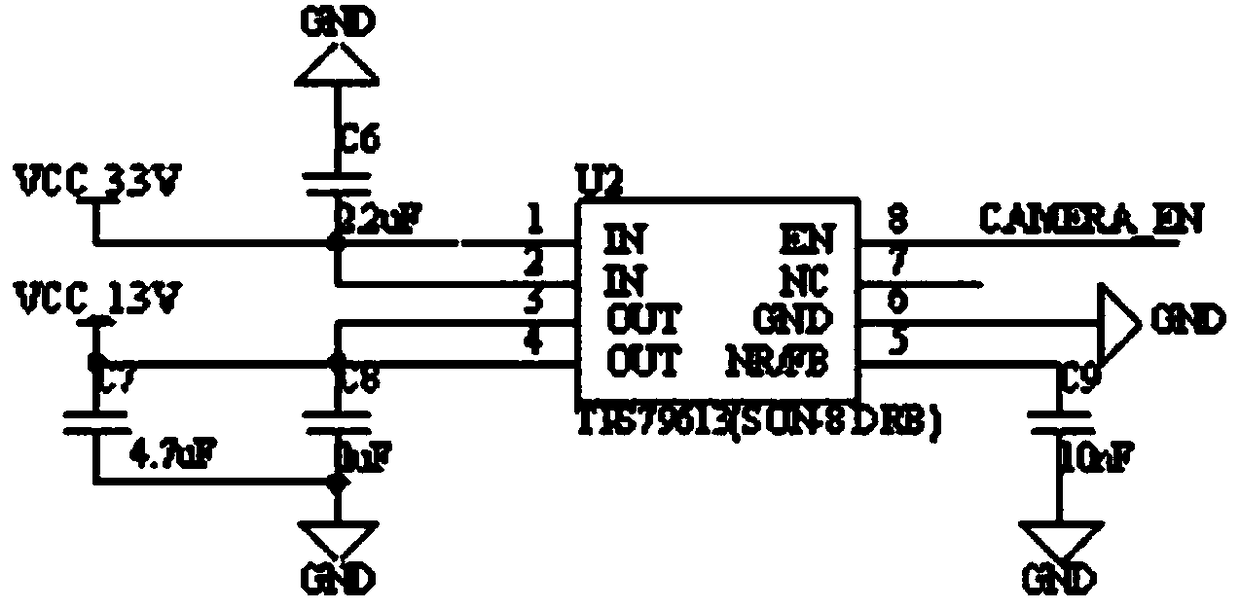

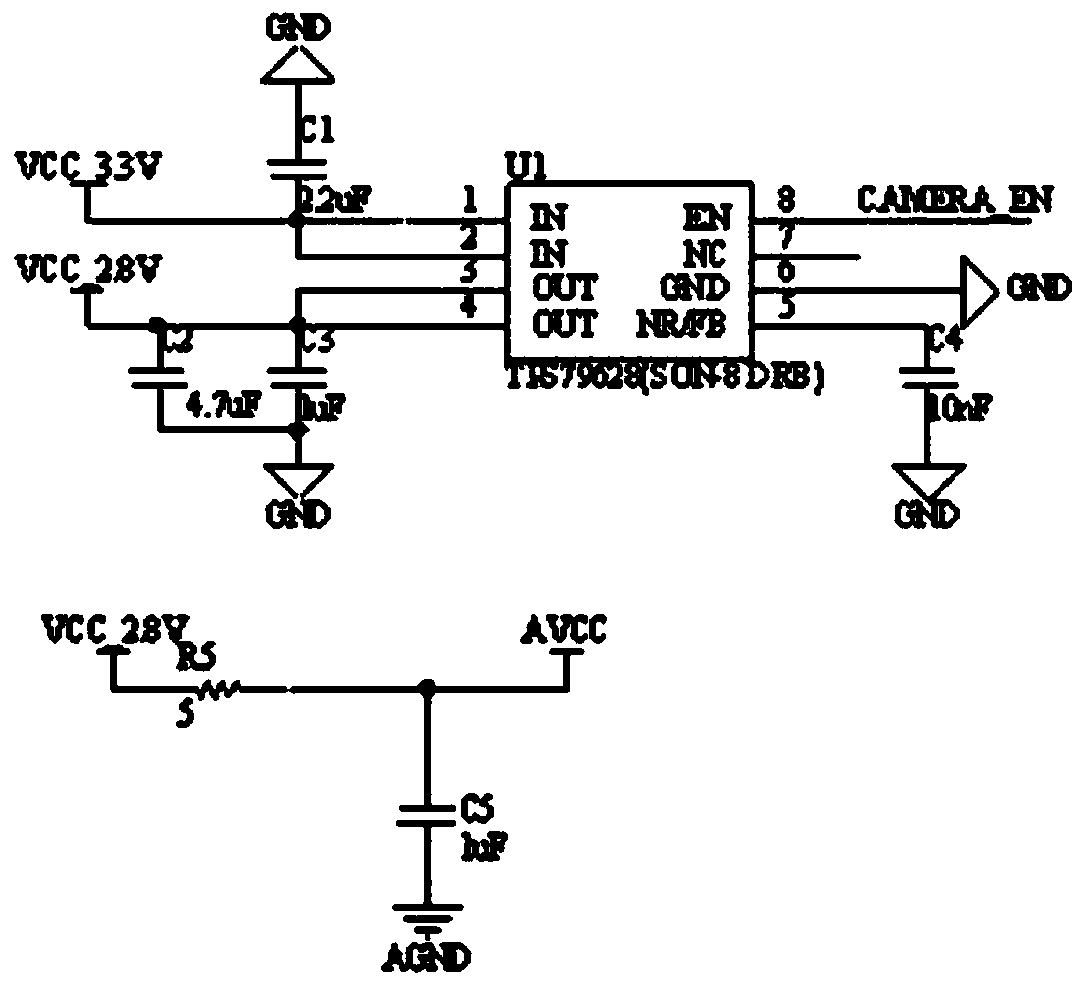

Identifying and reading instrument of lightning arrester instrument of transformer substation

InactiveCN108614175AReduce labor intensityReduce read errorsElectrical testingMeasurement using digital techniquesControl signalTransformer

Provided in the invention is an identifying and reading instrument of a lightning arrester instrument of a transformer substation. The invention relates to an instrument data transmission device, particularly to a transmission device for a measuring value, a control signal or other similar signals so that problems that errors are made frequently and the efficiency is low because only manual monitoring is carried out by the lightning arrester instrument can be solved. The identifying and reading instrument is composed of a main controller, a caching module, a communication module, a human-computer interaction module, a camera module and a camera power supply module. The camera power supply module and the camera module are electrically connected; and the main controller is connected with thecamera module, the camera power supply module, the caching module, the communication module and the human-machine interaction module electrically. Therefore, a problem that the lightning arrester instrument can not transmit data remotely because of lack of a data transmission interface is solved and thus the labor intensity of the staff is reduced. Moreover, the identifying and reading correctionrate is close to the 100 percent, so that the reading error caused by manual reading is reduced and thus the work efficiency is improved.

Owner:国网黑龙江省电力有限公司佳木斯供电公司 +1

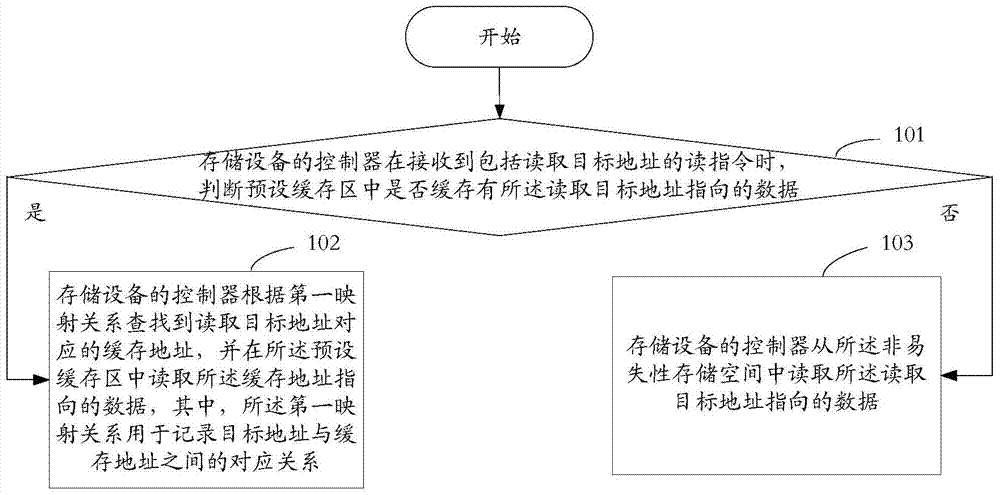

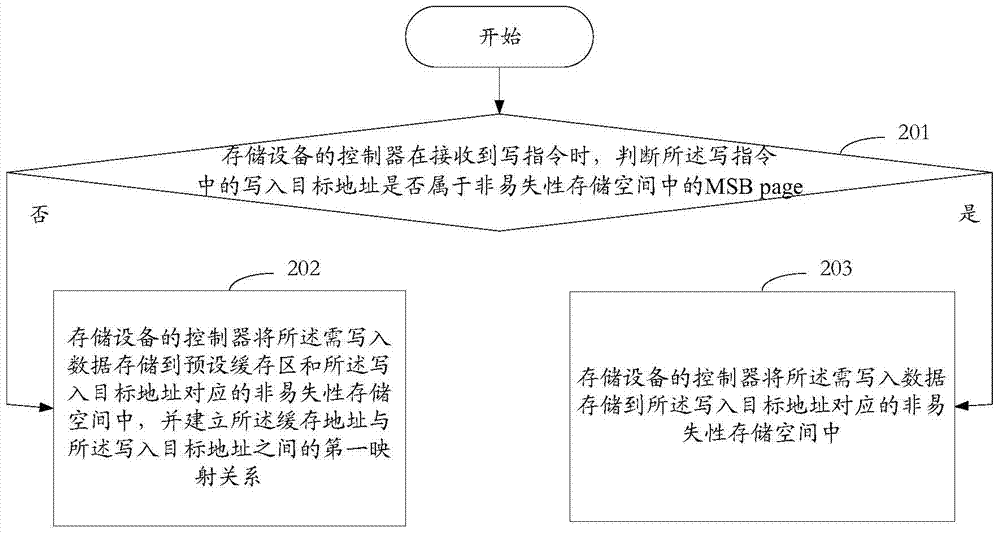

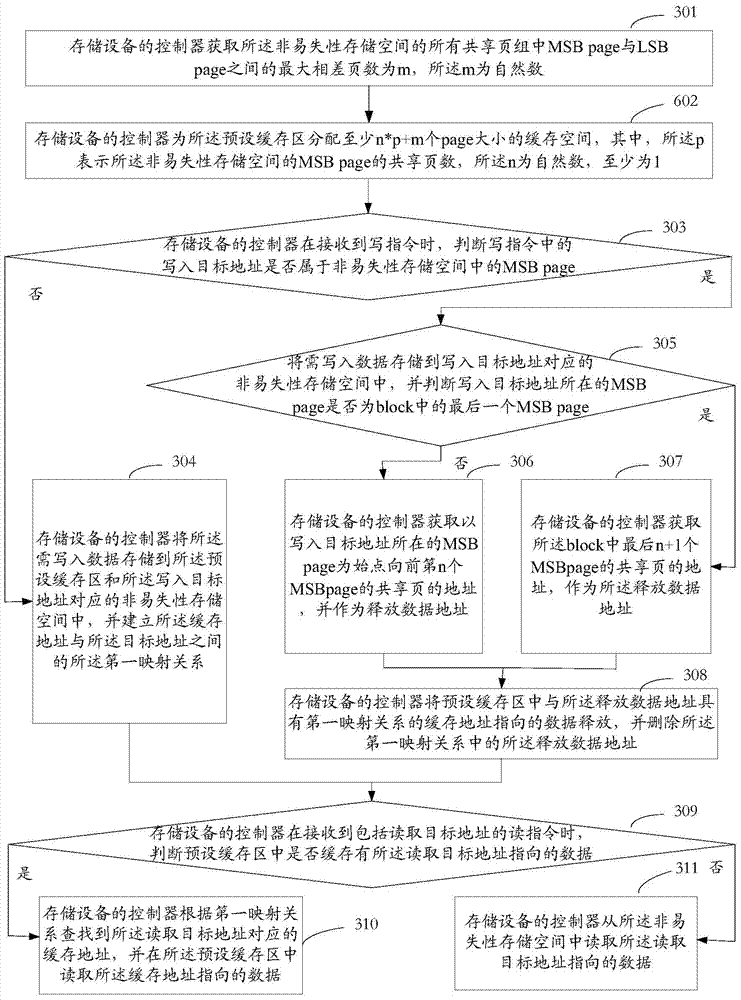

Method and device for reading data

ActiveCN104503707BImprove reliabilityReduce read errorsMemory architecture accessing/allocationInput/output to record carriersOperating systemData point

The present application discloses a method and device for reading data, wherein, the method includes: when receiving a read command including a read target address, judging whether the read target address points to a cache in the preset buffer area If there is, find the cache address corresponding to the read target address according to the first mapping relationship, and read the data pointed to by the cache address in the preset cache area, wherein the first The mapping relationship is used to record the corresponding relationship between the target address and the cache address; if not, read the data pointed to by the read target address from the non-volatile storage space. Through the above manner, errors in reading data caused by write interference can be reduced.

Owner:HUAWEI TECH CO LTD

METHODS for forming semiconductor structures

InactiveCN111129065AReduce read errorsSuppress read errorsMagnetic-field-controlled resistorsSolid-state devicesMemory cellRemote plasma

Methods for forming semiconductor structures and methods of forming magnetic tunnel junction (MTJ) memory cells used in a magneto-resistive random access memory (MRAM) array are provided. A pre-cleanprocess is performed to remove a metal oxide layer that may form on the top surface of the bottom electrodes of MTJ memory cells during the time the bottom electrode can be exposed to air prior to depositing MTJ layers. The pre-clean processes may include a remote plasma process wherein the metal oxide reacts with hydrogen radicals generated in the remote plasma.

Owner:TAIWAN SEMICON MFG CO LTD

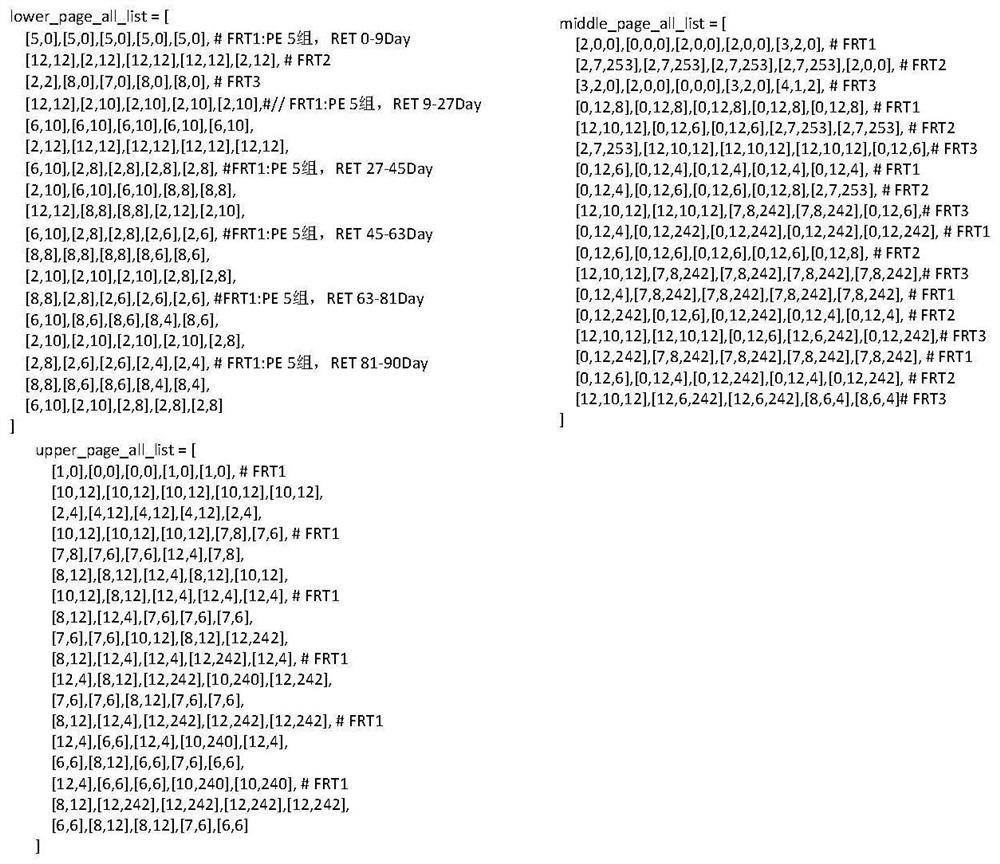

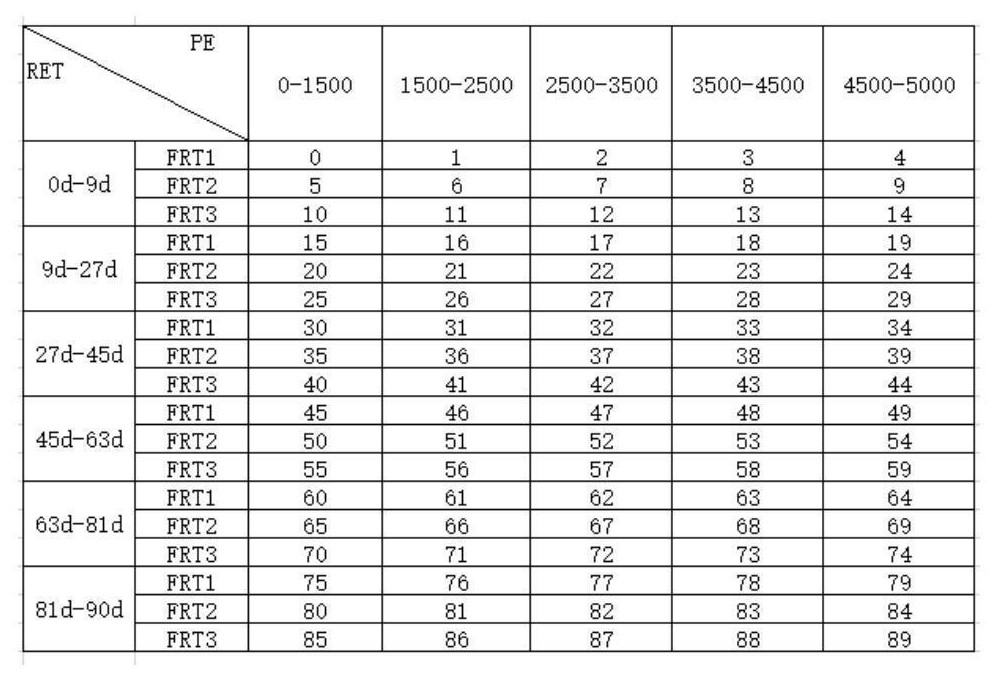

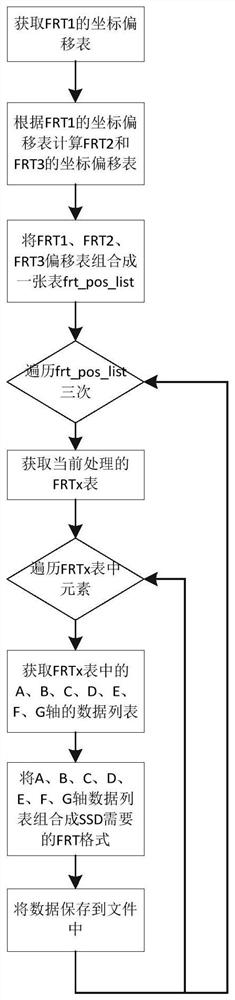

Method and device for acquiring FRT table in solid state disk

PendingCN114496049AReduce read errorsImprove accuracyStatic storageOriginal dataSoftware engineering

The invention provides a method for obtaining an FRT table in a solid state disk, which comprises the following steps: processing FRT original data, summarizing FRT data obtained by NAND test into a lower page all list, a middle page all list and an upper page all list for representing A, B, C, D, E, F and G axis data, and the lower page all list comprises three groups of data of FRT1, FRT2 and FRT3; acquiring data position offset tables of the FRT1, the FRT2 and the FRT3; extracting A-axis data, B-axis data, C-axis data, D-axis data, E-axis data, F-axis data and G-axis data from the FRT original data table; and recombining the FRT table, recombining the extracted A, B, C, D, E, F and G axis data, and storing the generated data in a file. According to the method, the FRT table applied to the SSD firmware is finally obtained by performing script analysis on the offset voltmeter obtained by the NAND test, and the FRT table is applied to the SSD firmware, so that the occurrence of read errors is greatly reduced.

Owner:SHANDONG YUNHAI GUOCHUANG CLOUD COMPUTING EQUIP IND INNOVATION CENT CO LTD

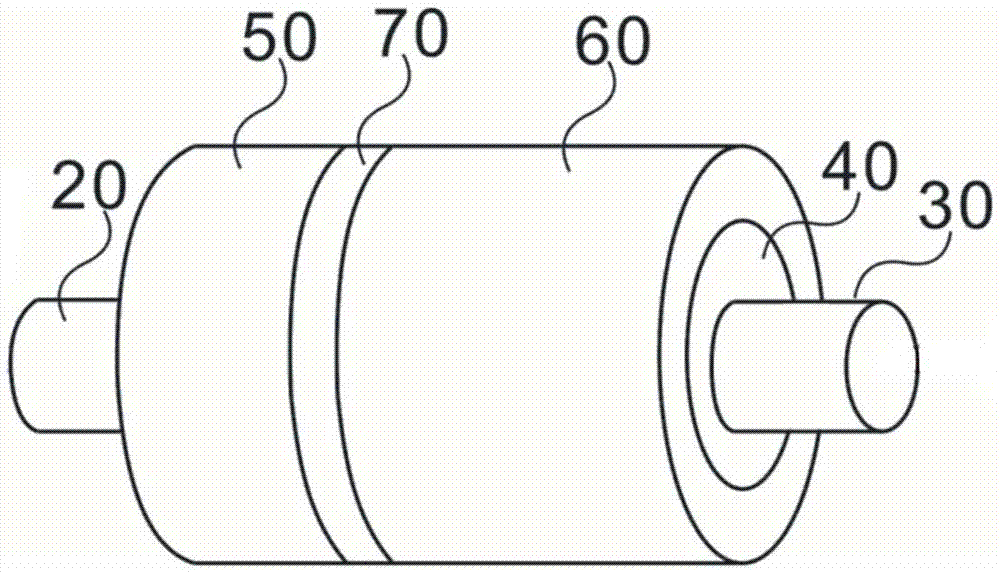

A flash memory device and programming method thereof

ActiveCN104637537BReduce read errorsIncrease storage capacityRead-only memoriesLow voltageContact line

The invention provides a flash memory device and a programming method thereof. The flash memory device comprises a substrate, wherein the substrate is of a cylindrical structure; a source end and a drain end are respectively arranged at the end parts of the substrate; a grid is coats the middle of the substrate; a first insulating layer is arranged between the grid and the substrate; the grid comprises a control grid and a floating grid parallel to each other; and contact lines are respectively led out of the two ends and are used for applying voltage to the substrate. According to the programming method of the flash memory device, by utilizing a back grid bias assisted hot electron generating mechanism, low voltage can be applied to the drain end, the key size of a split floating grid flash memory is effectively shortened, and the cell density of a flash memory array is increased, namely the memory capacity and density of the flash memory are increased. The movement of hot electrons is assisted by applying bias voltage, enough energy crossing an oxide layer is provided so as to finish compiling, the compiling efficiency of the flash memory is improved, and the compiling current power consumption is reduced.

Owner:SHANGHAI HUALI MICROELECTRONICS CORP

A floating gate flash memory device and programming method thereof

ActiveCN104377248BReduce the numberShorten the acceleration distanceTransistorSolid-state devicesComputer architectureParallel computing

The invention provides a floating gate flash memory device and a programming method. The floating gate flash memory device includes a substrate in a cylindrical structure, and the two ends of the substrate are respectively a source end and a drain end; the gate is coated on the substrate In the middle part, a gate oxide layer is provided between the gate and the substrate, and the gate includes a parallel control gate and a floating gate. The programming method of the floating gate flash memory device provided by the present invention assists the movement of hot electrons by applying a bias voltage, provides enough energy to cross the gate oxide layer to complete the compilation, improves the compilation efficiency of the flash memory, and reduces the compilation current power consumption; in addition, the present invention The invention can also effectively shorten the key size of the floating gate flash memory with column gate and increase the cell density of the flash memory array, that is, increase the storage capacity and density of the flash memory.

Owner:SHANGHAI HUALI MICROELECTRONICS CORP

A kind of Sonos flash memory device and compiling method thereof

ActiveCN104332471BReduce read errorsReduce critical sizeSolid-state devicesSemiconductor devicesSilicon oxideEngineering

The invention provides a SONOS flash memory device and a compiling method. The SONOS flash memory device includes a substrate in a cylindrical structure and a gate covering the middle part of the substrate; the ends on both sides of the substrate are respectively a source end and a drain end. , the gate includes a parallel first silicon gate and a second silicon gate, and a first oxide layer is provided between the first silicon gate and the second silicon gate; wherein, the second silicon gate and the substrate include in turn: A second oxide layer disposed on the substrate, a silicon nitride layer disposed on the second oxide layer for storing charges, and a third oxide layer disposed on the silicon nitride layer. The structure can suppress the short-channel effect, resist threshold voltage drift, and effectively shorten the critical size of the flash memory device. The programming method of the flash memory device in the present invention assists the movement of hot electrons by adjusting the voltage of the gate and the drain, provides enough energy to cross the oxide layer to complete the compilation, improves the compilation efficiency of the flash memory, and reduces the compilation current power consumption.

Owner:SHANGHAI HUALI MICROELECTRONICS CORP

A method and system for selecting physical blocks of 3D flash memory

ActiveCN106021123BGuaranteed correctnessReduce workloadMemory adressing/allocation/relocationWorkloadSelection system

The invention is suitable for the technical field of storage and provides a selection method and a selection system for physical blocks of a 3D flash memory. The selection method comprises the following steps of confirming whether data can be written in a physical page of a latest physical block corresponding to a logic address of a writing operation instruction or not when the writing operation instruction is received; if the data cannot be written in the physical page, determining a blank physical block with the best performance from a blank physical block group of the 3D flash memory; and writing the data in the blank physical block with the best performance. According to the selection method, the performance of each blank physical block is considered in a data writing process, so that the generation of writing errors and read errors can be reduced, the data correctness can be ensured to the maximum extent, and the workload of ECC (Error Correcting Code) error correction is reduced.

Owner:SHENZHEN UNIV

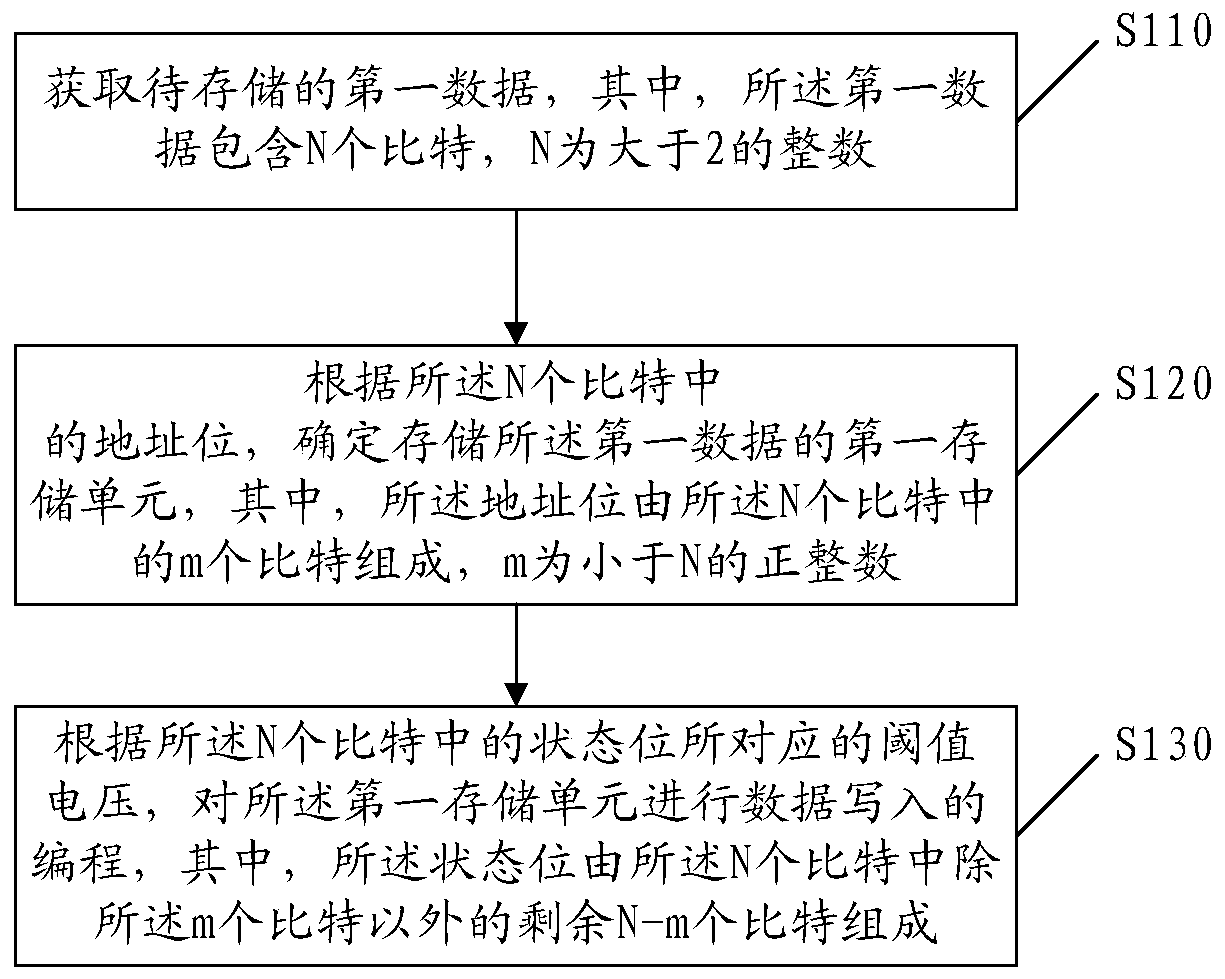

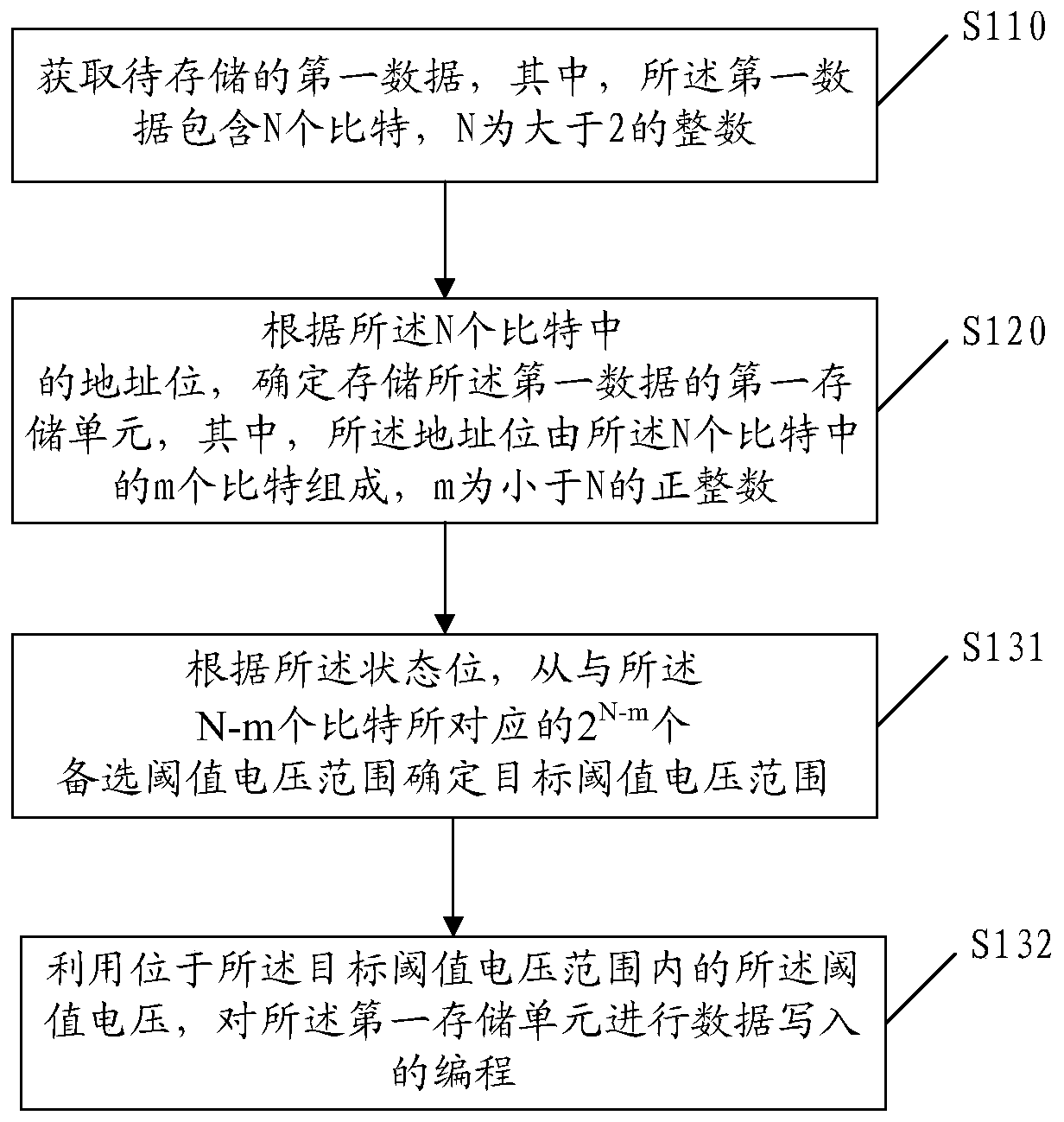

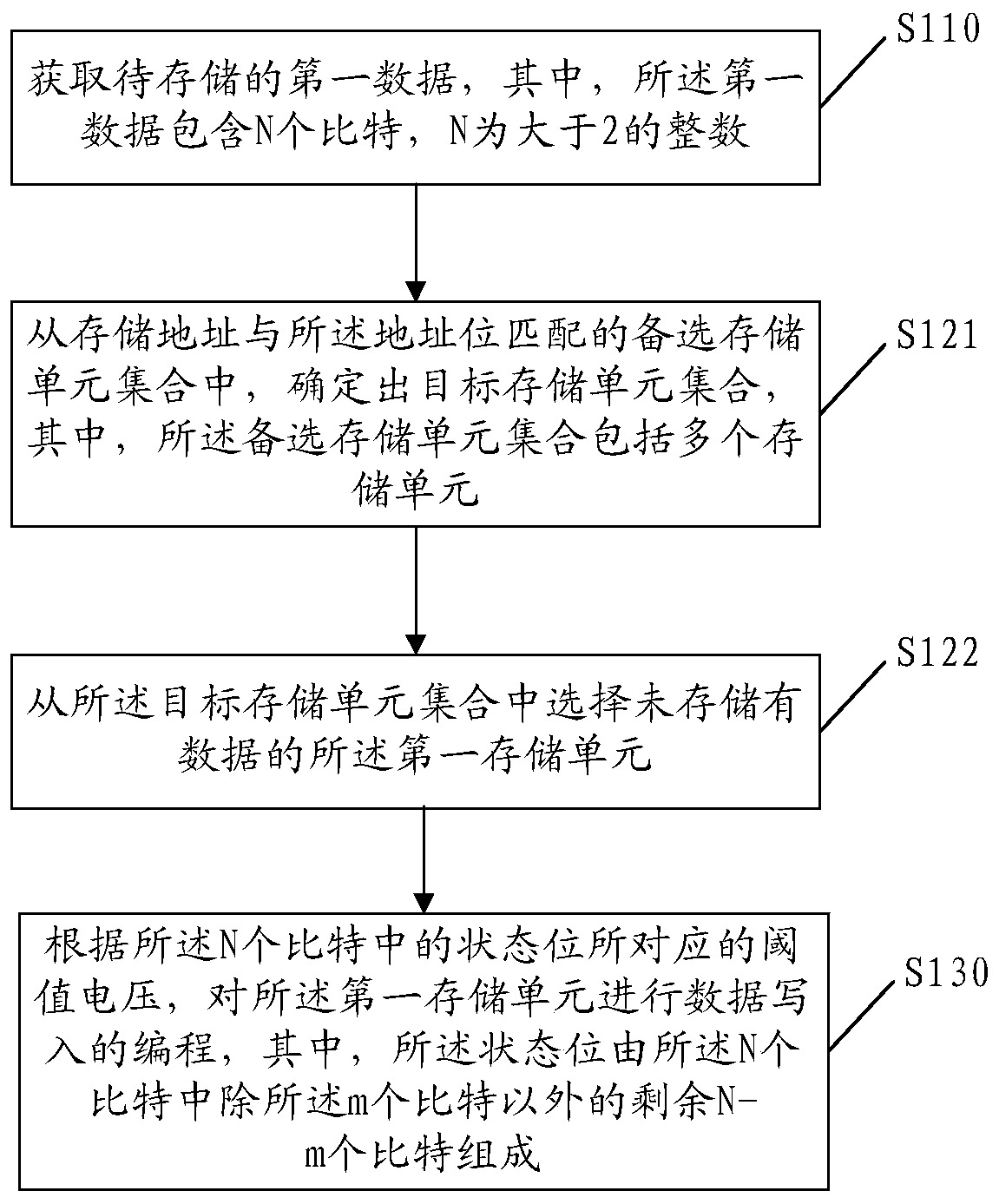

Data reading method and device, memory and storage medium

ActiveCN109935265AImprove reliabilityReduce read errorsRead-only memoriesComputer hardwareStorage cell

The embodiment of the invention discloses a data reading method and device, a memory and a storage medium. The data programming method comprises the steps of obtaining a reading address of data reading; According to the read address, determining an address bit, wherein the address bit is composed of m bits, and m is a positive integer; reading the status bit from the second storage unit corresponding to the read address by using the read voltage corresponding to the N-m bits, Wherein the status bit is composed of N-m bits, the N is a positive integer greater than 2 and the m is a positive integer smaller than N; And combining the address bit and the state bit to obtain second data required to be read.

Owner:YANGTZE MEMORY TECH CO LTD

A data storage method and storage system

ActiveCN106021124BGuaranteed correctnessReduce workloadMemory adressing/allocation/relocationComputer hardwareWorkload

Owner:SHENZHEN UNIV