A kind of Sonos flash memory device and compiling method thereof

A flash memory device and substrate technology, applied in the direction of electric solid-state devices, semiconductor devices, electrical components, etc., can solve the problems of high current consumption, low efficiency of channel hot electron injection, and high voltage, so as to increase cell density, Effect of suppressing short channel effect and reducing readout errors

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

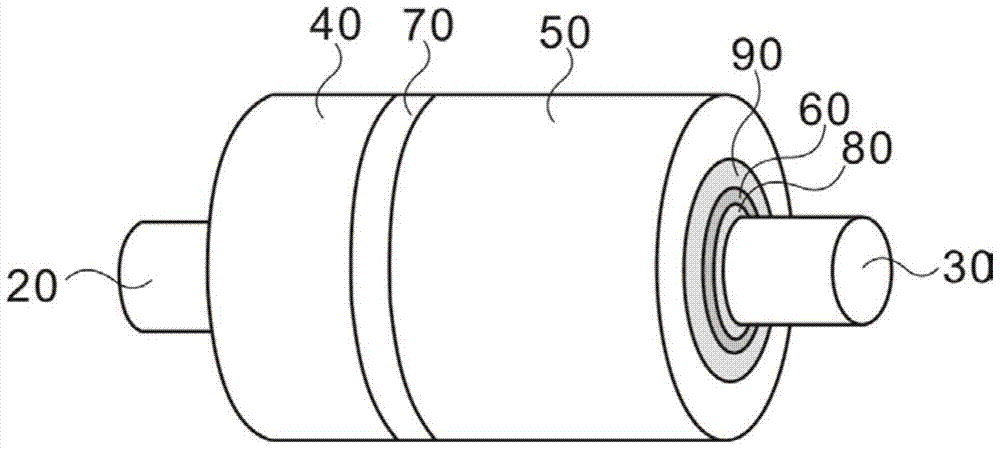

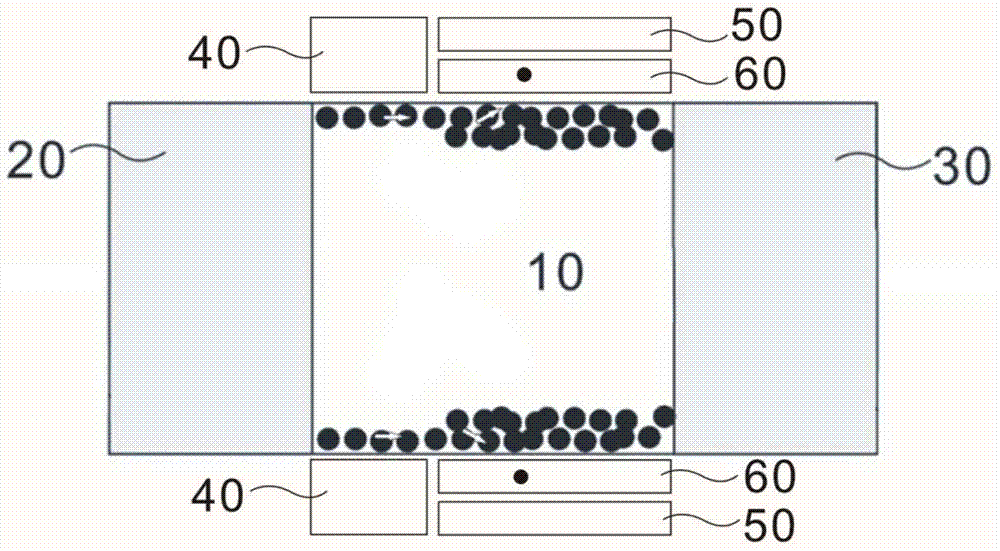

[0029] In this embodiment, the material of the first silicon gate 40 is polysilicon, its height is 90nm, and its length is 10nm; the material of the second silicon gate 50 is polysilicon, its height is 30nm, its length is 40nm; The material of the second oxide layer 80 is silicon dioxide with a thickness of 2 nm; the material of the third oxide layer 90 is silicon dioxide with a thickness of 8 nm. The manufacturing process of the device can be selected from the top-down technology compatible with the standard CMOS process.

[0030] In the SONOS flash memory device provided by the present invention, a cylindrical substrate structure is used, and the gate is covered on it. The use of a cylindrical structure can enable the voltage of the gate to better control the channel and suppress the short channel effect. , resist threshold voltage drift, reduce readout errors of flash memory, and at the same time, can effectively shorten the critical size of flash memory devices, increase t...

Embodiment 2

[0033] In this embodiment, when compiling the SONOS flash memory device, the voltage value applied to the first silicon gate 40 is equal to the threshold voltage value of the flash memory device, the voltage applied to the second silicon gate 50 is 8V, and the voltage applied to the drain terminal 30 is 4V. A voltage of 0V is applied to the source terminal 20 .

[0034] The compiling principle of the present invention is: when compiling a SONOS flash memory device, the voltage value applied to the first silicon gate 40 is equal to the threshold voltage value of the flash memory device, and a thinner channel electron layer is induced in the lower substrate region. The voltage applied to the second silicon gate 50 is greater than the threshold voltage of the flash memory device, and the voltage is coupled to the underlying silicon nitride layer 60 to induce a thicker channel electron layer in the lower channel electron layer. The voltage applied to the drain terminal 30 accelera...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More