Patents

Literature

71results about How to "Reduce critical size" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

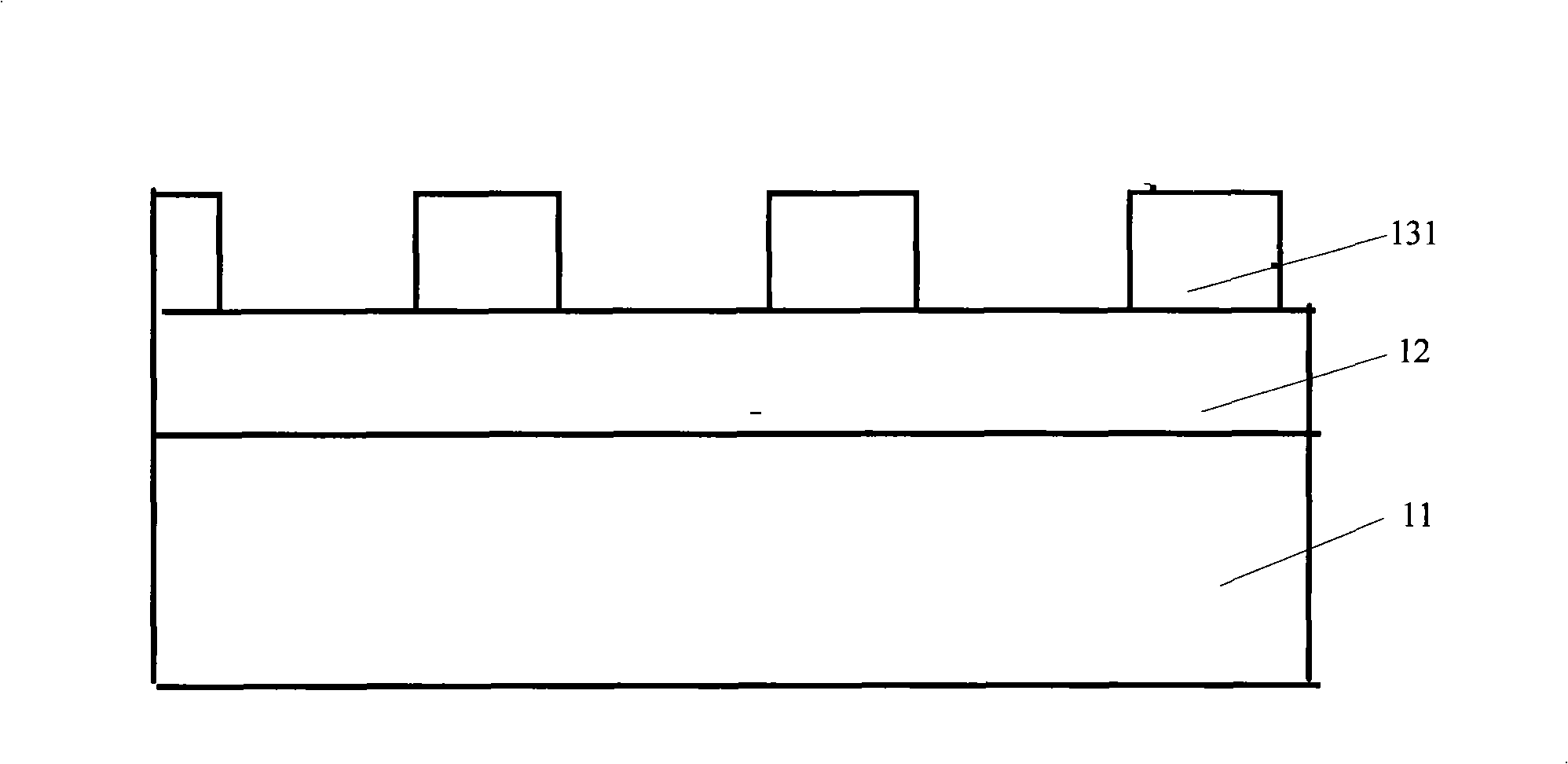

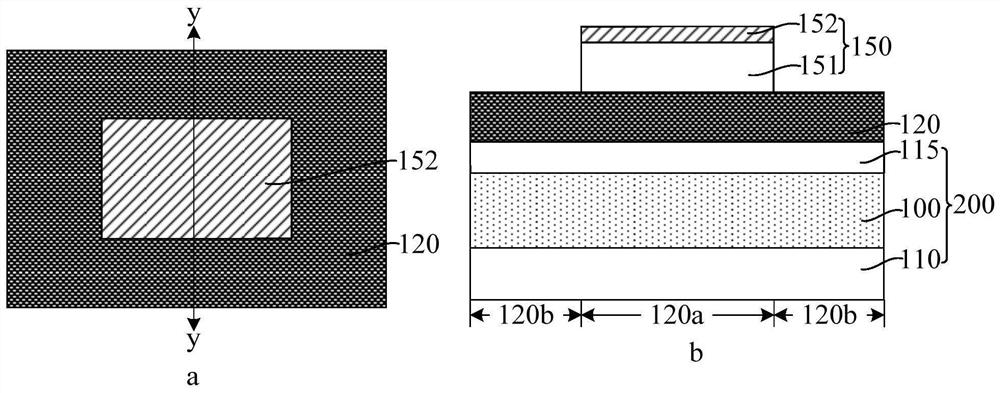

Method for decreasing critical size of copper-connection groove

InactiveCN103346119AImprove performanceReduce critical sizeSemiconductor/solid-state device manufacturingIntegrated circuit manufacturingPlasma deposition

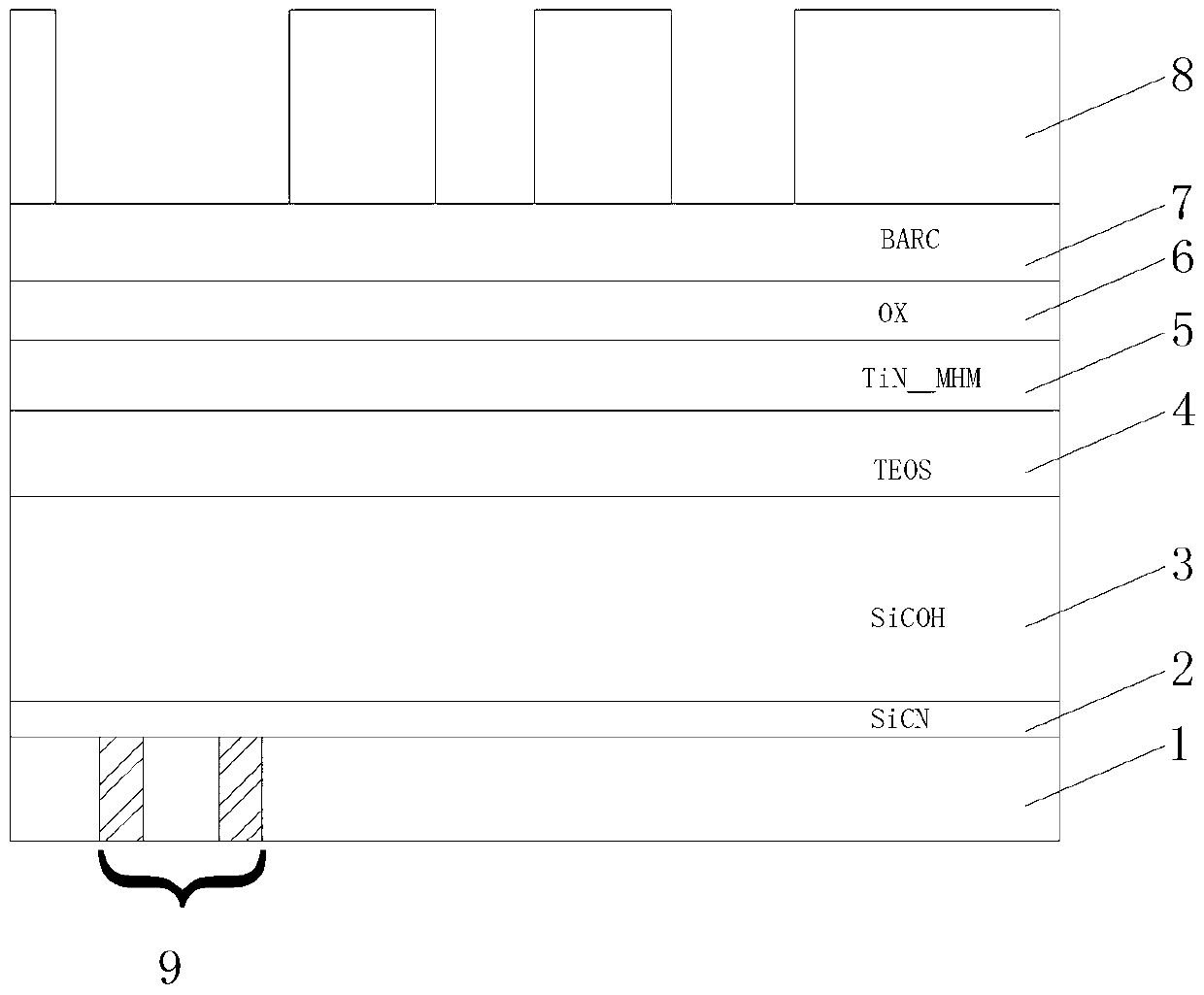

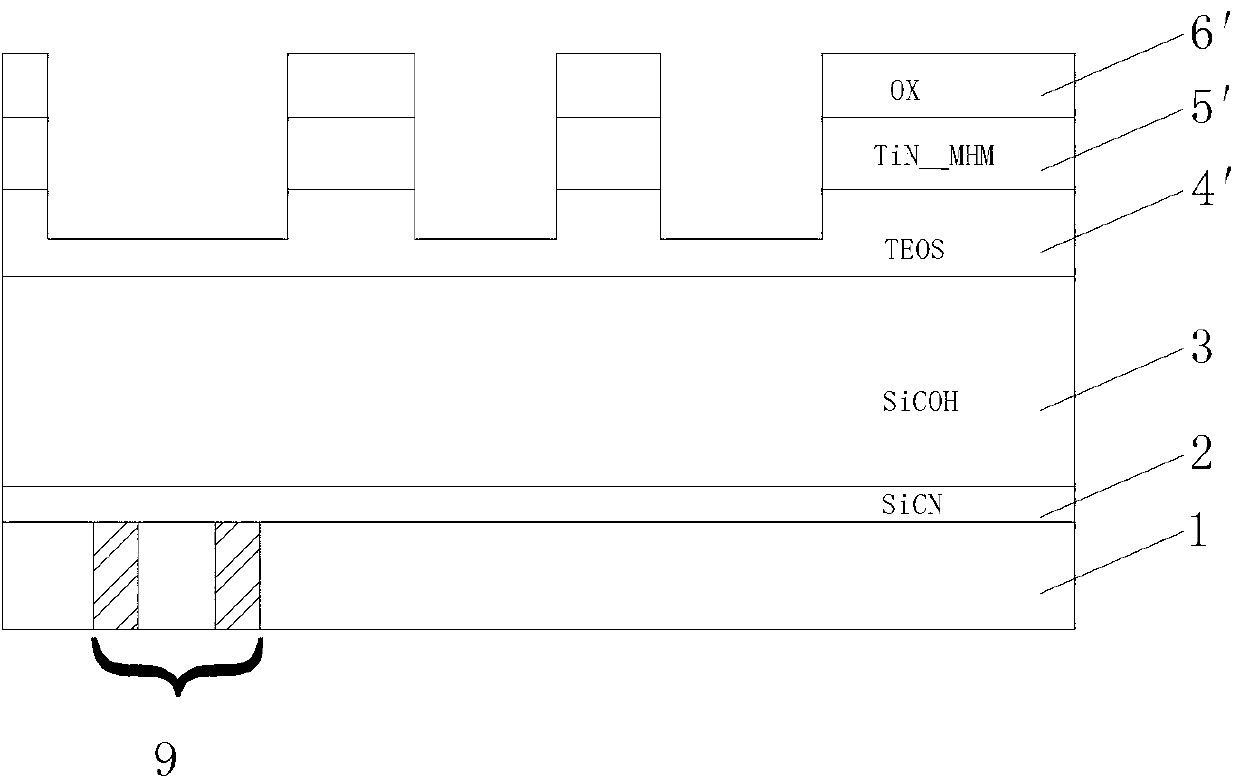

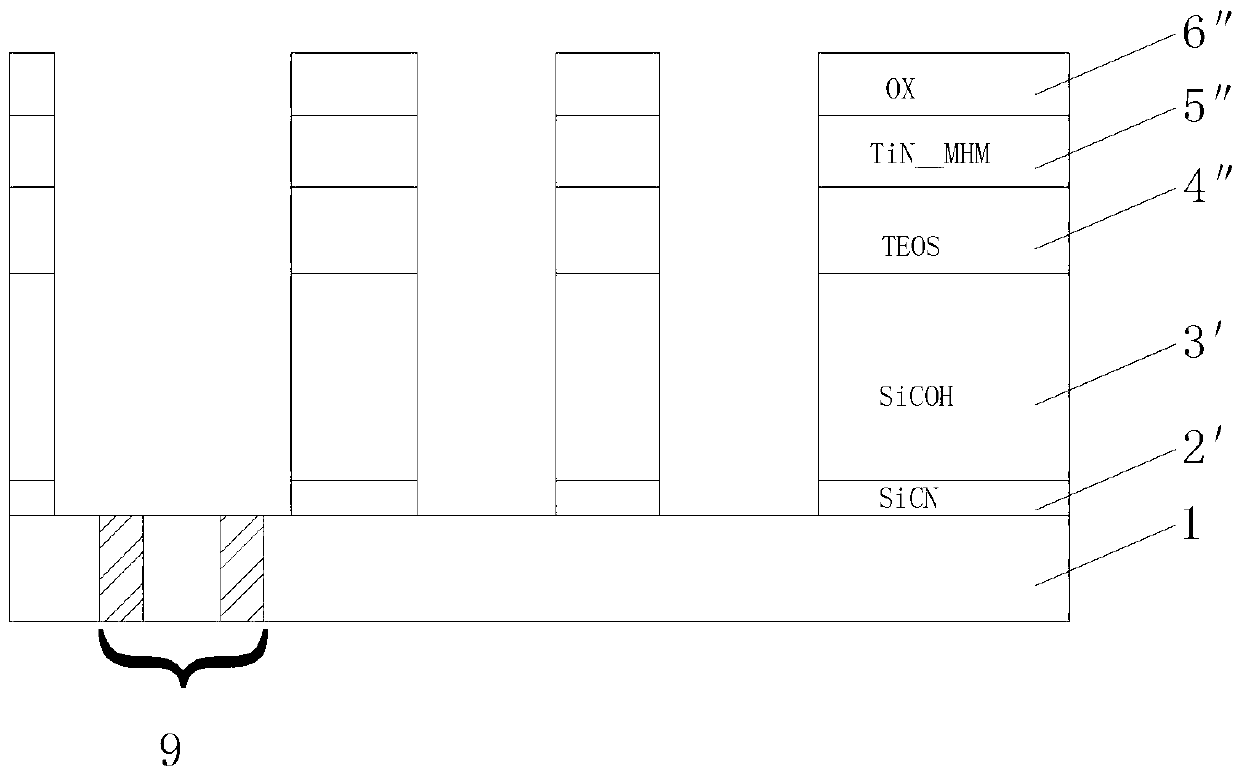

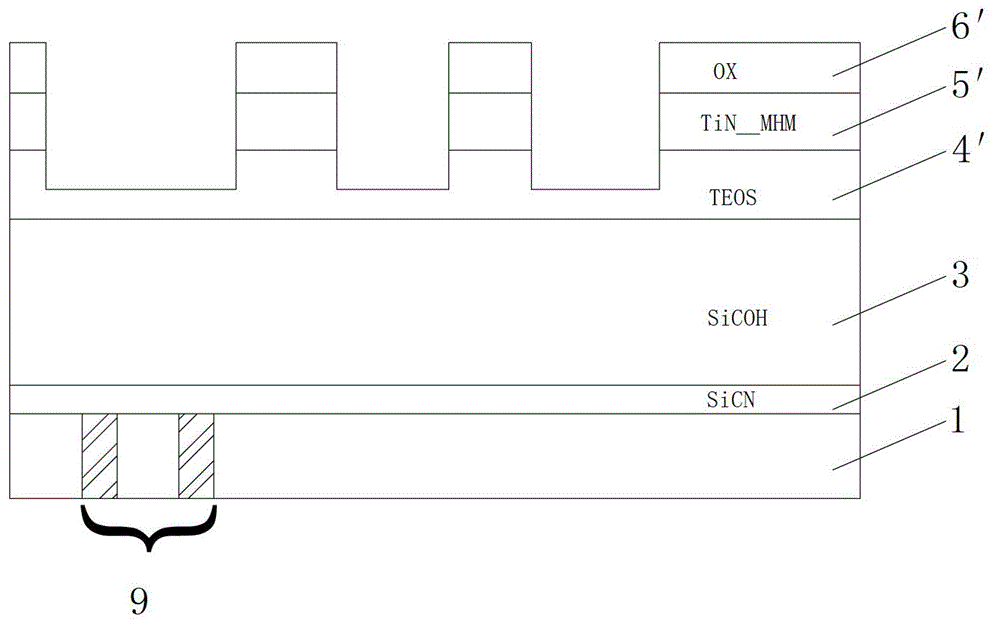

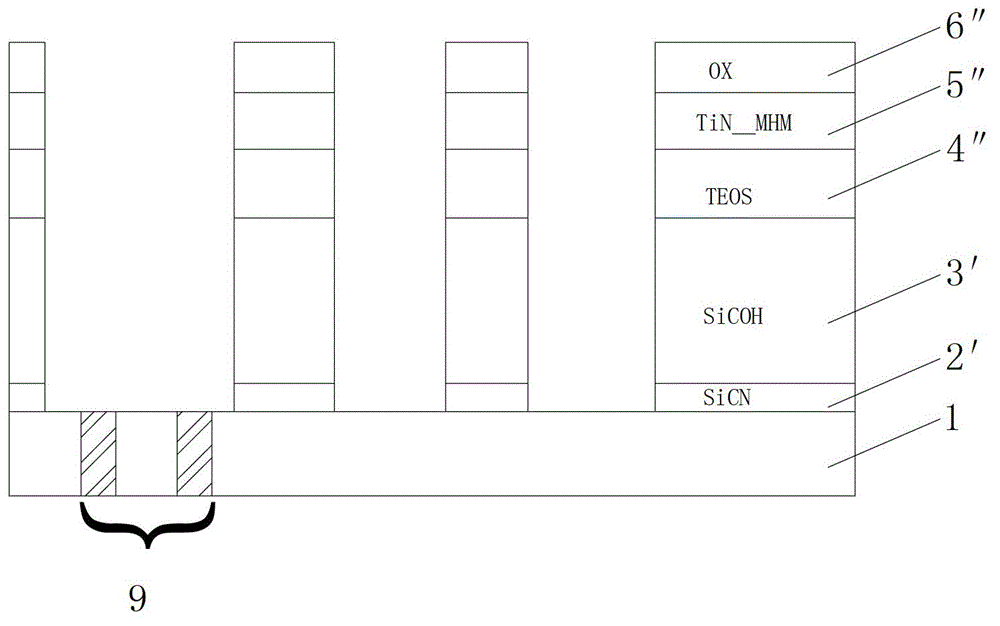

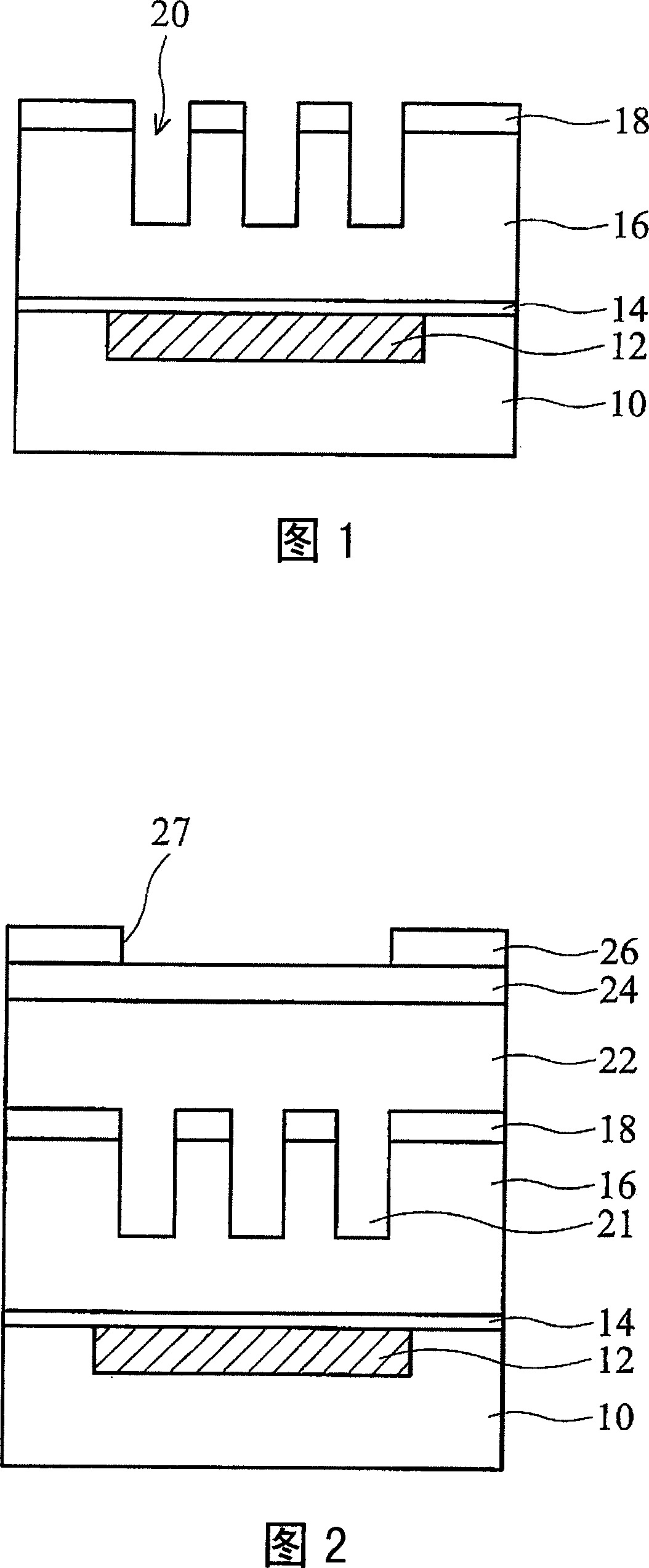

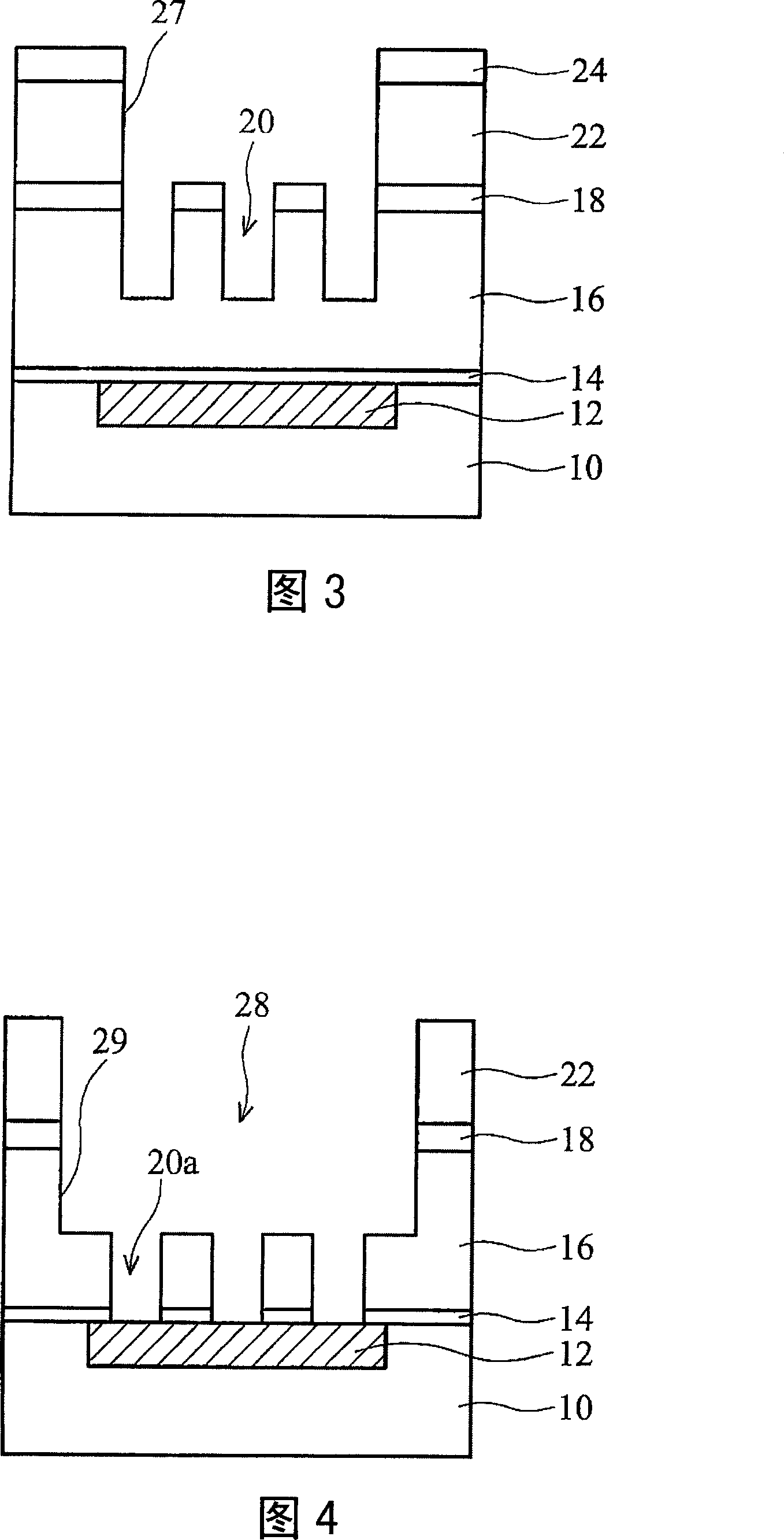

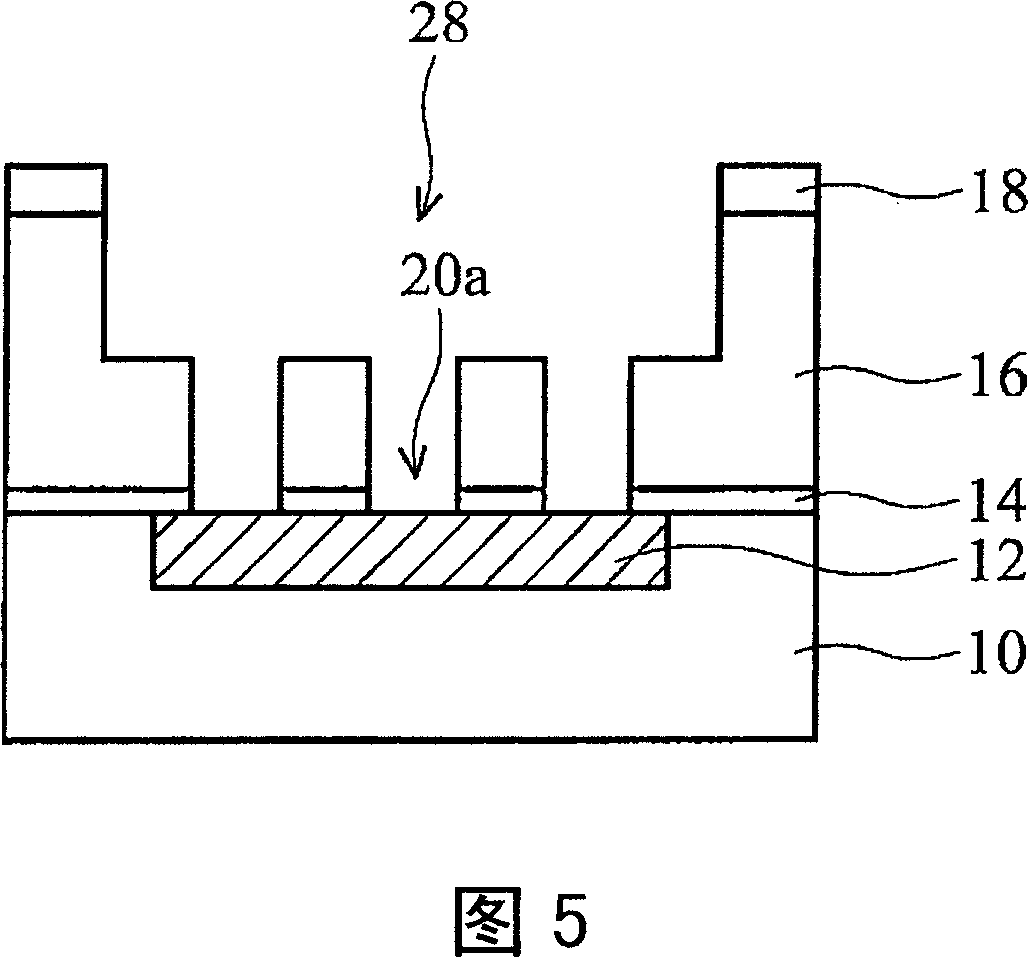

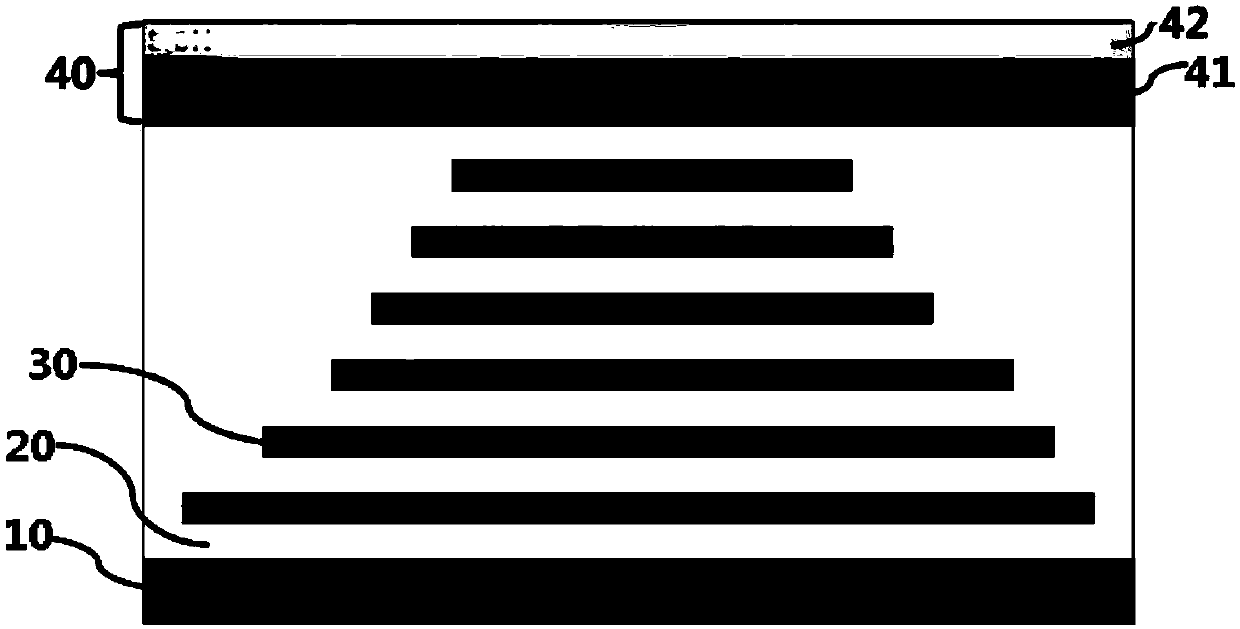

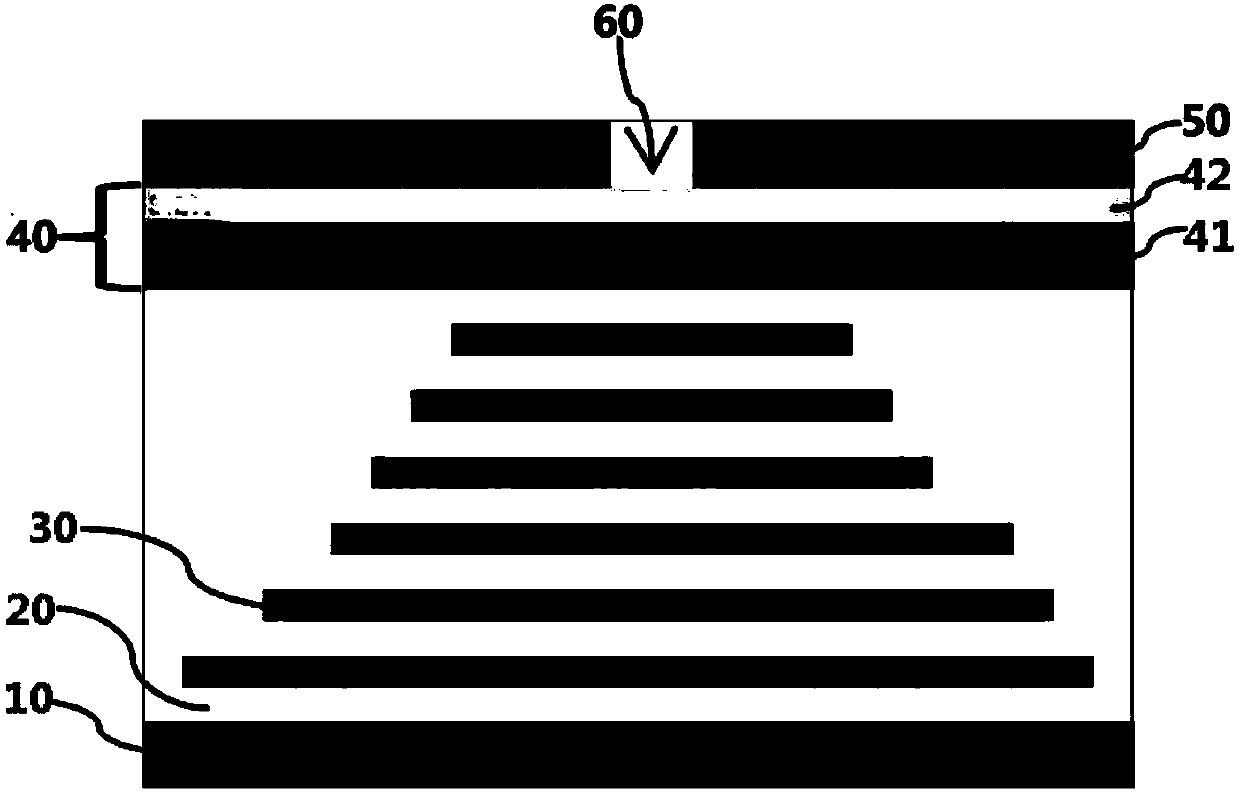

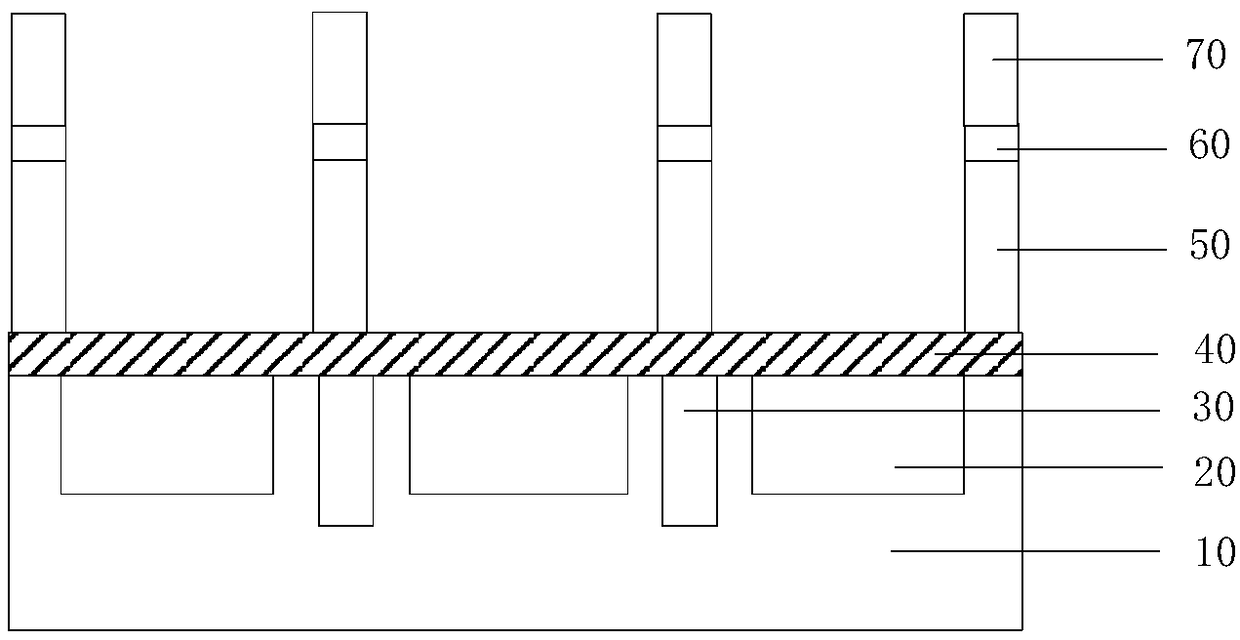

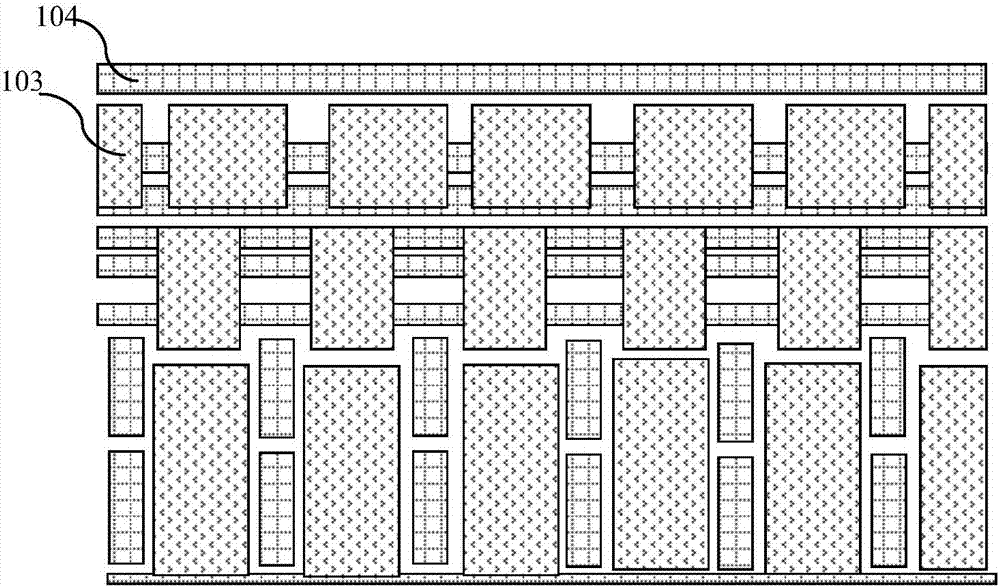

The invention relates to the field of integrated circuit manufacturing, in particular to a method for decreasing the critical size of a copper-connection groove. In the manufacturing process of a mask of the copper-connection groove, after a traditional process is used for etching to a dielectric layer to form a first groove, a polymer layer is deposited on the surface of a device by the adoption of a plasma deposition process, the first groove is filled with the polymer layer, then plasma etching is conducted, the polymer layer is partially removed, the polymer layer with a certain thickness is reserved on the inner wall of the first groove, so that a second groove which is smaller in size compared with the critical size of an original pattern is formed, afterwards, the second groove is used for etching until a metal through hole area inside a substrate is exposed out of the substrate, and finally the polymer layer left in the groove is removed through the way of wet process cleaning so that the subsequent processes can be continued. According to the technical scheme, in the preparation technology of the copper-connection groove, the critical size of the groove can be decreased, the device performance can be enhanced, meanwhile production cost is low, and therefore the method for decreasing the critical size of the copper-connection groove is suitable for application and popularization.

Owner:SHANGHAI HUALI MICROELECTRONICS CORP

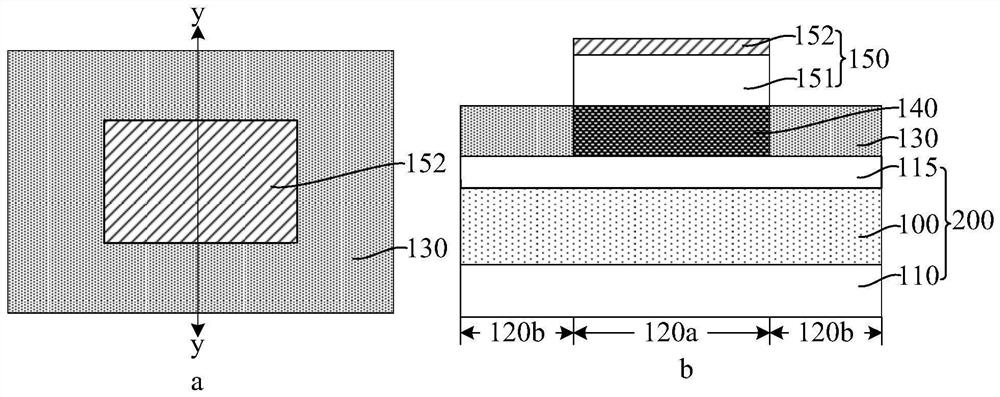

Method for reducing critical size of copper interconnection groove

InactiveCN103337476AImprove performanceReduce critical sizeSemiconductor/solid-state device manufacturingPlasma depositionInterconnection

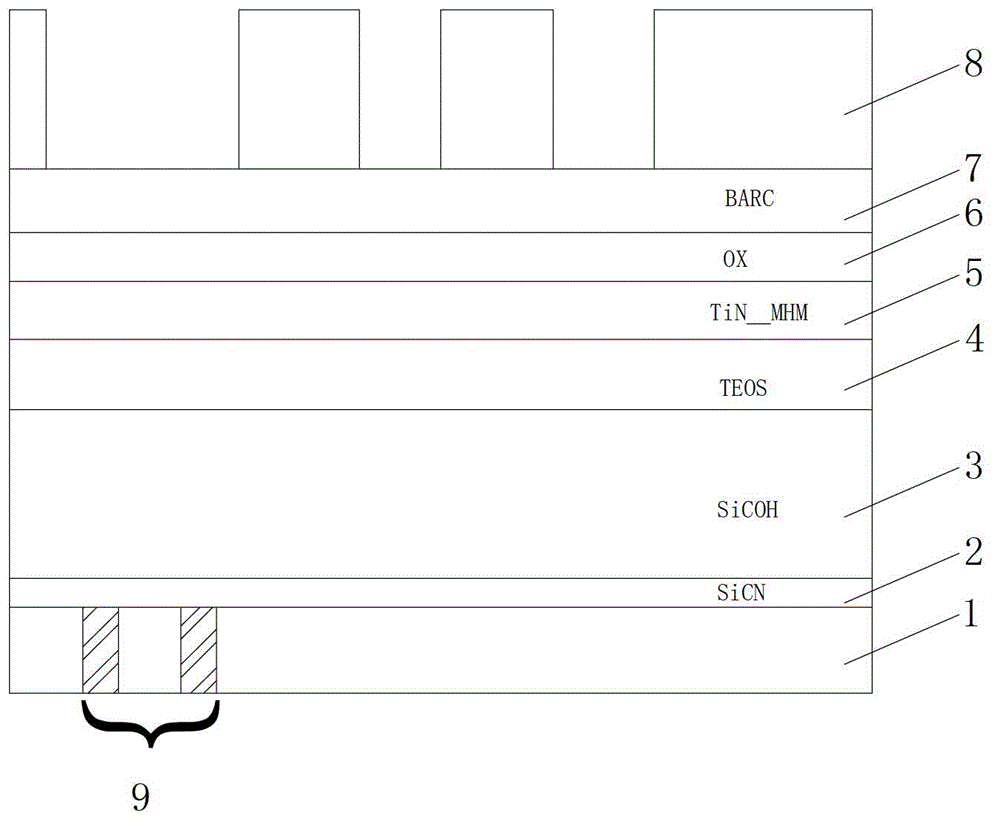

The invention relates to the field of manufacturing of integrated circuits, in particular to a method for reducing the critical size of a copper interconnection groove. In the mask manufacture process of the copper interconnection groove, the operation of etching is performed to the dielectric layer so as to form a first groove by utilizing the traditional process, thereafter, a silicon nitride film is deposited on the surface of a device through adopting the plasma deposition process and the first groove is filled, then plasma etching is performed, the silicon nitride film is partly removed and the silicon nitride film with a certain thickness is retained on the inner wall of the first groove, so that a first groove with the critical size smaller than that of the original picture is formed, then the operation of etching is performed by utilizing the second groove till a metal through-hole area in the substrate is exposed, and finally the residual silicon nitride film in the groove is removed by adopting wet process cleaning and the follow-up process is performed. Through adopting the technical scheme provided by the invention, in the manufacturing process of copper interconnection groove, the critical size of the groove can be reduced, the performance of the device is improved, and meanwhile the production cost is lower, so that the method facilities application and popularization.

Owner:SHANGHAI HUALI MICROELECTRONICS CORP

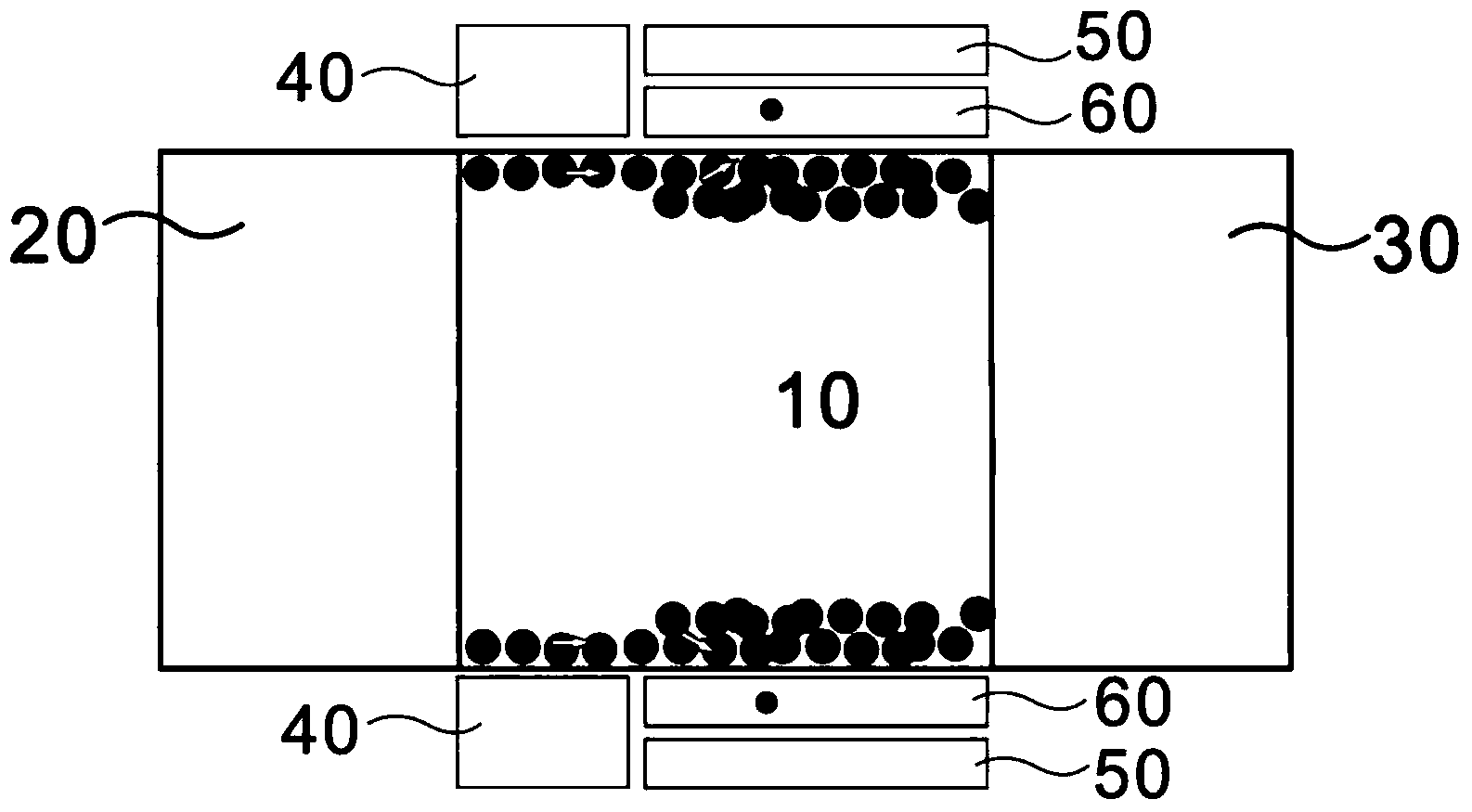

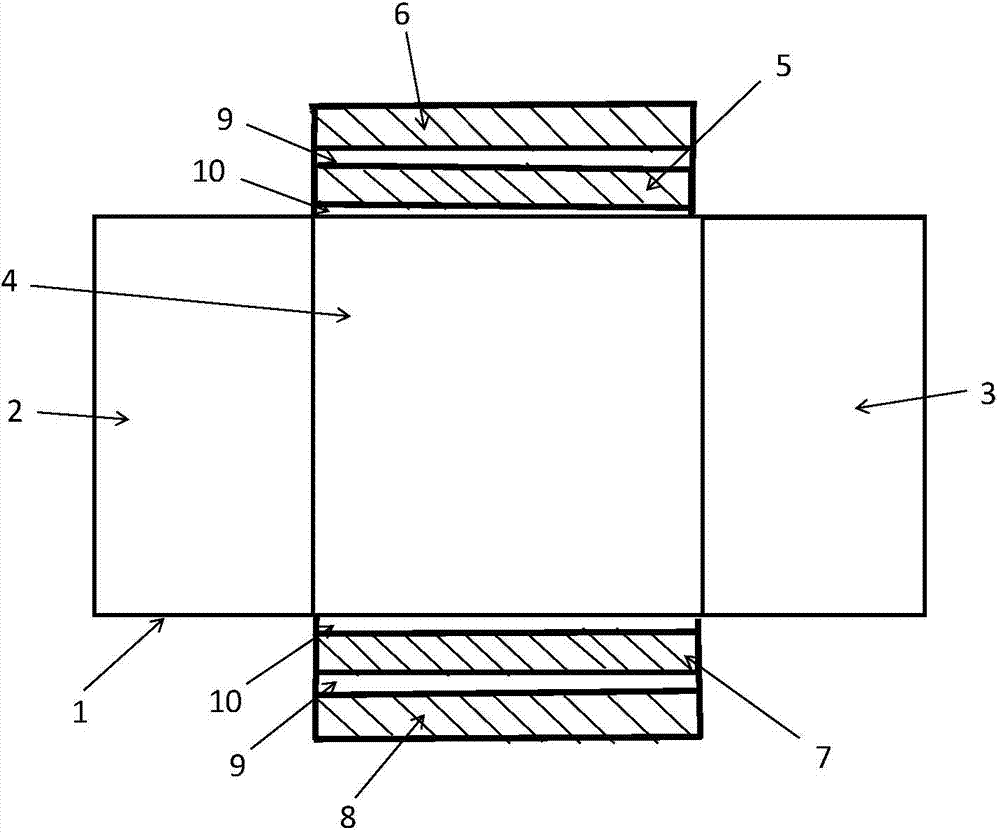

High-accuracy wide-range double-layer nano-grating micro displacement detection device

ActiveCN106524921ASmall grating periodHigh precisionUsing optical meansPhotodetectorPhotovoltaic detectors

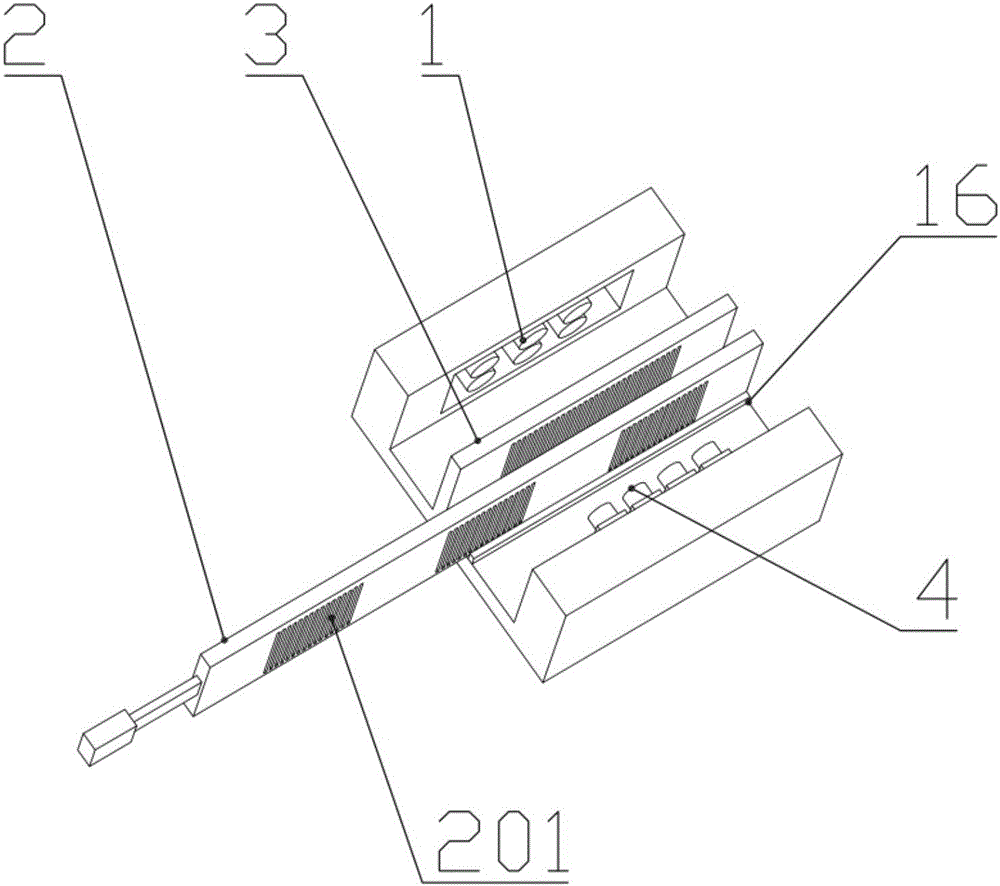

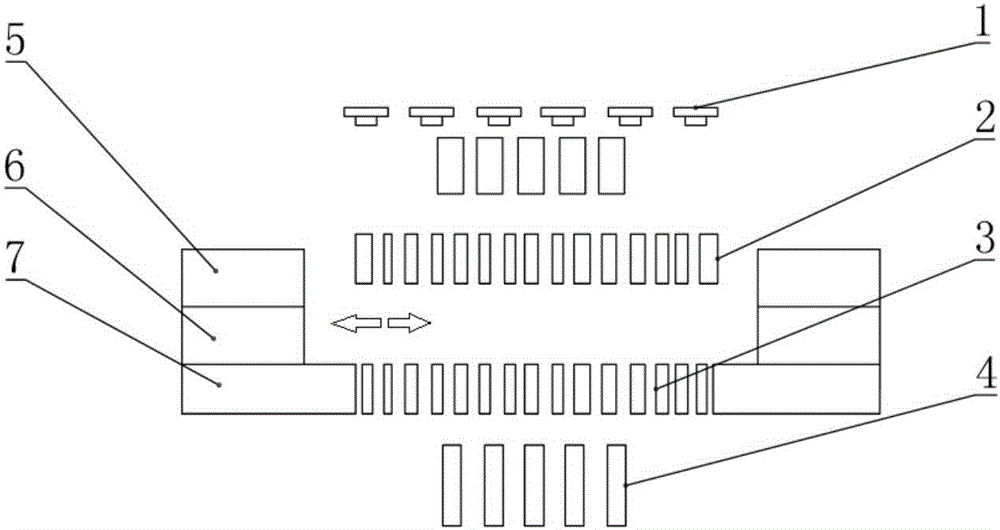

The present invention relates to a high-accuracy wide-range double-layer nano-grating micro displacement detection device. The micro displacement detection device includes a displacement sensing module, a processing unit and a display unit; the displacement sensing module is connected with the display unit through the processing unit; the displacement sensing module comprises double nano-grating layers which can move relative to each other; the double nano-grating layers include a movable nano-grating array and fixed nano-gratings; a plurality of nano-grating regions are spliced to form the movable nano-grating array; certain intervals are left between the plurality of nano-grating regions; the processing unit includes a subdividing circuit; and the subdividing circuit can improve the resolution of the output signals of a photodetector array. The grating period of the micro displacement detection device is smaller than the grating period of an existing micrometer-scale device, and therefore, the micro-displacement detection precision of the gratings is improved; the grating regions of the movable nano-grating array are spliced, so that the range of the micro displacement detection device is wider. The micro displacement detection device has the advantages of compact overall structure, high miniaturization degree and higher practicality.

Owner:ZHONGBEI UNIV

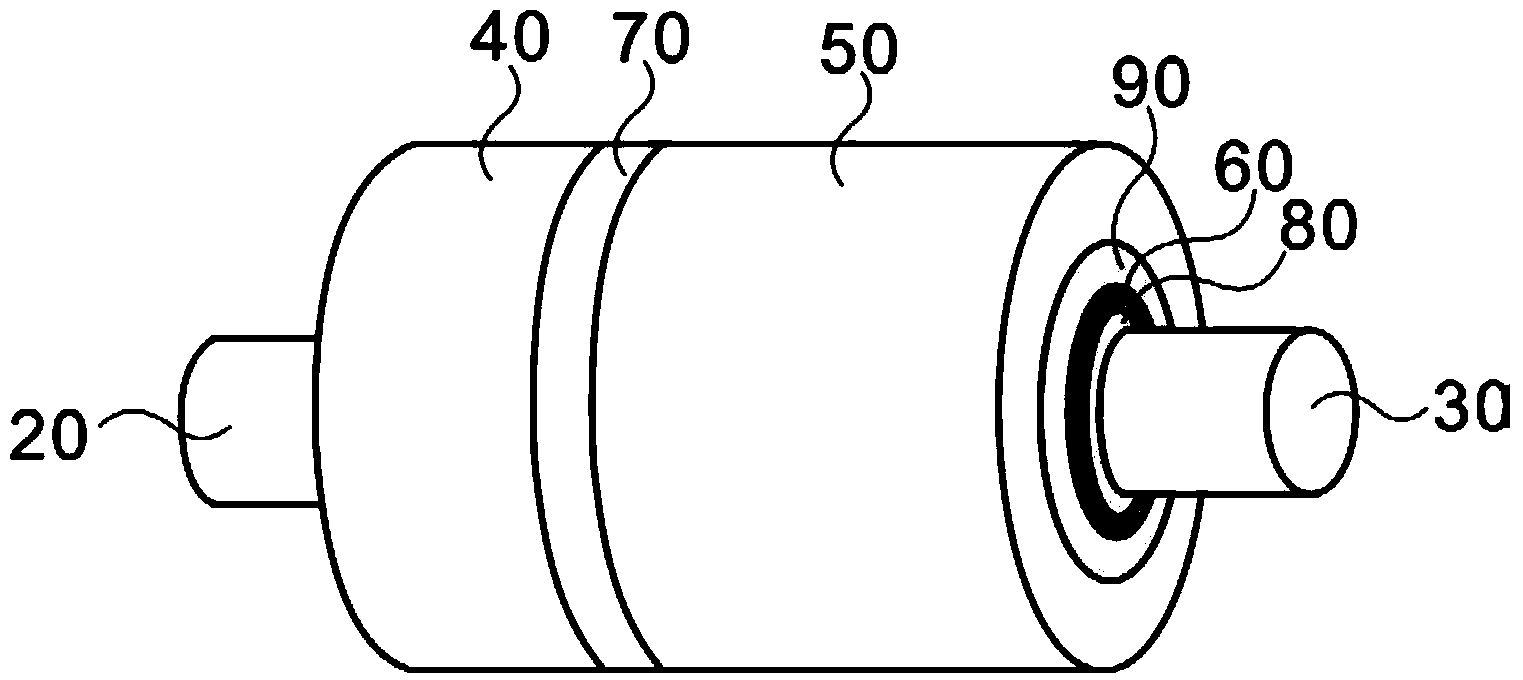

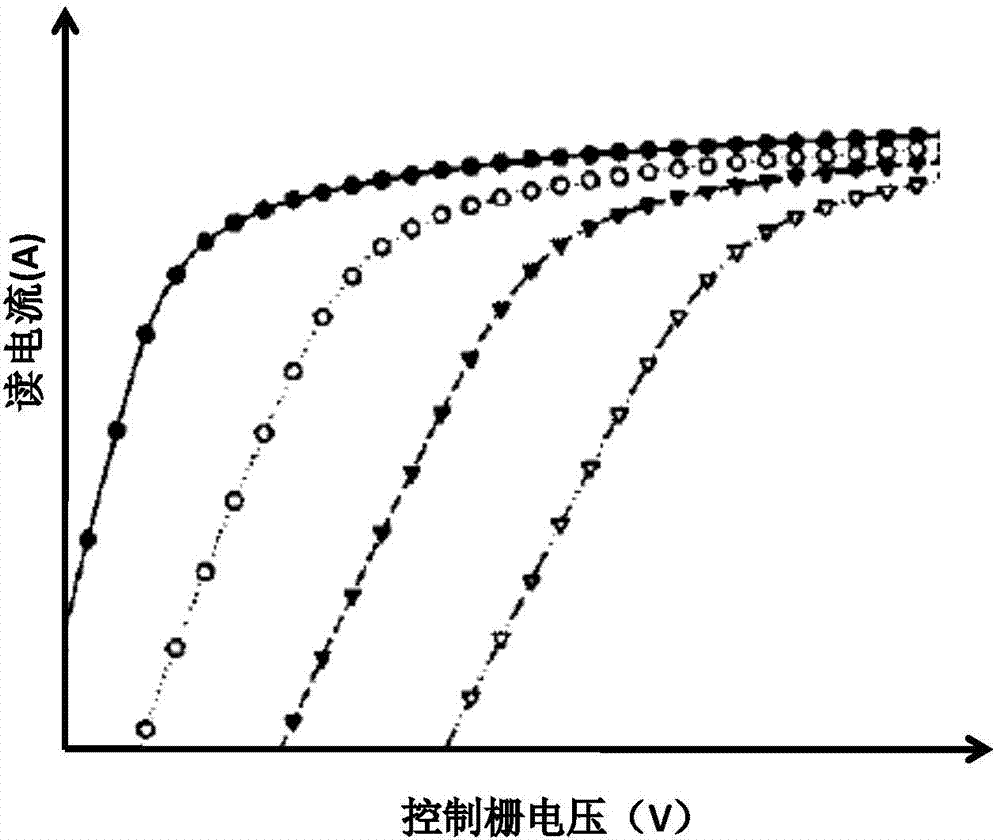

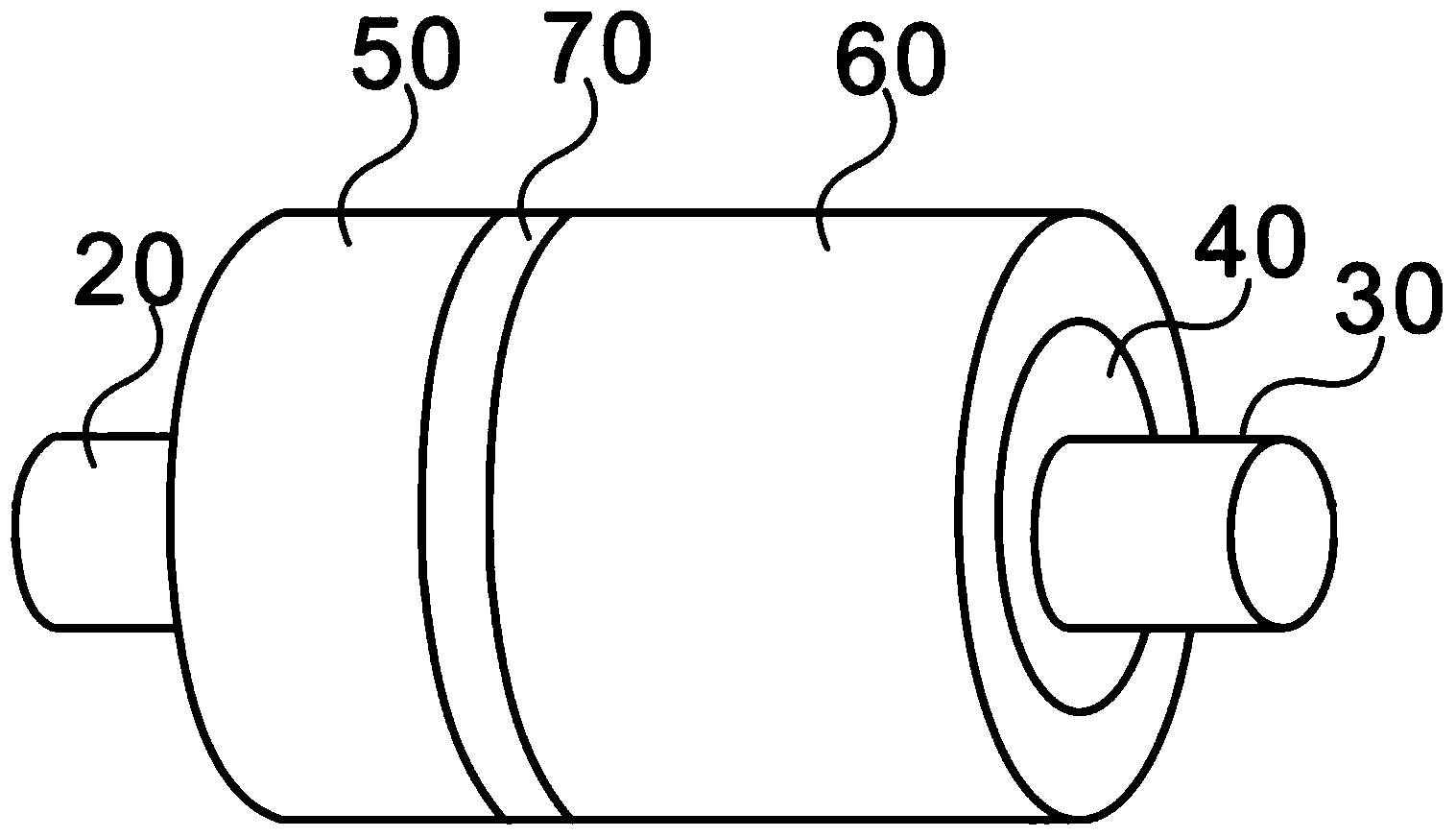

SONOS (silicon oxide nitride oxide silicon) flash memory device and compiling method thereof

ActiveCN104332471AReduce read errorsReduce critical sizeSolid-state devicesSemiconductor/solid-state device manufacturingSilicon oxideNitride

The invention provides an SONOS (silicon oxide nitride oxide silicon) flash memory device and a compiling method thereof. The SONOS flash memory device comprises a substrate of a cylinder structure and a grid electrode which wraps the middle of the substrate, wherein a source terminal and a drain terminal are respectively arranged at two ends of the substrate, the grid electrode comprises a first silicon gate and a second silicon gate which are parallel, a first oxidation layer is arranged between the first silicon gate and the second silicon gate, and a second oxidation layer arranged on the substrate, a silicon nitride layer arranged on the second oxidation layer and used to store electric charges and a third oxidation layer arranged on the silicon nitride layer are sequentially arranged between the second silicon gate and the substrate. The above structure of the SONOS flash memory device can restrain short channel effects and resist threshold voltage drifts, and simultaneously can effectively reduce the critical size of the SONOS flash memory device. The compiling method of the SONOS flash memory device assists in movement of thermion by adjusting voltage of the grid electrode and the drain terminal, provides sufficient oxidation layer crossing energy to complete compiling, improves compiling efficiency of the SONOS flash memory device, and reduces compiling electric current power consumption.

Owner:SHANGHAI HUALI MICROELECTRONICS CORP

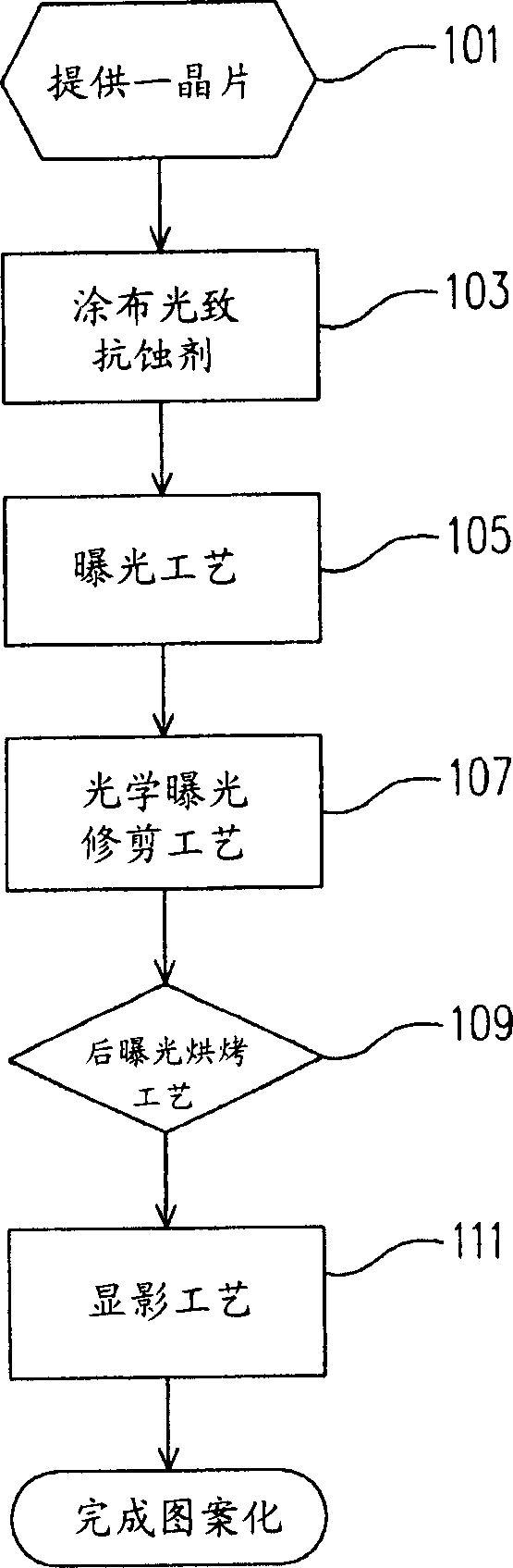

Method for reducing critical dimension

InactiveCN1866130AExemption from changes in natureReduce processing timeSemiconductor/solid-state device manufacturingPhotomechanical exposure apparatusEngineeringCritical dimension

A method for reducing critical dimension is provided. An exposure process and a develop process are performed on a photoresist layer. An optical trim exposure process is performed between the exposure process and the development process or before the exposure process. The optical trim expsoure process is performed to expose the photoresit layer by using a fully open mask of which the transmission rate is greater than zero. Because of the performance of the optical trim exposure process, the critical dimension of the photoresist layer can be reduced without substantially changing the characteristics of the photoresist layer.

Owner:UNITED MICROELECTRONICS CORP

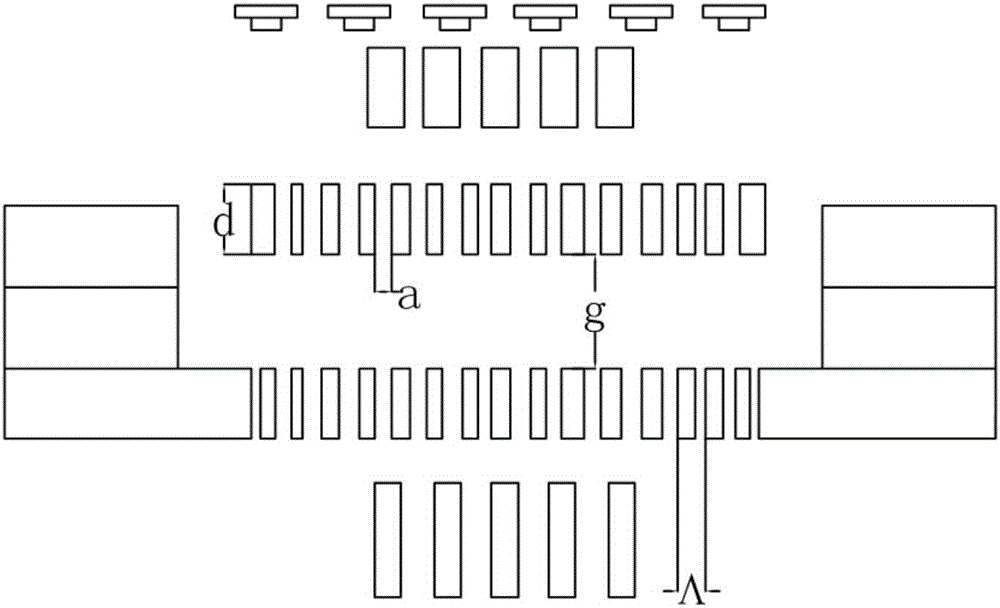

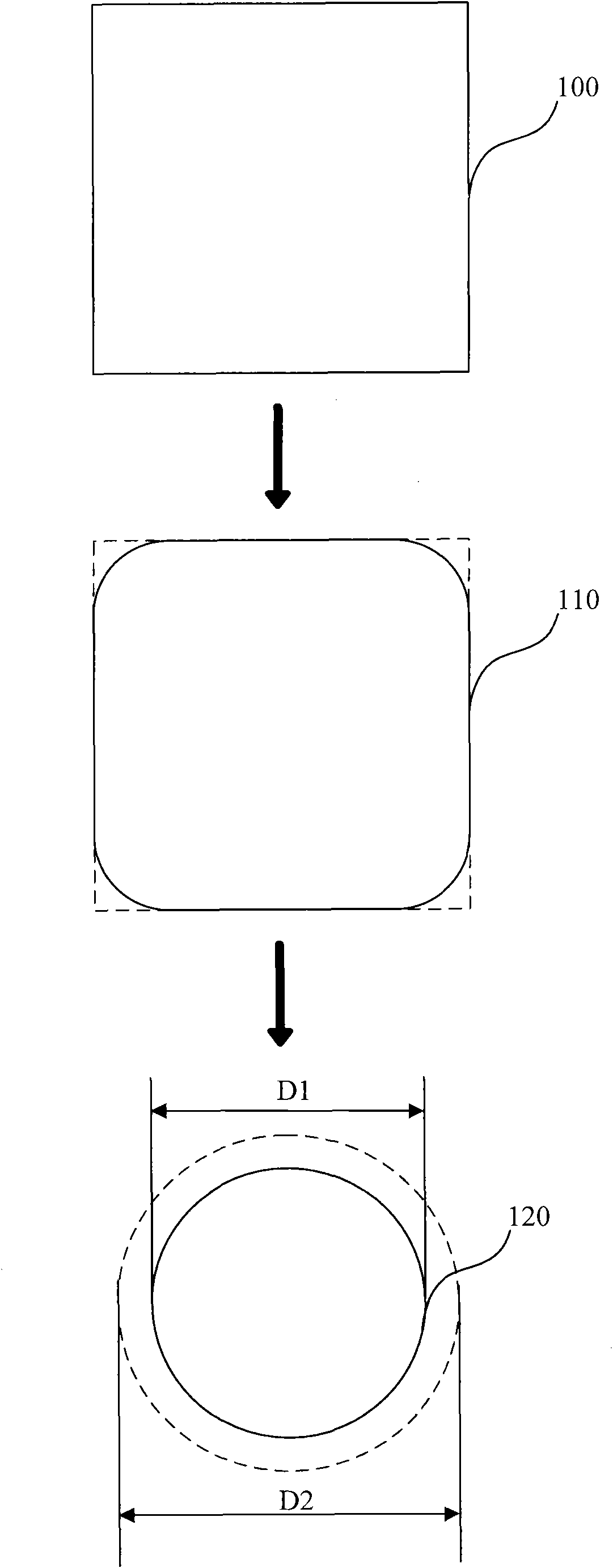

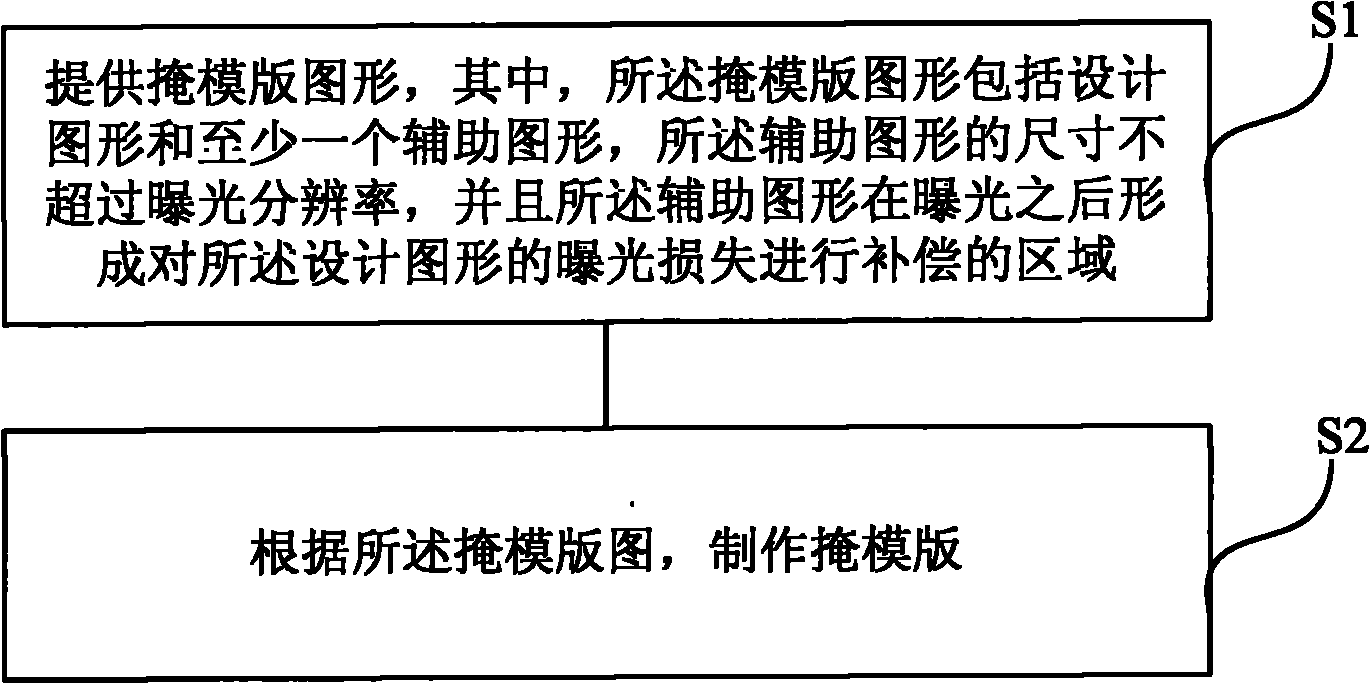

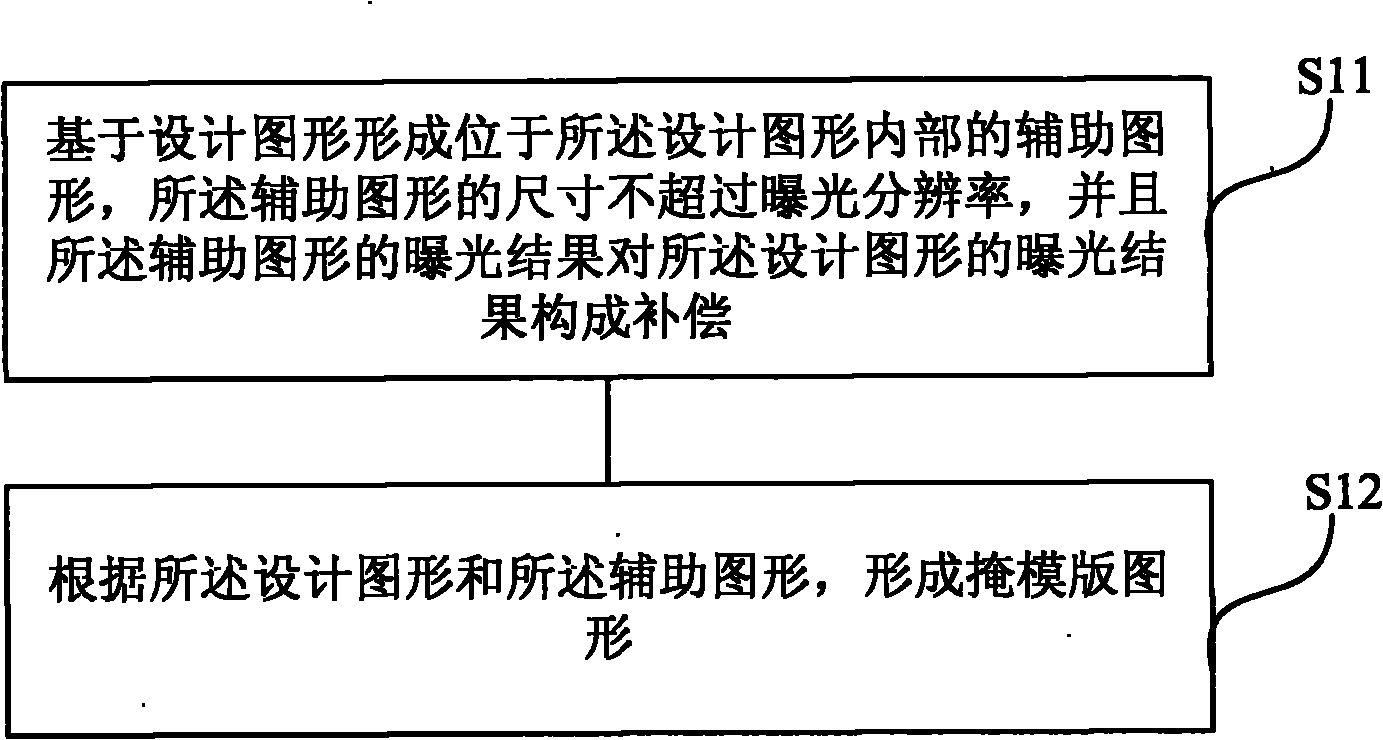

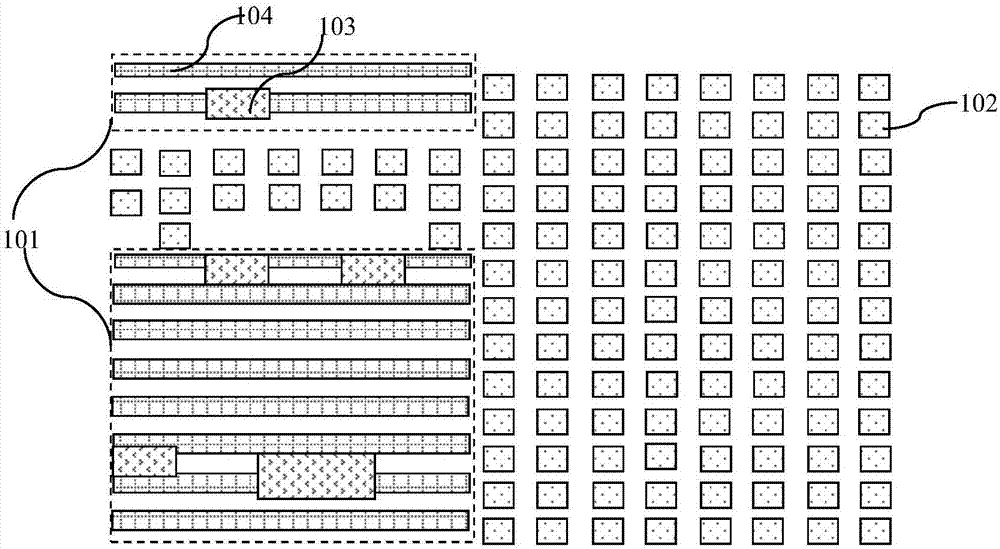

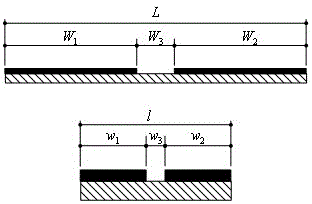

Mask graph, method for manufacturing mask, and method for correcting mask graph

ActiveCN102096308AReduce critical sizeSimplify the calibration stepsOriginals for photomechanical treatmentComputer science

The invention relates to a mask graph, a method for manufacturing a mask, and a method for correcting the mask graph. The mask graph comprises a design graph for forming a product graph according to an exposure and development process, and an auxiliary graph of which the size does not exceed exposure resolution, wherein an area for compensating the exposure loss of the design graph is formed in the auxiliary graph after the auxiliary graph is exposed. By setting the auxiliary graph, the exposure distortion of the design graph is effectively compensated, so that the critical size of the obtained product is increasingly close to the expected size, a large amount of time and energy for comparing and debugging are saved, production efficiency is improved, and production cost is saved.

Owner:SEMICON MFG INT (SHANGHAI) CORP +1

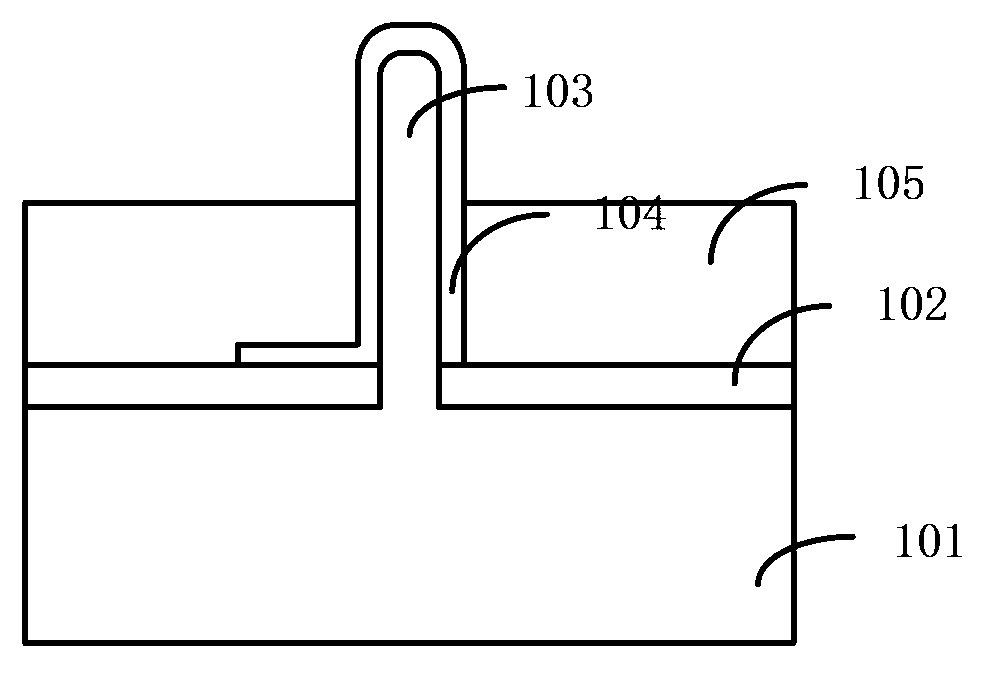

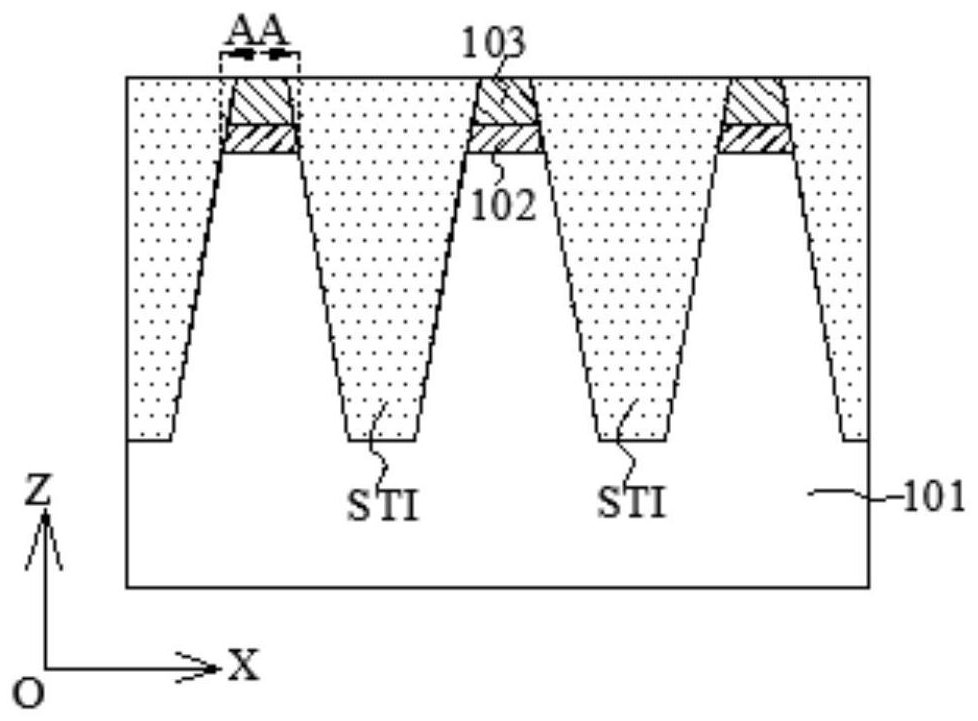

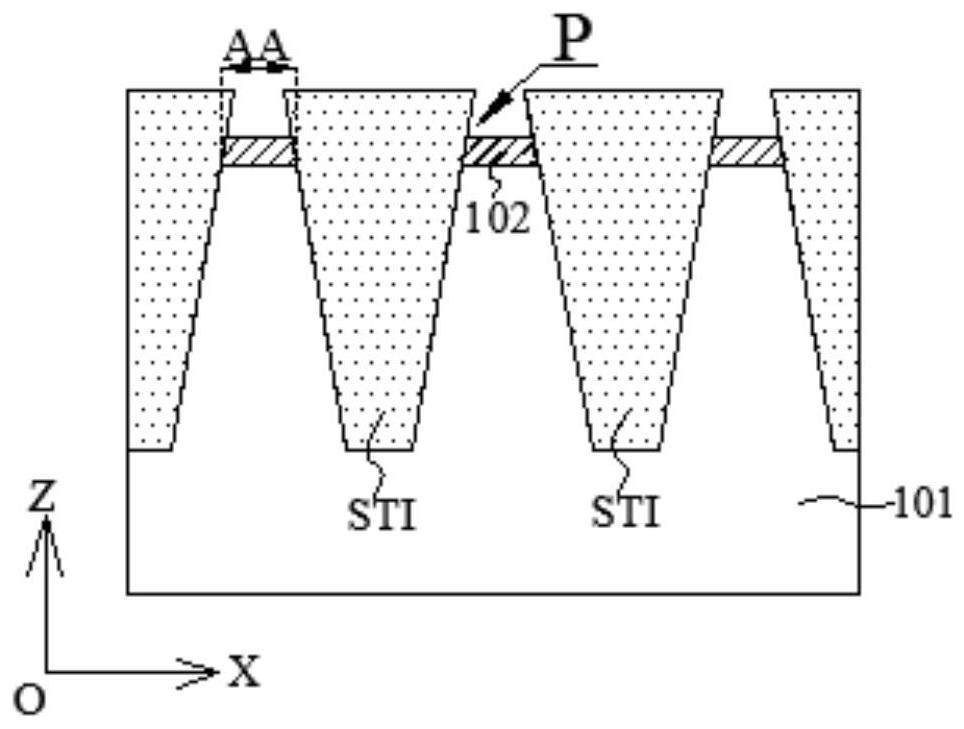

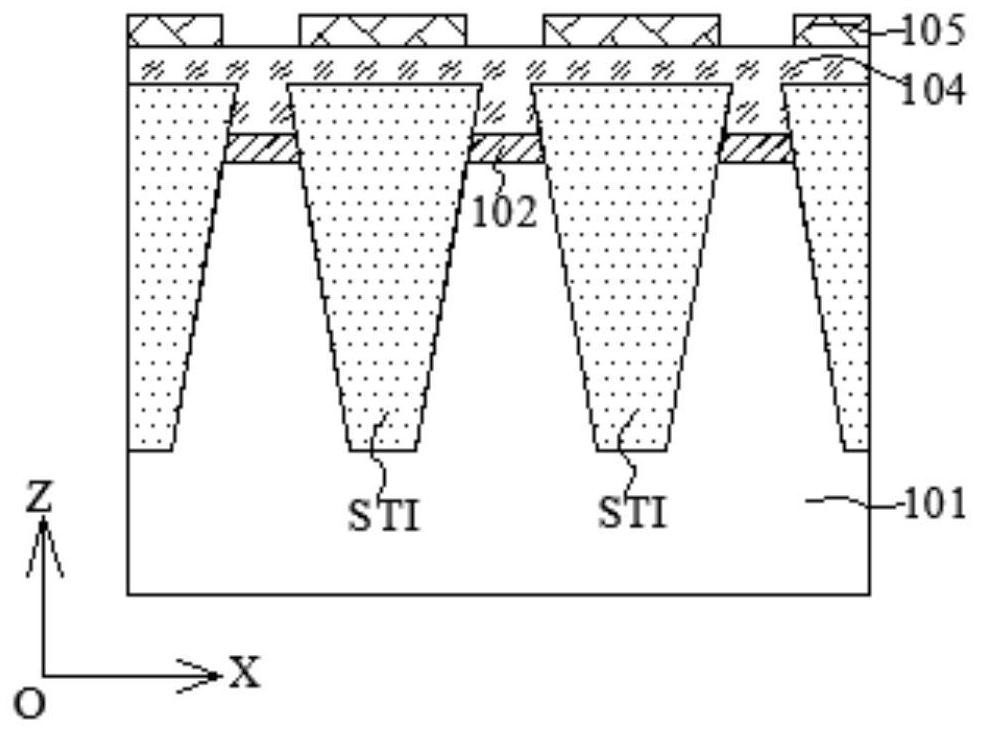

Semiconductor device and manufacturing method, and electronic device

ActiveCN108155237AImprove performanceImprove yieldSemiconductor/solid-state device manufacturingSemiconductor devicesManufacturing technologySemiconductor technology

The invention provides a semiconductor device and a manufacturing method, and an electronic device and relates to the semiconductor technology field. The semiconductor device comprises the first conductive type of a semiconductor substrate, a grid structure, a source electrode and a drain electrode, and a groove contact, wherein the grid structure is formed on the semiconductor substrate; the source electrode and the drain electrode are formed in the semiconductor substrate of the two sides of the grid structure, an interval exists between the drain electrode and the grid structure, and the extension direction of a connection line between the source electrode and the drain electrode is defined as a first direction; the groove contact is formed in the semiconductor substrate between the grid structure and the drain electrode; the groove contact includes a main body portion and several comb teeth connected to the main body portion; and the at least one side of the main body portion, which is along with the first direction, is provided with the comb teeth. By using the groove contact of the semiconductor device, the margin of a manufacturing technology can be improved, the key size ofthe groove contact can be reduced, and a problem that an active area and a polycrystalline silicon grid are damaged during groove contact manufacturing can be effectively solved.

Owner:SEMICON MFG INT (SHANGHAI) CORP +1

Dual-damascene process

ActiveCN1983552AReduce microloading effectsReduce critical sizeSemiconductor/solid-state device manufacturingResistInter layer

The invention provides a partial-via-first dual-damascene method using a tri-layer resist method forms a first via hole through partial thickness of a dielectric layer, and forms a tri-layer resist structure on the dielectric layer to fill the first via hole with the bottom photoresist layer. A dry development process is performed to transfer a first opening on the top photoresist layer to the middle layer and the bottom photoresist layer, and expose the first via hole again, and remove the top photoresist layer. A dry etching process is then performed to form a second via hole under the first via hole and a trench over the second via hole. Finally a wet striping process is used to remove the remainder of the photoresist layer.

Owner:TAIWAN SEMICON MFG CO LTD

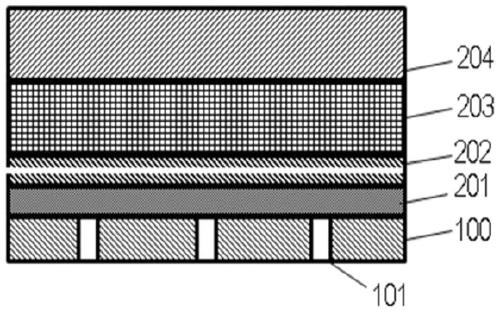

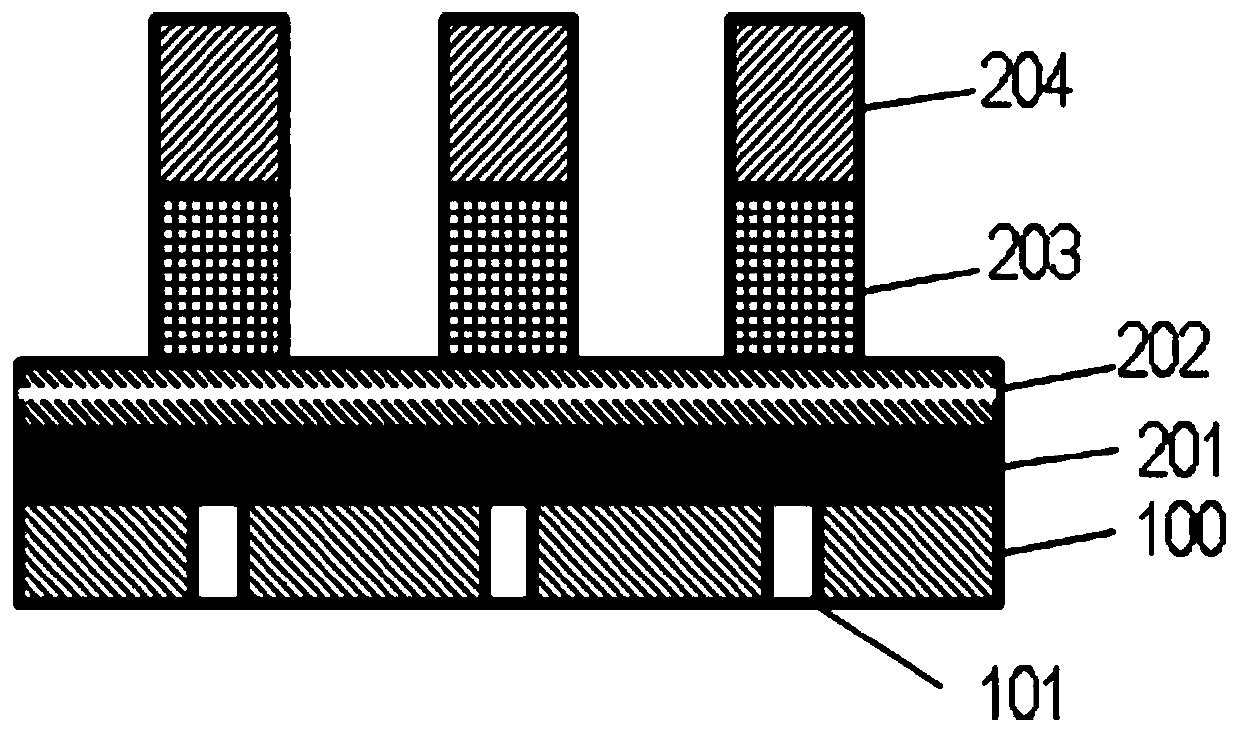

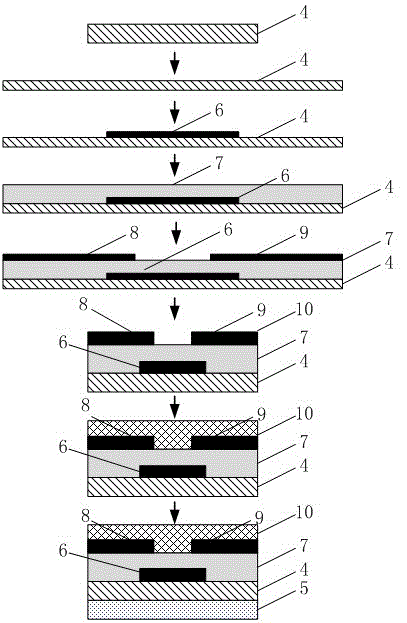

Photoetching-etching technological method of top select gate cut

InactiveCN107658308AReduce critical sizeAdapt to the needs of miniaturization developmentSolid-state devicesSemiconductor devicesResistDeposition temperature

The invention provides a photoetching-etching technological method of a top select gate cut. A technological step of low temperature oxide (LTO) material deposition is added after photoetching, so that the photoetching critical dimension (PHCD) is reduced equivalently, thereby realizing reduction of the critical dimension of the top select gate cut so as to satisfy the requirement of the miniaturization development of a semiconductor part. Meanwhile, the low temperature oxide (LTO) is used as the deposition material, so that the deposition temperature of the plasma enhanced chemical vapor deposition (PECVD) can be controlled to be about 50 DEG C which is far lower than the bake temperature of 100-120 DEG C of the photo resist material, so that a phenomenon of photo resist material softening in the material deposition can be fully avoided; and by adopting the above-mentioned mode to replace a mode adopting an immersion litho tool, the photoetching critical dimension is reduced economically and stably, thereby further reducing the critical dimension of the top select gate cut.

Owner:YANGTZE MEMORY TECH CO LTD

Image sensor and method for forming same

InactiveCN108933152AReduce critical sizeCritical dimension controlSolid-state devicesDiodeEngineeringPhotoresist

The technical solution of the present invention discloses an image sensor and a method for forming the same. The method for forming the image sensor includes: providing a semiconductor substrate; forming a first insulating layer on the semiconductor substrate; forming a patterned photoresist layer on the first insulating layer; by using the patterned photoresist layer as a mask, etching the firstinsulating layer to form a metal grid pattern; forming a second insulating layer on the sidewall and the bottom of the metal grid pattern; fully filling the metal grid pattern with a metal layer to form metal grids; and removing the second insulating layer outside the metal grids and a certain thickness of the first insulating layer. The method controls the critical dimension of the metal grids tomeet a corresponding requirement, and further ensures the performance of the image sensor and the yield of devices.

Owner:HUAIAN IMAGING DEVICE MFGR CORP

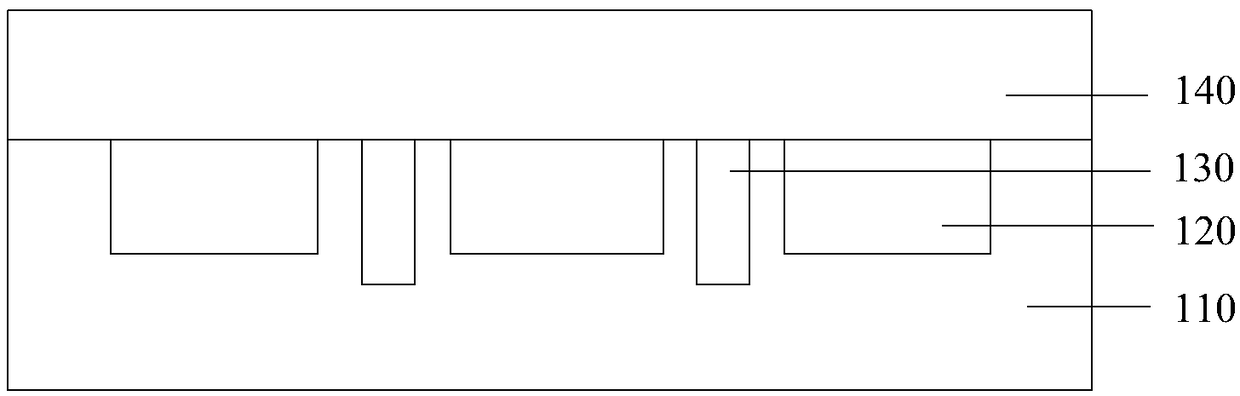

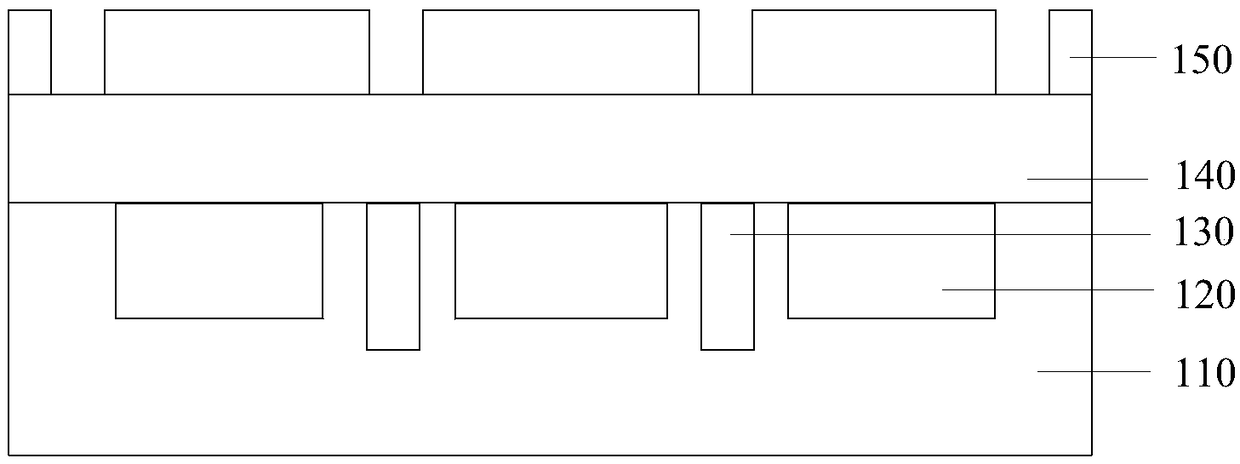

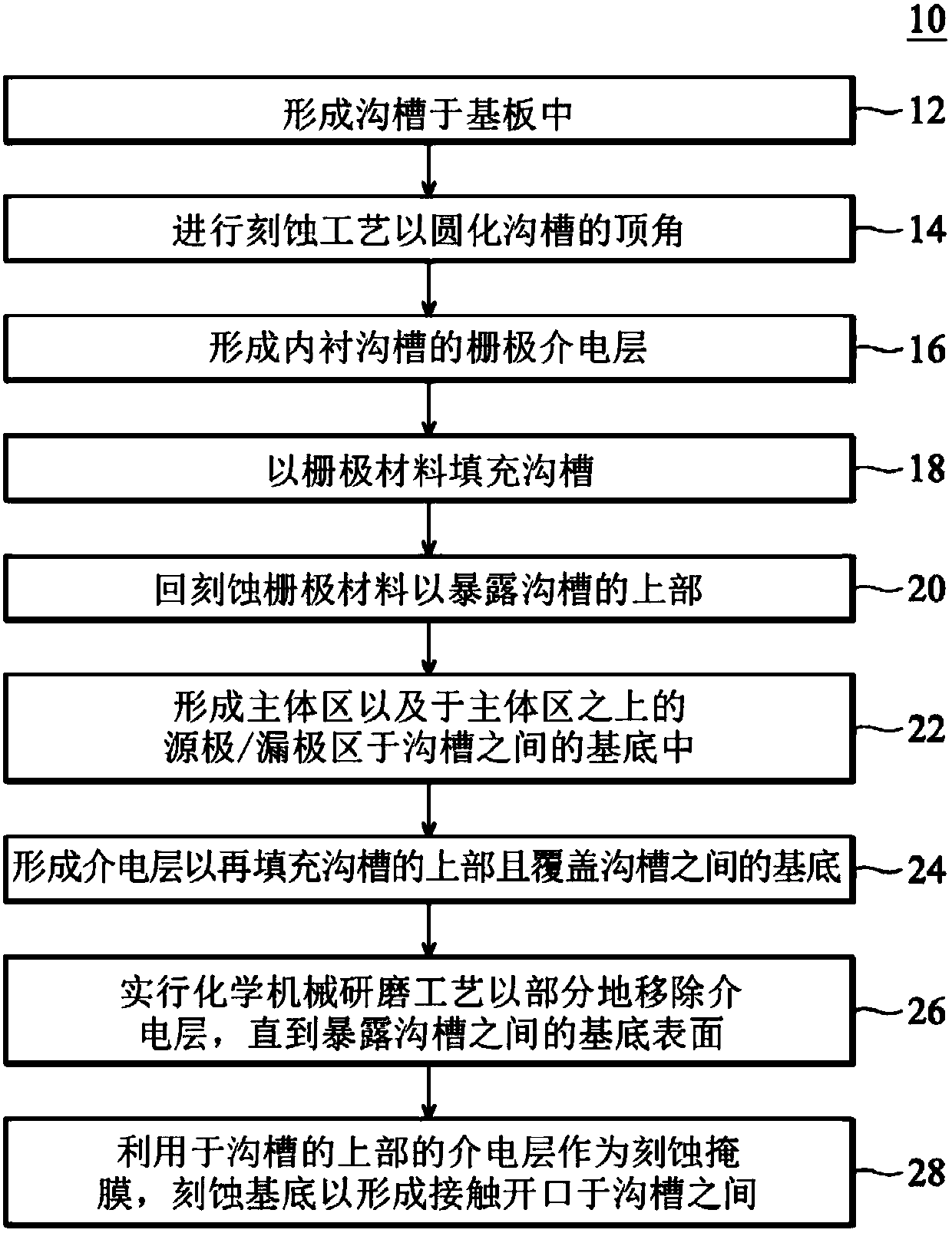

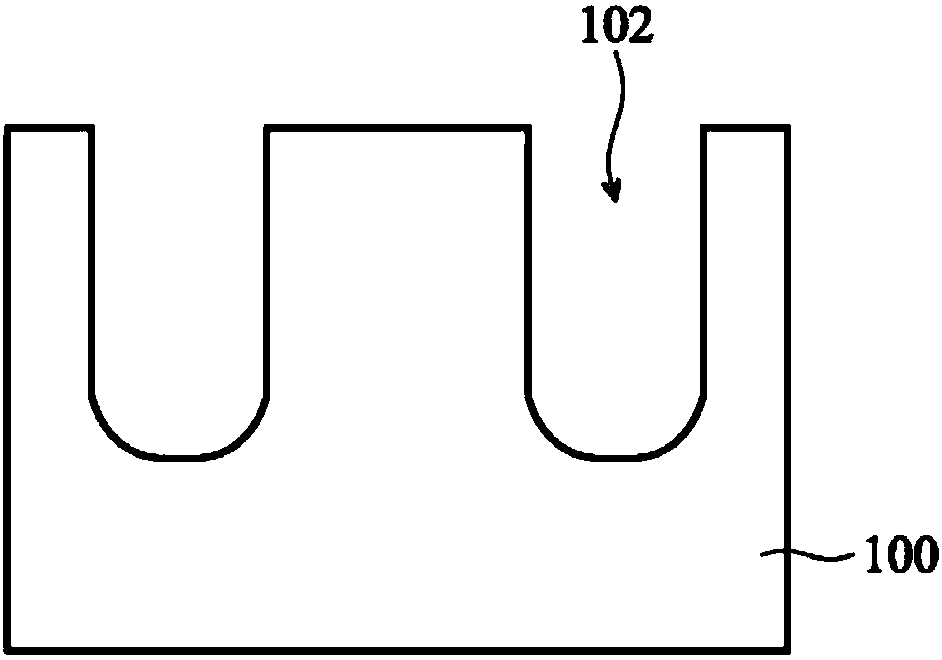

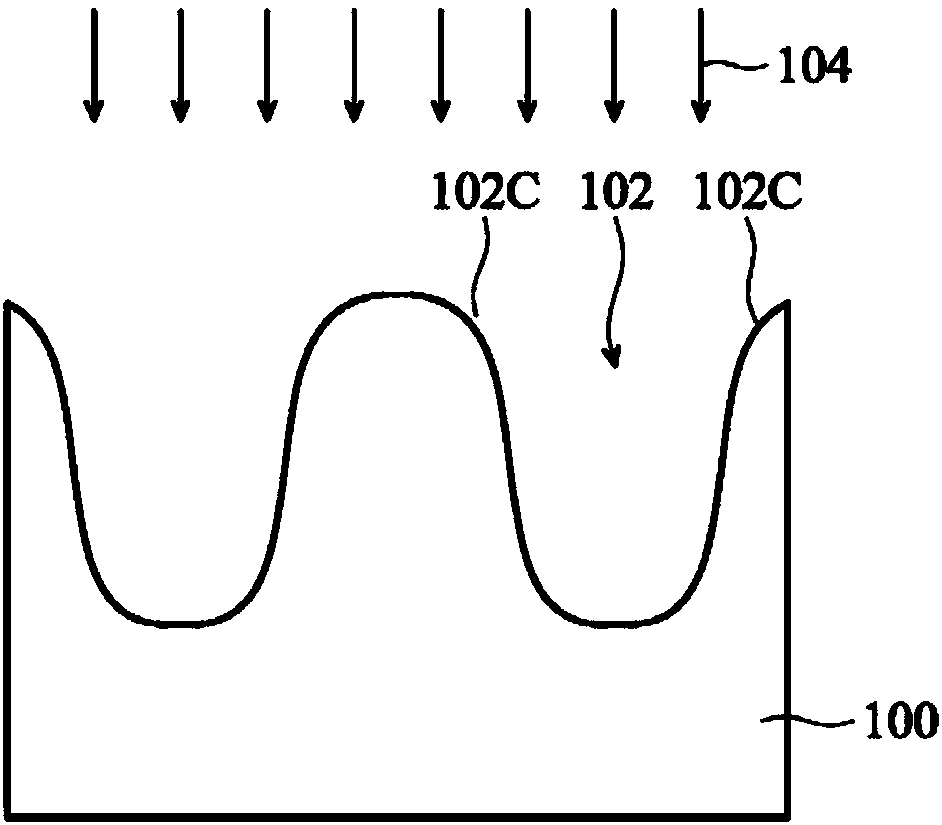

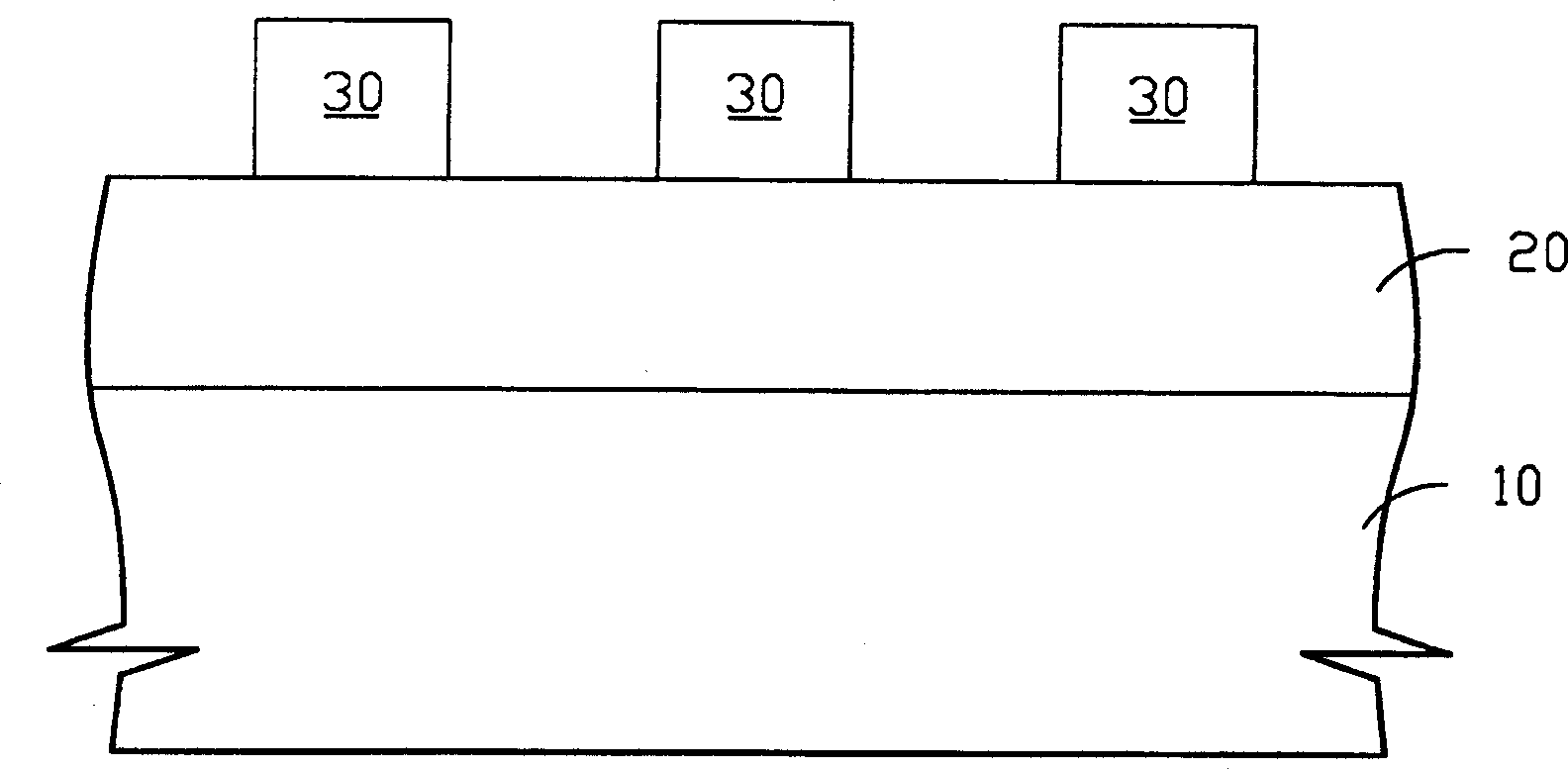

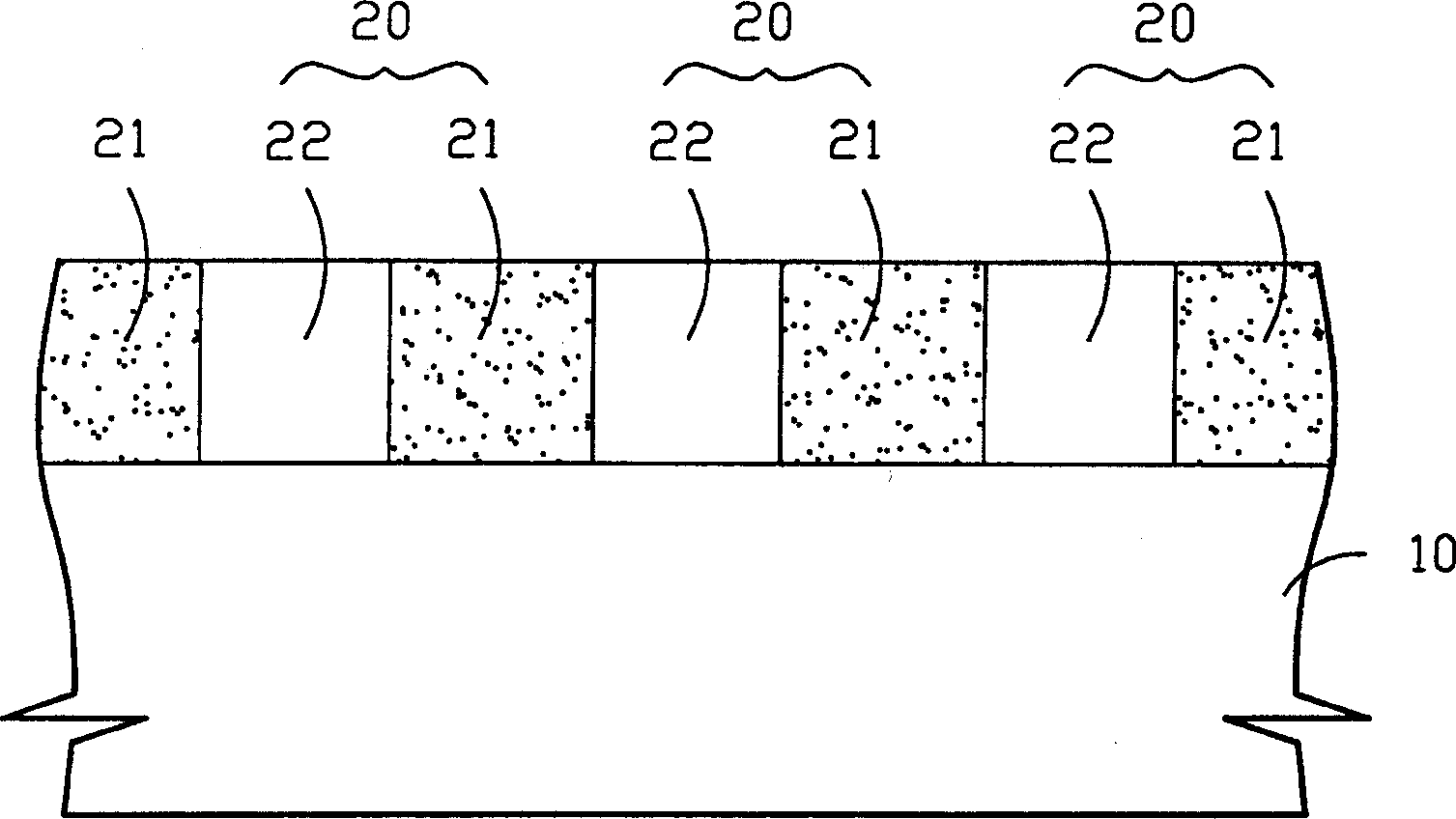

Formation method for structure of semi-conductor device

InactiveCN107689328AReduce critical sizeAvoid misalignmentSemiconductor/solid-state device manufacturingSemiconductor devicesGate dielectricEngineering

The invention provides a formation method for structure of semi-conductor device, which includes forming several grooves in the base; forming a gate dielectric layer in the grove as an inner liner; filling the grooves with gate materials; re-etching the gate materials to make the top of the grooves be exposed; filling the top of grooves with a first dielectric layer which also covers the surface of the base between two grooves; implementing a first chemical and mechanical grinding techniques to partly eliminate the first dielectric layer, until the surface of the base between two grooves is exposed; using the first dielectric layer, which is used to form the top of the grooves, as an etching mask; and etching the base to form self-aligned contact openings between the grooves by exposing the surface of the base to the air.

Owner:VANGUARD INTERNATIONAL SEMICONDUCTOR CORPORATION

Double-bit flash memory, and programming, erasing and reading method thereof

InactiveCN104733045AImprove storage capacity per unit areaReduce critical sizeRead-only memoriesDigital storageTerminal voltageGate oxide

The invention discloses a double-bit flash memory, which comprises a P-type substrate, a first floating gate, a second floating gate, a first control gate and a second control gate, wherein the P-type substrate comprises a source terminal and a drain terminal; the first floating gate, the second floating gate, the first control gate and the second control gate are sequentially located at the upper side and the lower side of the substrate; the first floating gate and the second floating gate are N-type doped polycrystalline silicon; the second control gate is made of P-type polycrystalline silicon; the second control gate is made of N-type polycrystalline silicon; in a programming process, positive drain terminal voltage is exerted on the drain terminal; the source terminal is grounded; the state of electrons stored in the corresponding floating gate is defined to be '1'; if the '1' state is programmed on any control gate, positive grid voltage is exerted on the corresponding control grid, so that an electronic inversion layer is generated on the groove of the substrate; under the accelerating action of the drain terminal voltage, groove electrons obtain enough energy and jump across a potential barrier between a grid oxidation layer and substrate silicon to become hot electrons; the hot electrons are injected into the floating gates to finish programming under the action of the grid voltage. According to the double-bit flash memory, the storage capacity per unit area of a floating gate flash memory is expanded, so that the dimension of the floating gate flash memory can be reduced.

Owner:SHANGHAI HUALI MICROELECTRONICS CORP

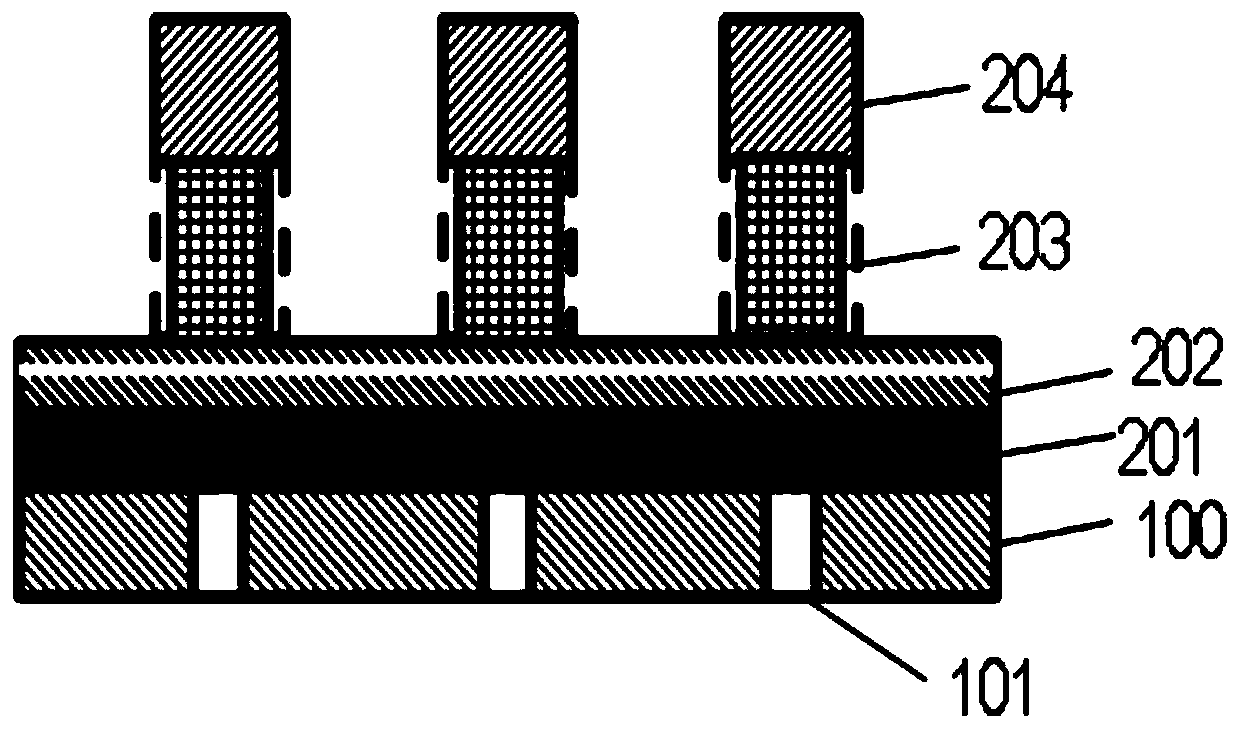

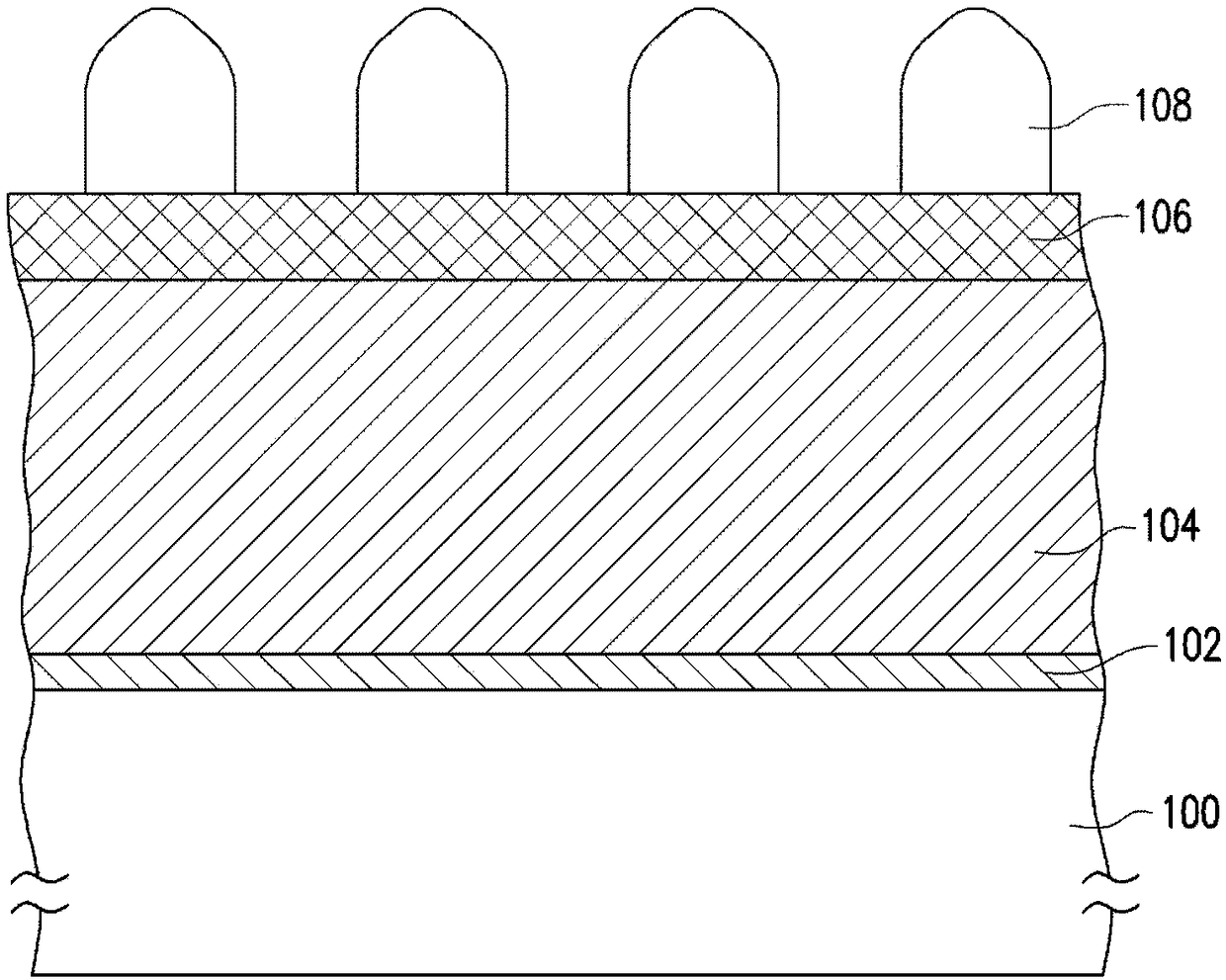

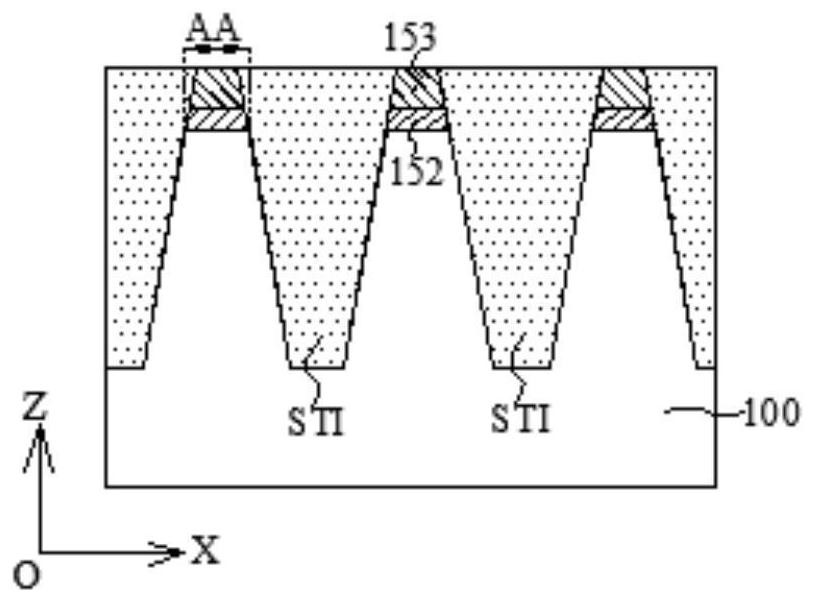

Method for manufacturing vertical SiGe FinFET

ActiveCN104241128AReduce critical sizeHighly integratedSemiconductor/solid-state device manufacturingSemiconductor devicesEngineeringSemiconductor

The invention relates to a method for manufacturing a vertical SiGe FinFET. The method includes the steps of providing a semiconductor substrate, forming a fin structure on the semiconductor substrate, depositing a first interlayer dielectric layer on the semiconductor substrate, carrying out epitaxy on the fin structure to form a SiGe layer, carrying out H2 high-temperature etching on the fin structure and the SiGe layer for forming vertical side walls, and meanwhile reducing the critical size of the fin structure and the critical size of the SiGe layer. By means of the method, after the fin structure is formed, the SiGe layer is grown on the fin structure in an epitaxy mode, the side wall of the fin structure and the side wall of the SiGe layer are etched with the hydrogen high-temperature etching method to be more vertical, the critical size of the fin structure and the critical size of the SiGe layer are reduced, the integrity of the FET is further improved, and finally the gate-all around is formed. Compared with a plane transistor, the performance of the FET is further improved.

Owner:SEMICON MFG INT (SHANGHAI) CORP

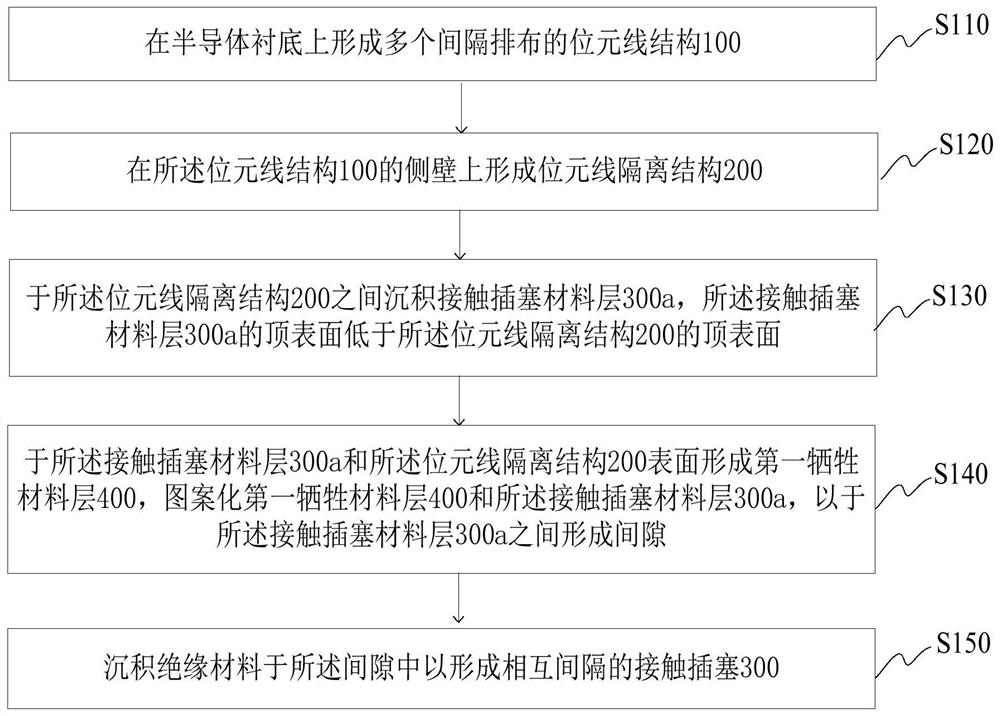

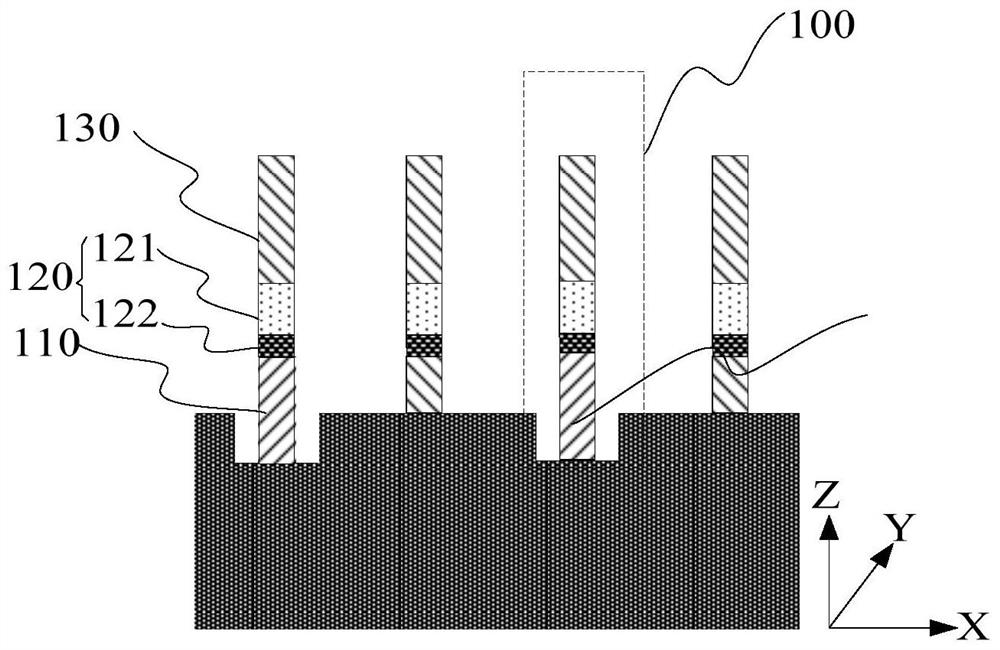

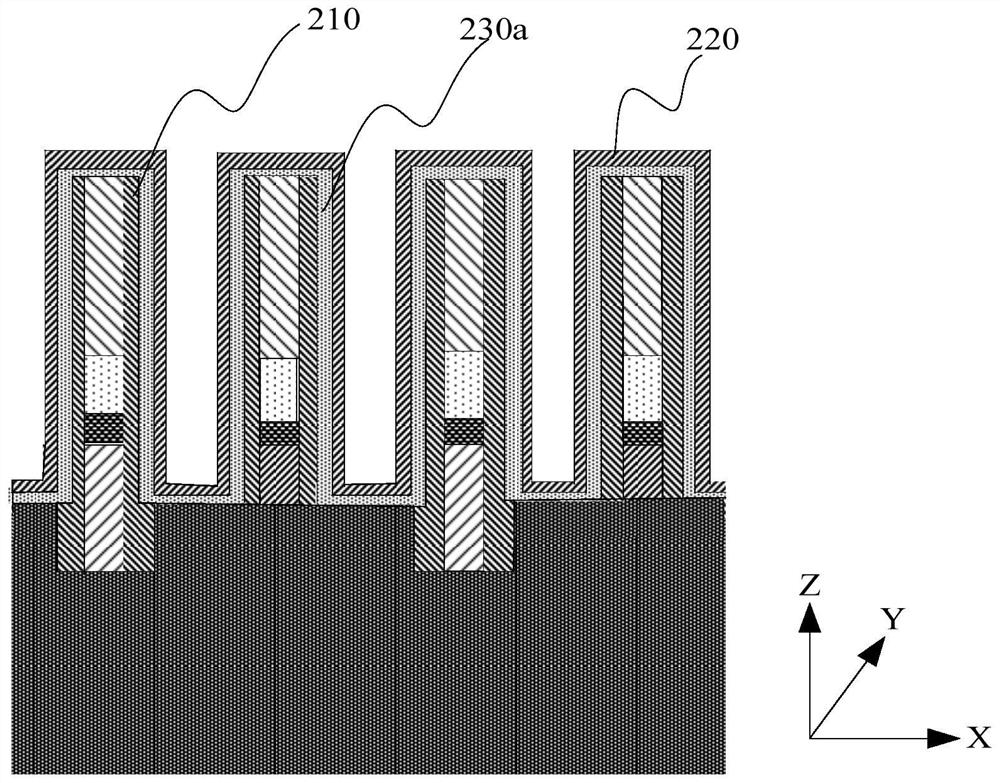

Manufacturing method of semiconductor device

ActiveCN112652623AReduce critical sizePrevent collapse and detachmentTransistorBit lineDevice material

The invention relates to a manufacturing method of a semiconductor device. The manufacturing method comprises the following steps: forming a bit line isolation structure on the side wall of a bit line structure; depositing a contact plug material layer between the bit line isolation structures, wherein the top surface of the contact plug material layer is lower than the top surfaces of the bit line isolation structures; forming a first sacrificial material layer on the surfaces of the contact plug material layer and the bit line isolation structure, patterning the first sacrificial material layer and the contact plug material layer, and forming a gap between the contact plug material layers; and depositing an insulating material in the gap to form contact plugs spaced apart from each other. According to the invention, the consumption of the bit line isolation structure is reduced by utilizing the high etching selection ratio among the contact plug material, the first sacrificial material layer and the bit line isolation structure, so that the thickness of the bit line isolation structure is reduced, and the critical size of the bit line is reduced. And the contact plug material layer is used for providing support for the bit line isolation structure, so that the bit line isolation structure is prevented from collapsing and being separated in the subsequent process.

Owner:CHANGXIN MEMORY TECH INC

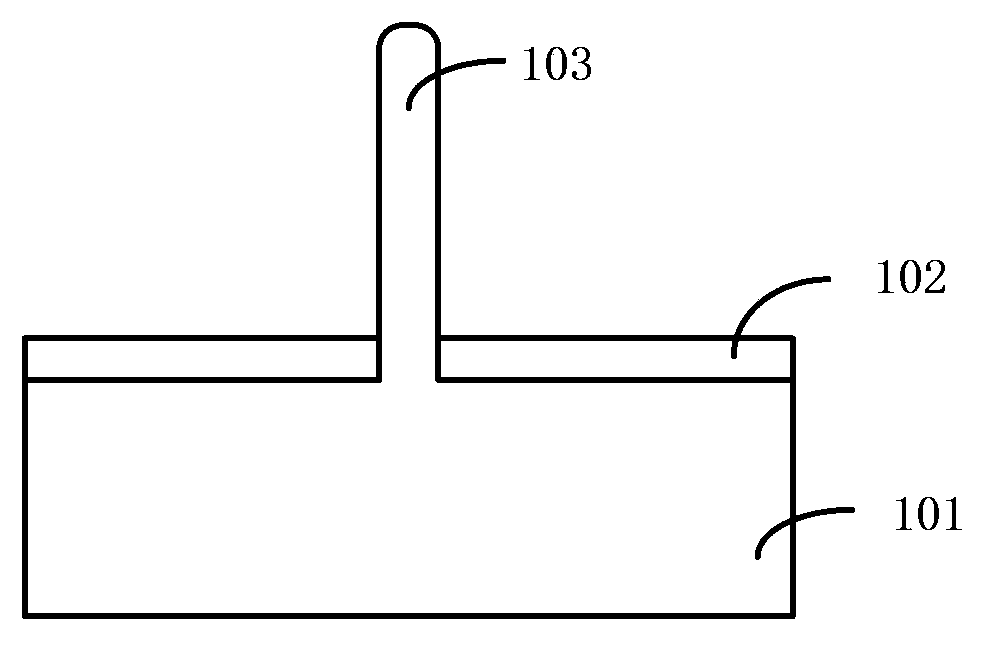

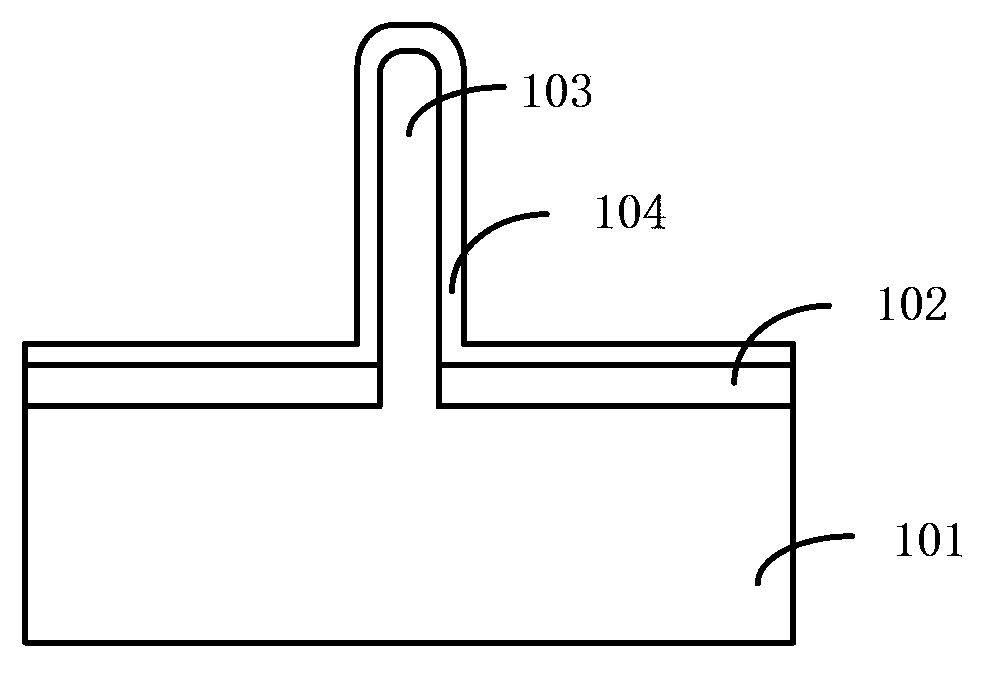

Floating gate flash memory device and programming method thereof

ActiveCN104377248AReduce the numberShorten the acceleration distanceTransistorSolid-state devicesGate oxideVoltage

The invention provides a floating gate flash memory device and a programming method of the floating gate flash memory device. The floating gate flash memory device comprise a substrate of a cylindrical structure, and a source end and a drain end are arranged at the two ends of the substrate; the middle of the substrate is covered with a grid, a gate oxide layer is arranged between the grid and the substrate, and the grid comprises a control gate and a floating gate. According to the programming method of the floating gate flash memory device, movement of hot electrons is assisted by applying bias voltage to provide sufficient energy to cross the gate oxide layer to complete compiling, the compiling efficiency of the flash memory is improved, and power consumption of compiling current is reduced; in addition, the floating gate flash memory device and the programming method of the floating gate flash memory device can effectively reduce the key size of the floating gate flash memory of a parse gate, increase the cell density of a flash memory array and namely increases the storage capacity and density of the flash memory.

Owner:SHANGHAI HUALI MICROELECTRONICS CORP

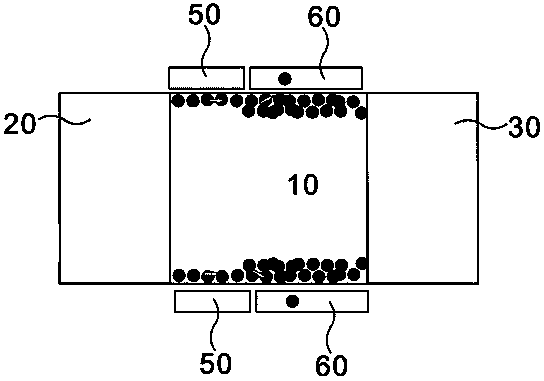

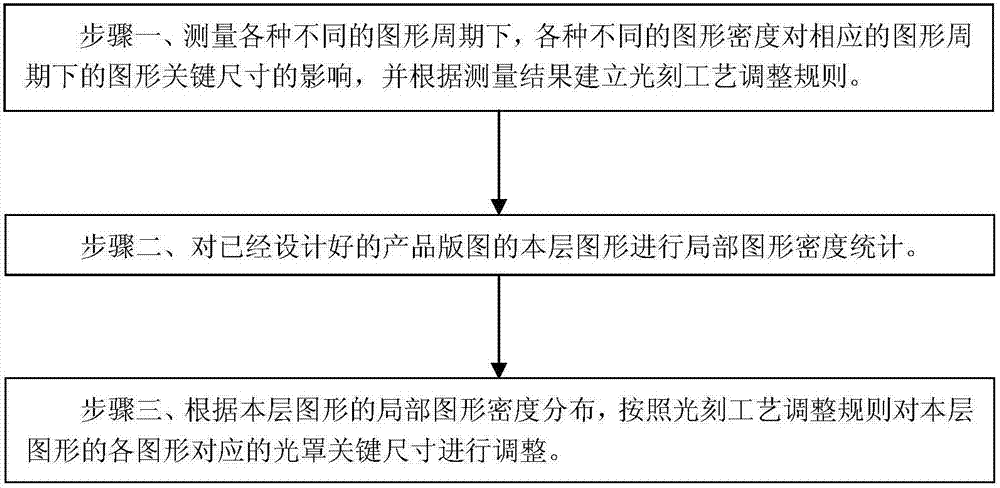

Method for improving uniformity of pattern critical dimensions in photoetching process

ActiveCN107121895AEliminate the effects ofReduce critical sizePhotomechanical exposure apparatusMicrolithography exposure apparatusLocal patternDensity distribution

The invention discloses a method for improving the uniformity of pattern critical dimensions in a photoetching process. The method comprises the following steps: 1, measuring the influence of various local pattern densities on the pattern critical dimensions in corresponding pattern periods in various pattern periods, and establishing a photoetching process regulation rule according to a measurement result; 2, making local pattern density statistics on local-layer patterns of a designed product layout; 3, regulating photomask critical dimensions corresponding to each pattern of the local-layer patterns according to a local pattern density distribution of the local-layer patterns and the photoetching process regulation rule. According to the method, the influence of changes of the local pattern densities in the layout on the pattern critical dimensions can be eliminated, each pattern critical dimension under the various local pattern densities tend to be the same as a design requirement, and the uniformity of the pattern critical dimensions is improved.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

Charge storage structure, manufacturing method thereof and nonvolatile memory structure

InactiveCN104183633AReduce critical sizePrevent protrusion defectsTransistorEngineeringStorage structure

Owner:WINBOND ELECTRONICS CORP

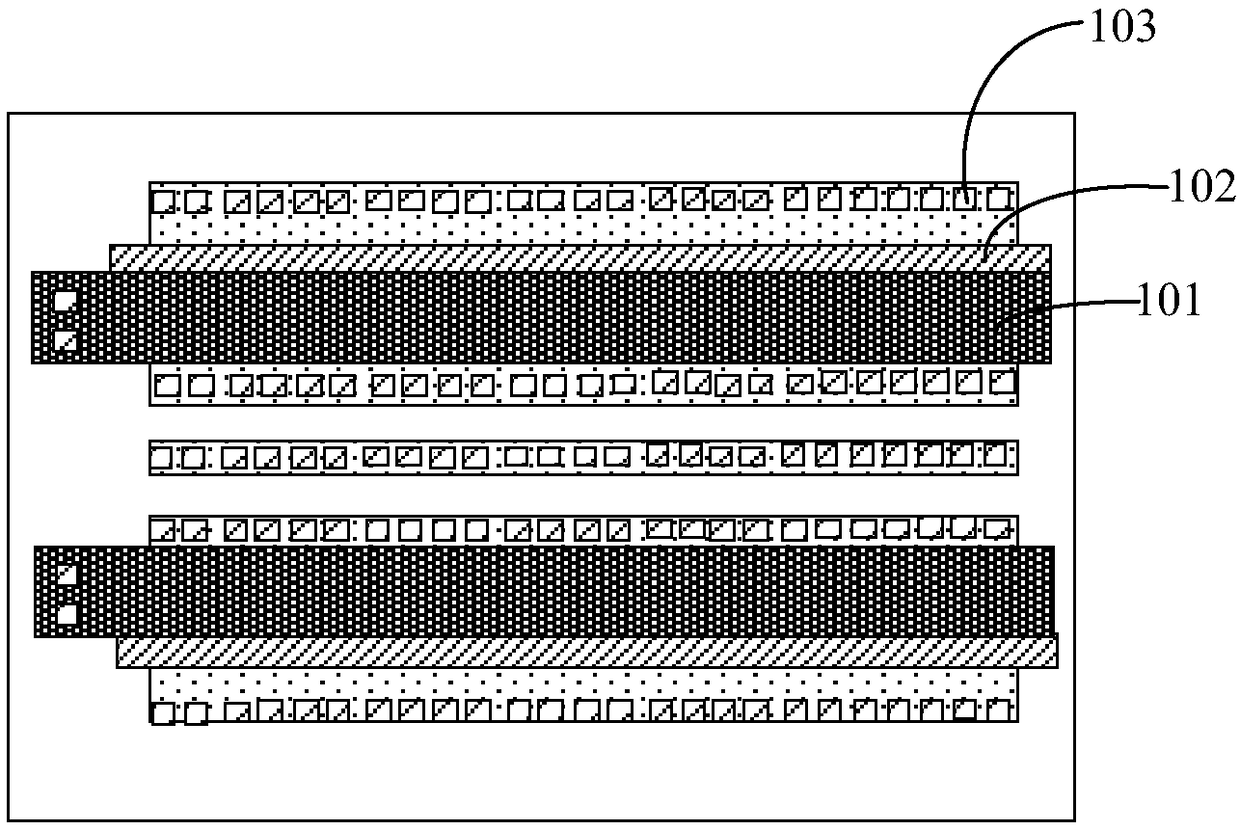

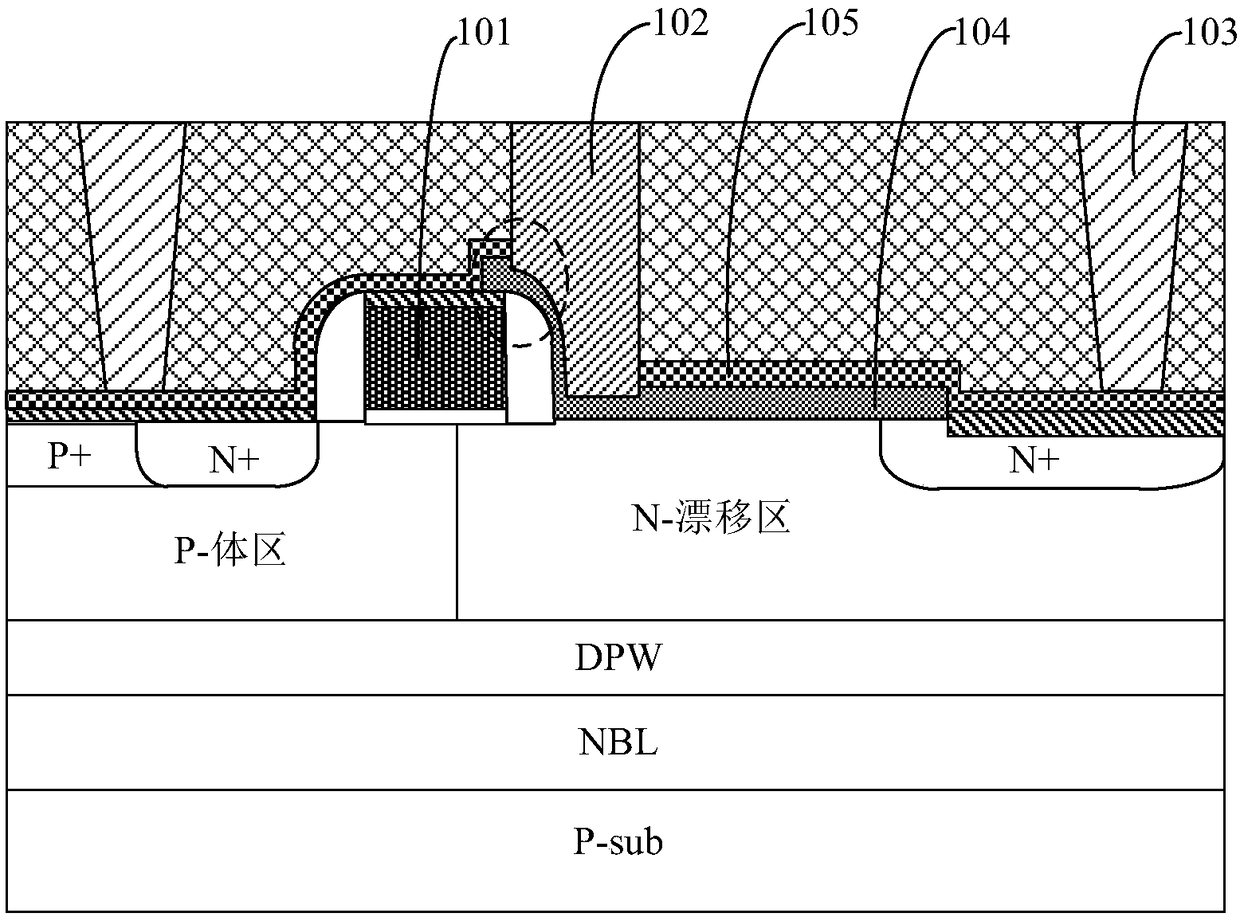

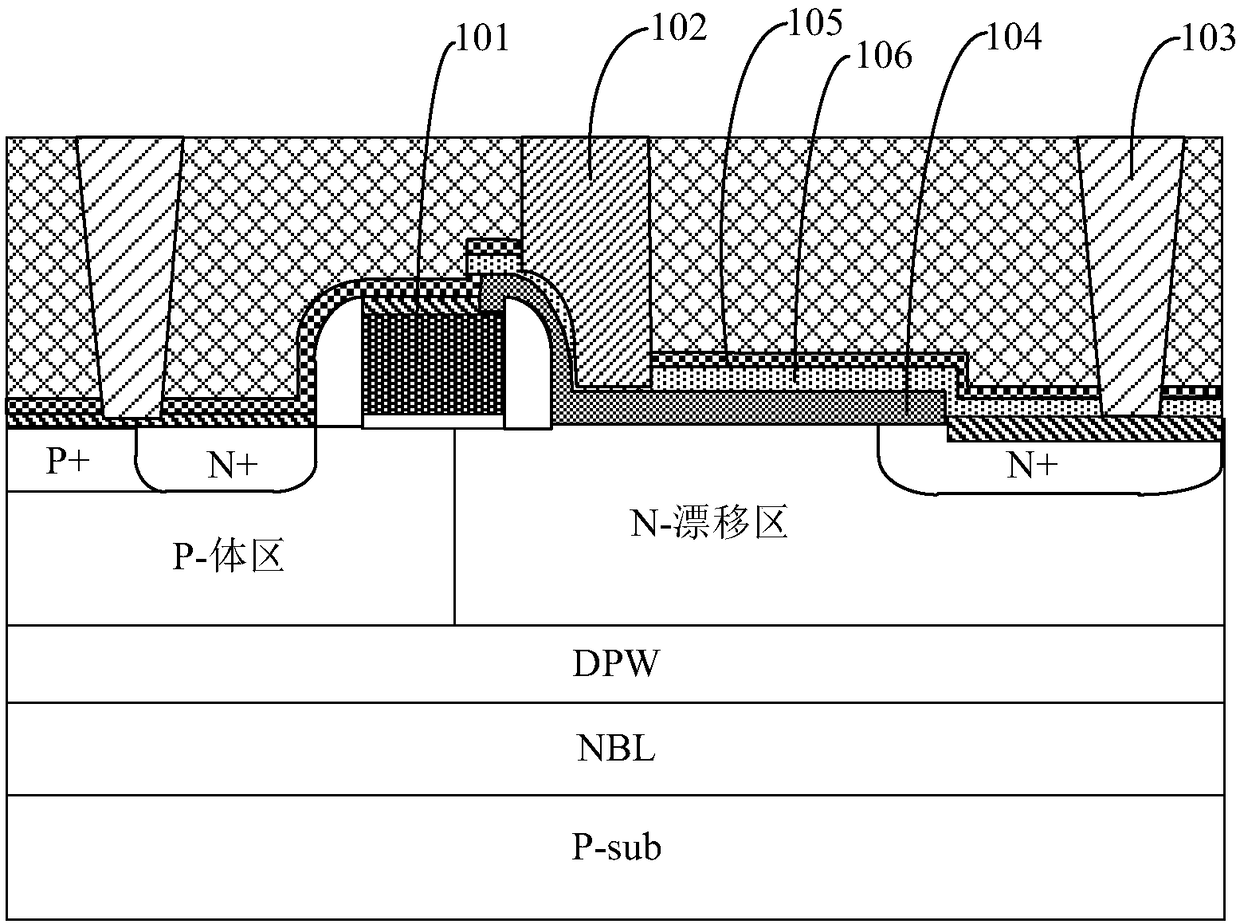

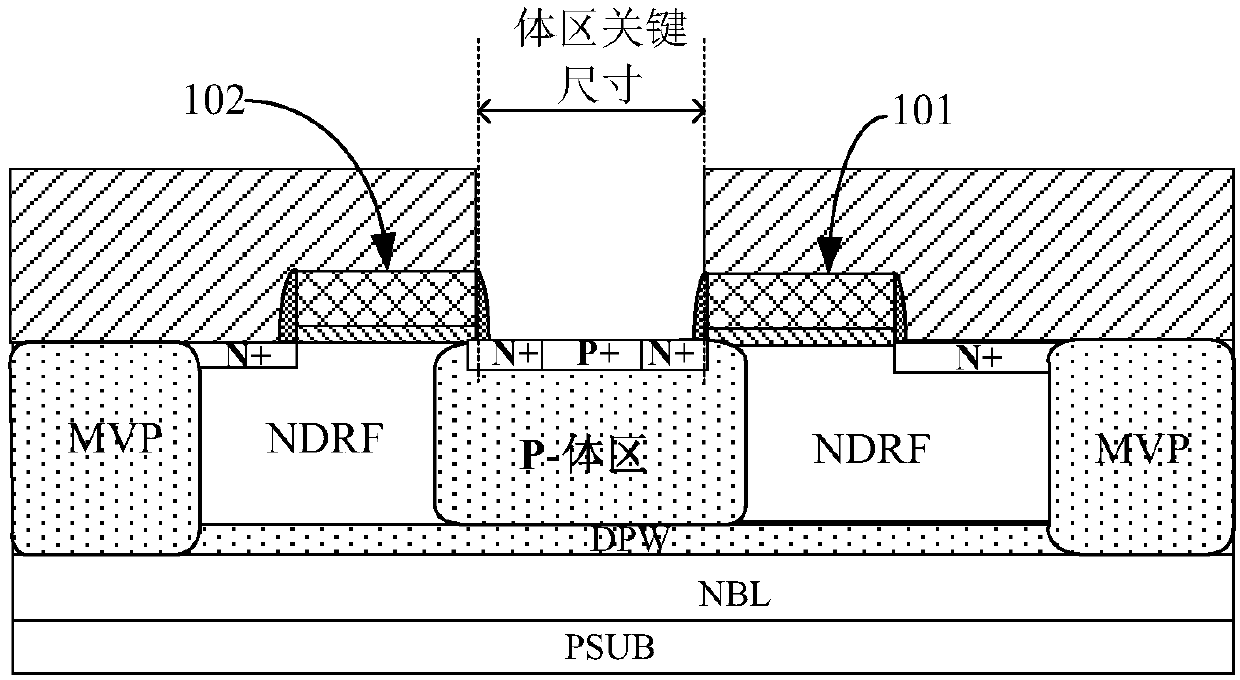

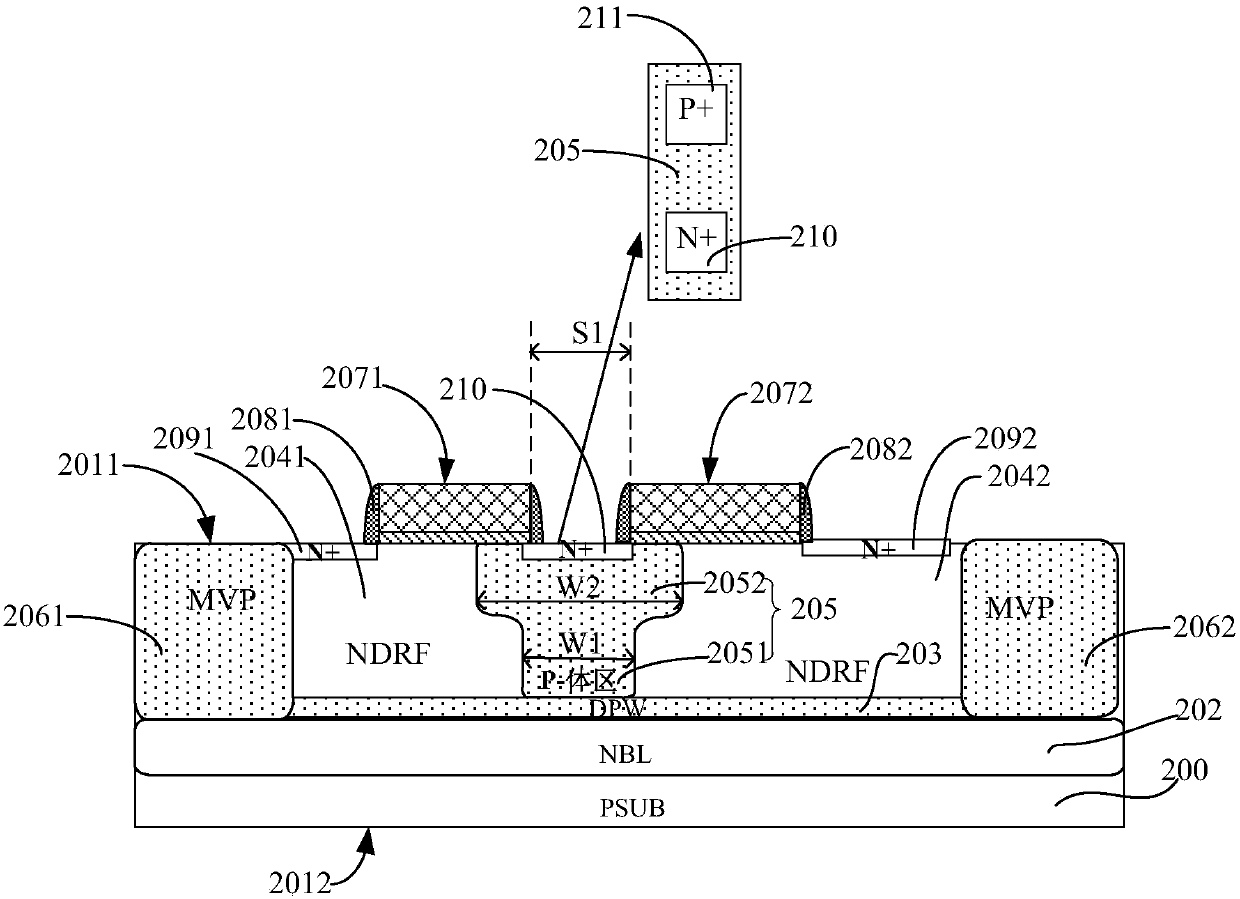

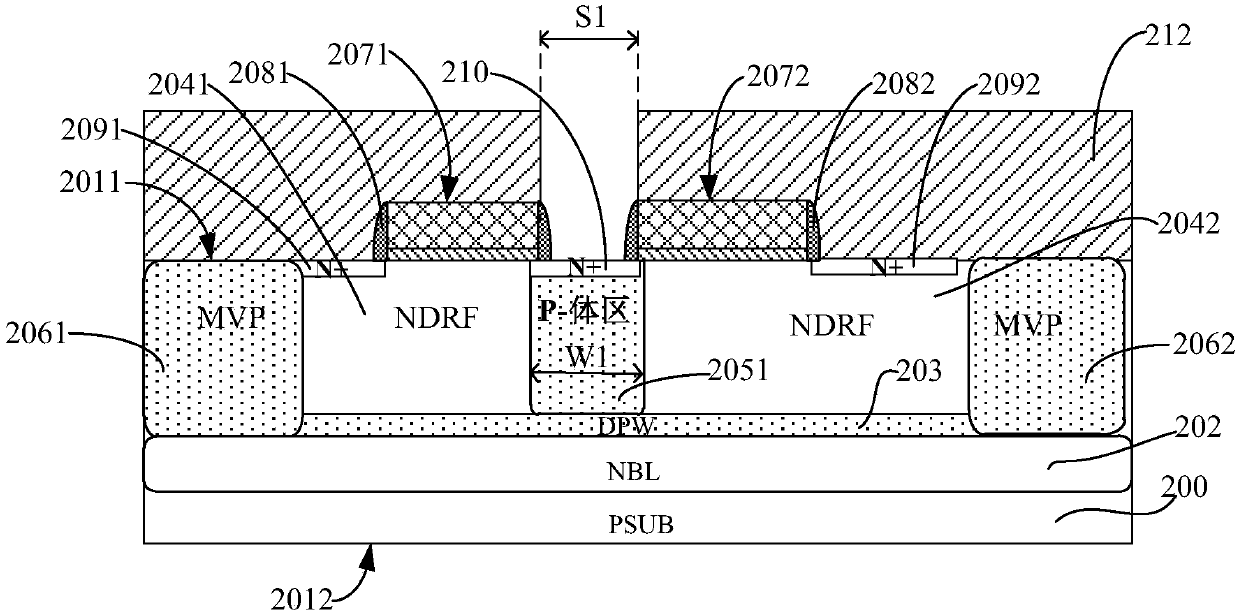

Semiconductor device and manufacturing method thereof, and electronic device

InactiveCN108122977ALower turn-on resistanceImprove performanceSemiconductor/solid-state device manufacturingSemiconductor devicesPower semiconductor deviceBody region

The invention provides a semiconductor device, a manufacturing method thereof and an electronic device, which relate to the technical field of semiconductors. The semiconductor device comprises a semiconductor substrate having a first conduction type, a body region having a first conduction type, a first gate structure and a second gate structure, wherein the body region is formed in the semiconductor substrate, the body region comprises a first portion and a second portion which is positioned on and adjacent to the first portion, the second portion is close to the first surface of the semiconductor substrate, the first portion extends for a first width along a first direction, the second portion extends for a second width along the first direction, and the first width is less than the second width; the first gate structure is arranged on the first surface of the semiconductor substrate, and partially extends onto the body region; and the second gate structure is arranged on the firstsurface of the semiconductor substrate, partially extends onto the body region, and is arranged along the first direction in a manner of being spaced from the first gate structure.

Owner:SEMICON MFG INT (SHANGHAI) CORP +1

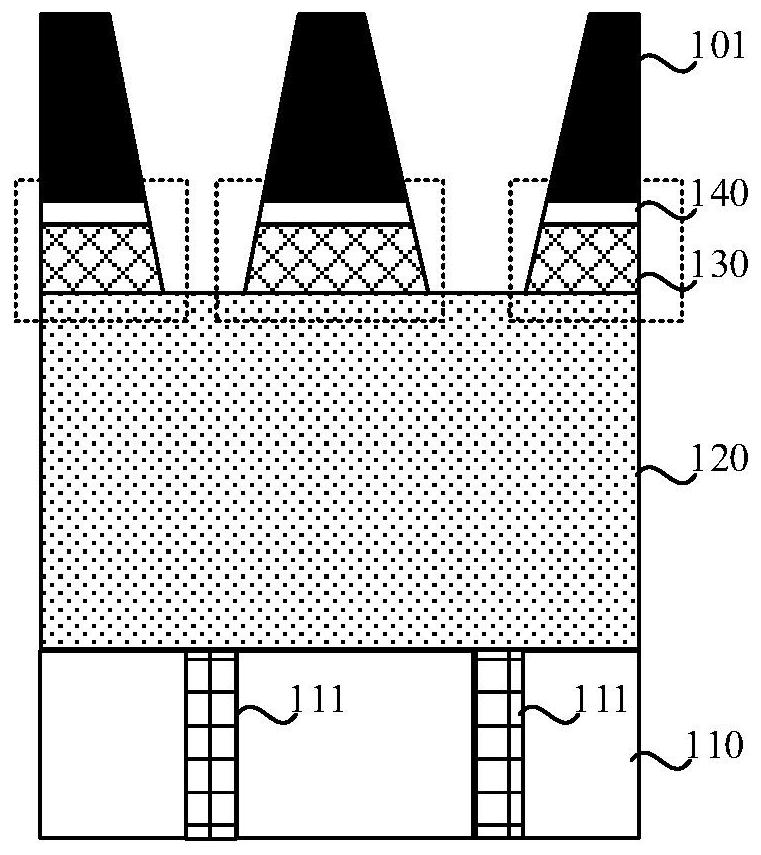

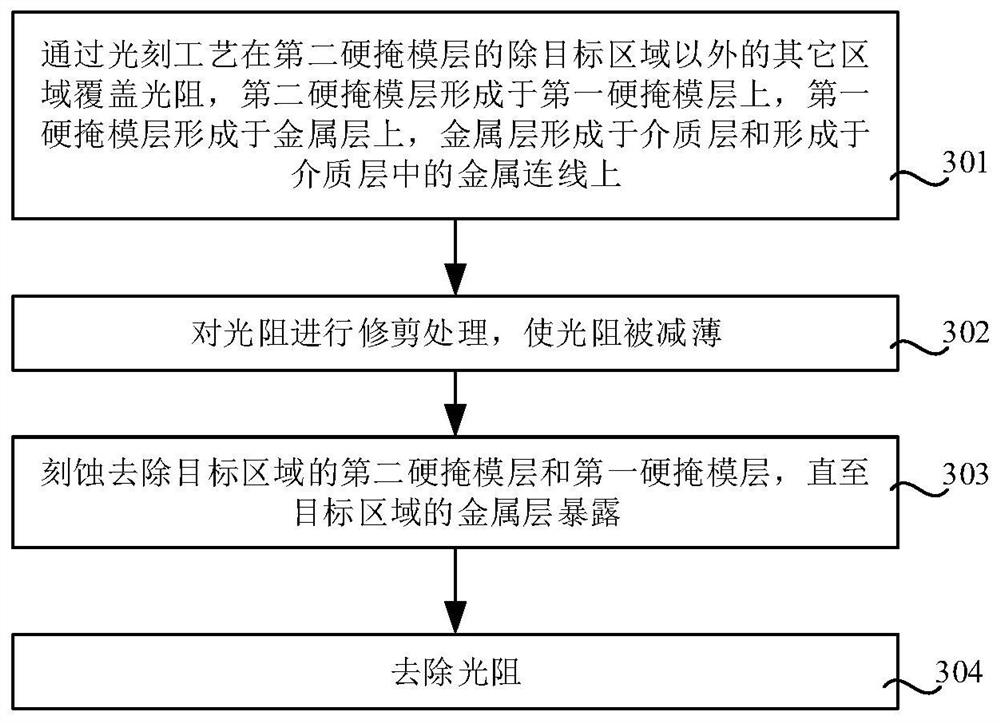

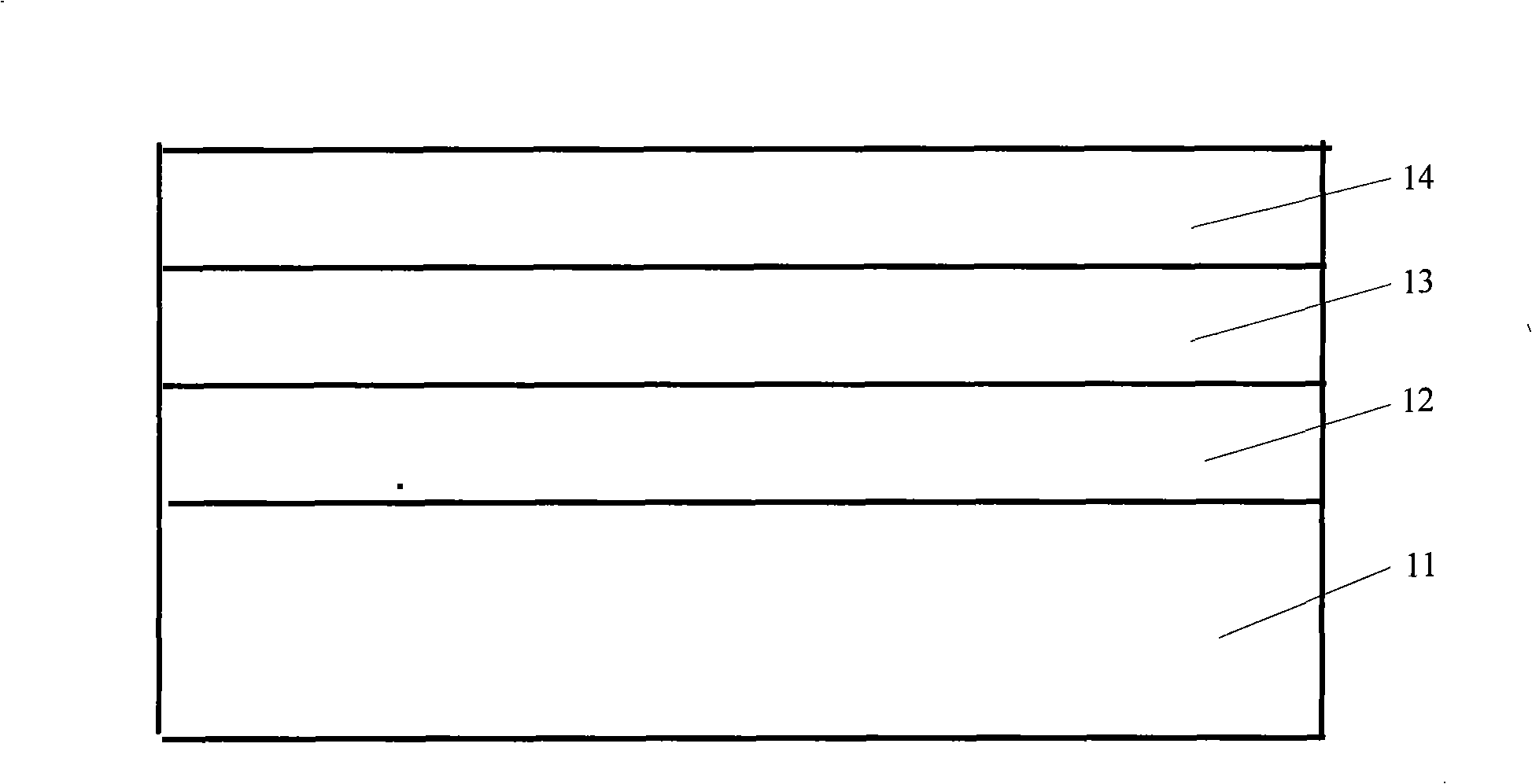

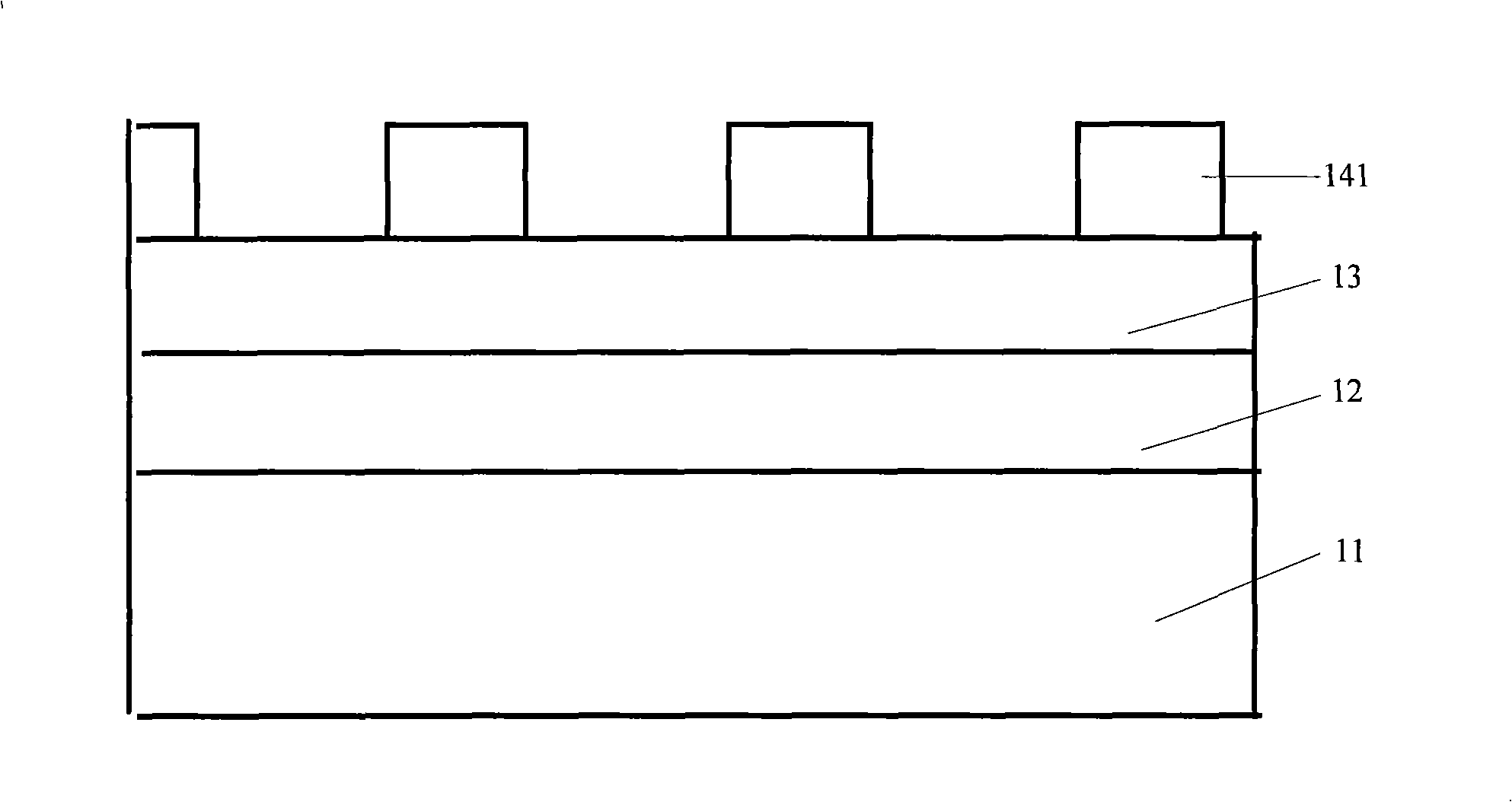

Etching method of metal interconnection structure

PendingCN111696917AGood lookingReduce critical sizeSemiconductor/solid-state device manufacturingChemistryPhotoresist

The invention discloses an etching method of a metal interconnection structure. The method comprises the following steps: covering a photoresist on other areas except a target area of a second hard mask layer through a photoetching process, forming the second hard mask layer on a first hard mask layer, forming the first hard mask layer on a metal layer, and forming the metal layer on a dielectriclayer and a metal connecting line formed in the dielectric layer; trimming the photoresist, so that the photoresist is thinned; carrying out etching to remove the second hard mask layer and the firsthard mask layer in the target area until the metal layer in the target area is exposed; and removing the photoresist. According to the invention, before the hard mask layer of the metal interconnection structure is etched, the hard mask layer is etched, the photoresist is trimmed, the critical size of the photoresist can be reduced in the initial process of subsequent etching, meanwhile, the sizeof the bottom of the photoresist can be reduced, and the roughness of the side wall of the photoresist is reduced, so that the subsequent etched structure has good morphology, and the stability and the manufacturing yield of the device are improved.

Owner:HUA HONG SEMICON WUXI LTD +1

Method for forming micro-graphic pattern on floating grid

InactiveCN101345215AReduce critical sizeReduce repetitive processing rateSemiconductor/solid-state device manufacturingWire widthReflux

The invention provides a method for forming micro-fine patterns on a floating grid, comprising the steps as follows: a multi-crystal silicon layer and a photoresist layer are sequentially formed on a silicon substrate where a floating grid is formed; the photoresist layer is exposed and developed; thermal reflux is carried out to the obtained photoresist patterns; by controlling the reflux temperature and the reflux time, the photoresist patterns with prearranged wire width and spacing are obtained; subsequently, the photoresist patterns with the prearranged wire width and the spacing is transferred to the multi-crystal silicon layer so as to carry out the subsequent preparation. By the method of the invention, patterns with the spacing of 80nm and less than 80nm on the floating grid, which can only be obtained by the more advanced ArF(ASML PAS / 1150C) scanner and ArF photoresist, can be obtained only by adopting the KrF(ASML PAS / 850c) scanner and thermal reflux KrF photoresist; furthermore, by comparison, the preparation process tolerance is more.

Owner:SEMICON MFG INT (SHANGHAI) CORP +1

Method for manufacturing ultra-small magnetic random access memory array

ActiveCN111490151AMiniaturizationEasy to manufactureMagnetic-field-controlled resistorsSolid-state devicesDielectricRandom access memory

The invention provides a method for manufacturing an ultra-small magnetic random access memory array. The method comprises the following steps: depositing a bottom electrode, a magnetic tunnel junction (MTJ), a hard mask and sacrificial mask layers on a substrate; graphically defining an MTJ pattern, and selectively and laterally demagnifying the hard mask and the sacrificial mask; etching the MTJuntil reaching the bottom electrode and maintaining a small amount of over-etching; depositing insulating layers, and enabling the thickness of the insulating layer on the bottom electrode etching front end and the sacrificial mask top to be greater than the thickness of the insulating layer on the side walls of the MTJ and the hard mask; trimming the side walls of the MTJ; depositing a self-aligning mask for etching the bottom electrode; etching the bottom electrode; and covering an insulating covering layer, and filling the dielectric and grinding the dielectric. According to the method, two times of etching are adopted when the MTJ and the bottom electrode are etched, so that the shadow effect is effectively reduced; and in addition, after the hard mask is etched, the transverse trimming process is added, so that the thickness of insulating layers deposited at the subsequent bottom electrode etching front end and the top end of the sacrificial mask is larger than the thickness of insulating layers deposited on the side walls of the MTJ and the side walls of the hard mask, and trimming efficiency is greatly improved.

Owner:SHANGHAI CIYU INFORMATION TECH CO LTD

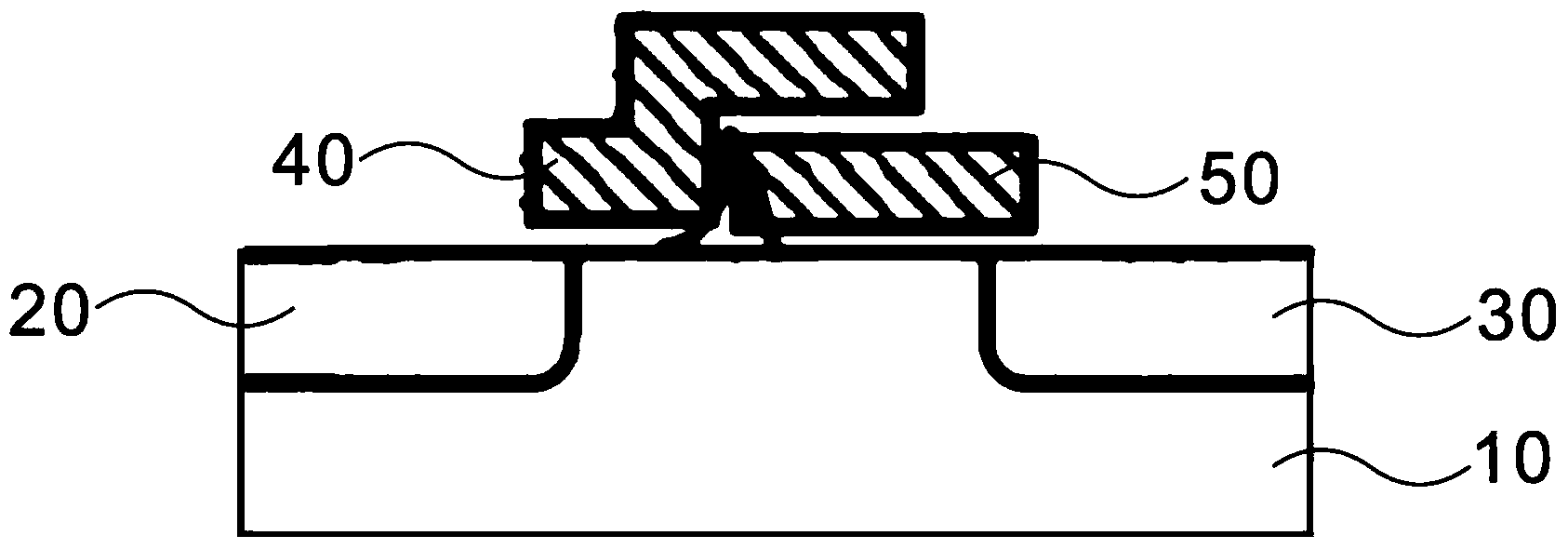

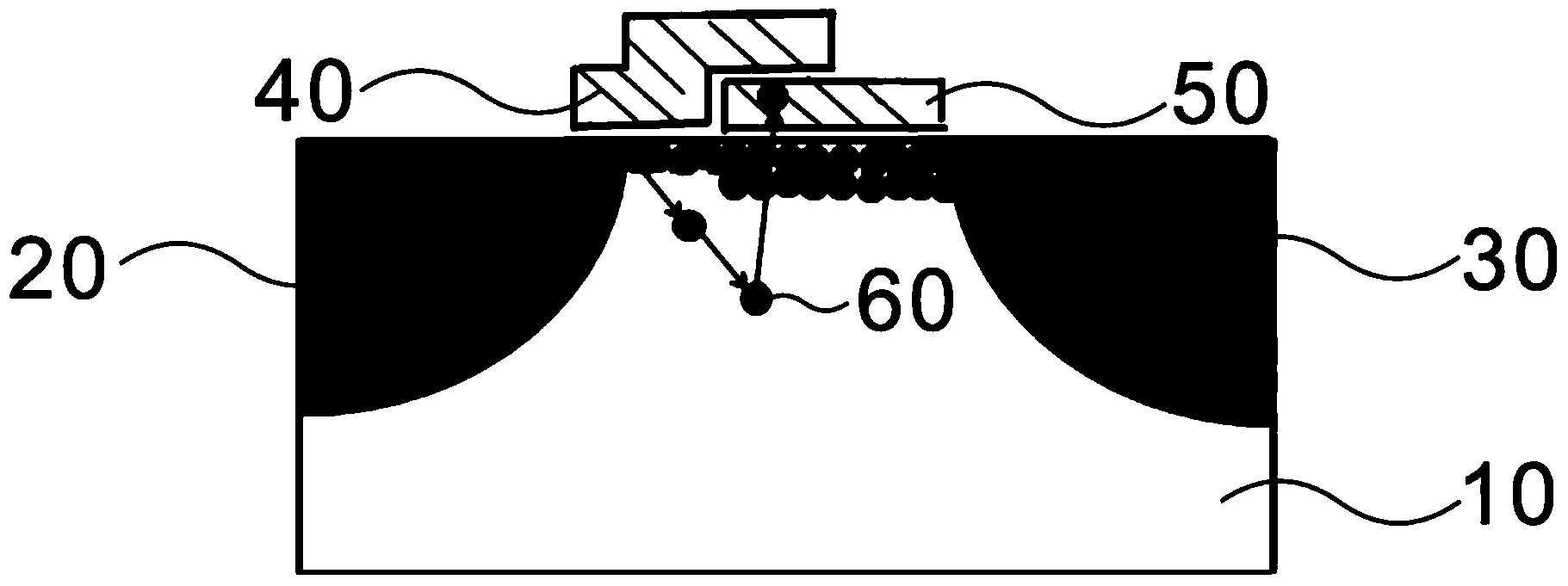

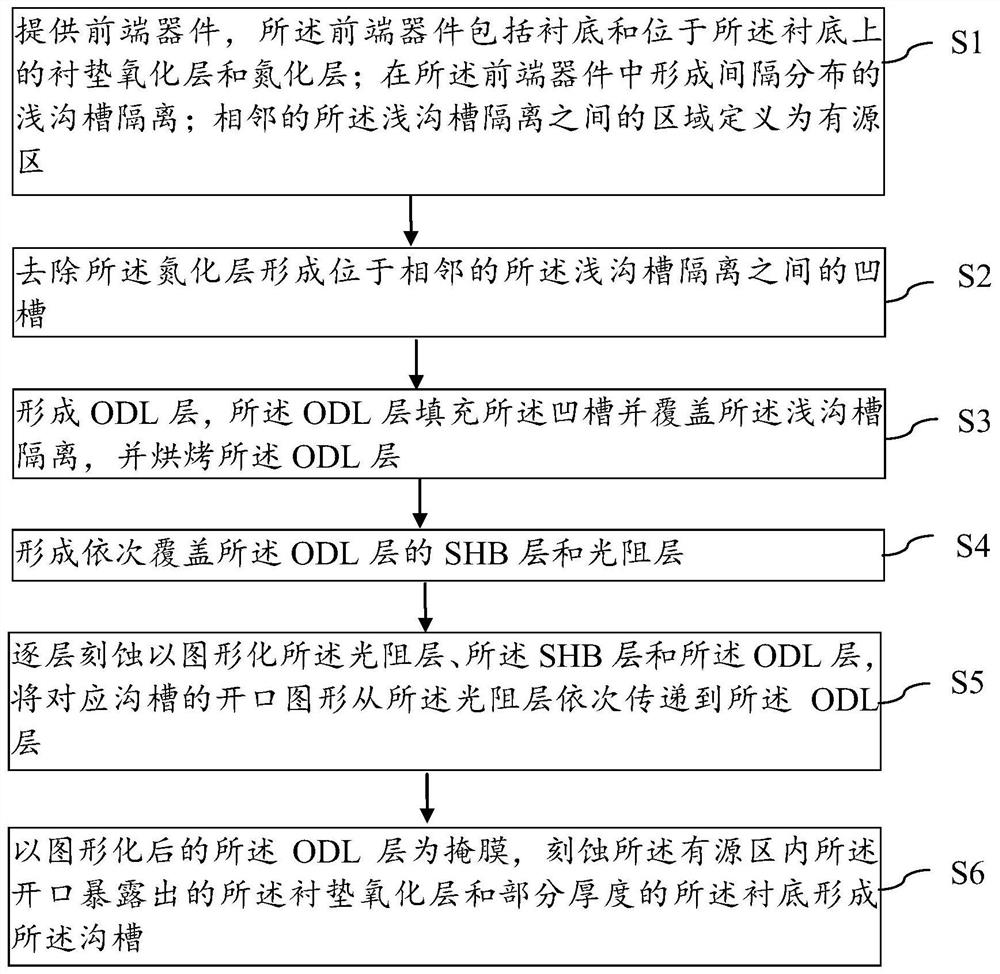

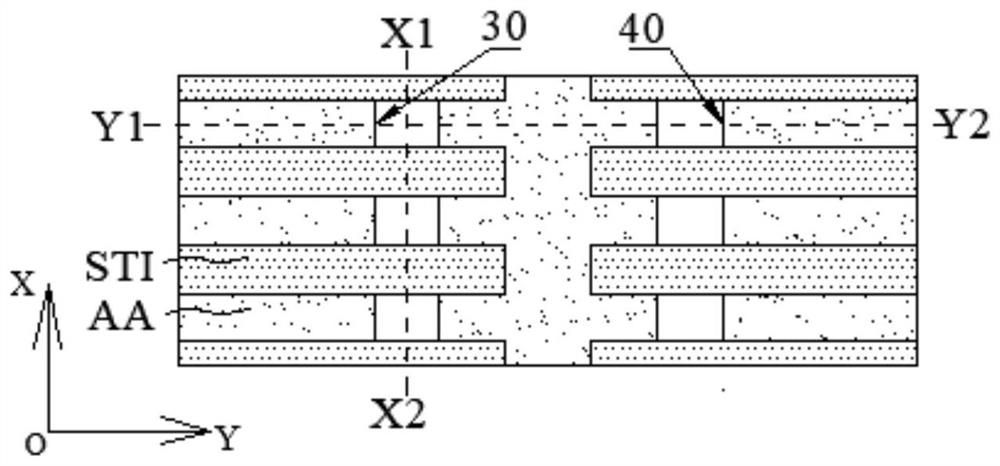

Manufacturing method of trench and manufacturing method of memory device

PendingCN114005750APrecise control of key dimensionsReduce critical sizeSolid-state devicesSemiconductor/solid-state device manufacturingEngineeringPhotoresist

The invention provides a manufacturing method of a trench and a manufacturing method of a memory device. A mask layer comprises an amorphous carbon layer and a DARC layer which are stacked, and the amorphous carbon layer covers a shallow trench isolation layer and a nitride layer; before the mask layer is formed, the nitride layer is not removed, pits are prevented from being formed, the advantage of the high vertical and horizontal etching selection ratio of the amorphous carbon layer is utilized, and the defect that the filling capacity of the amorphous carbon layer is poor is overcome. According to the method, the photoresist layer and the mask layer are etched layer by layer to pattern the photoresist layer and the mask layer, the corresponding opening of the groove is etched by adopting a multi-layer film layer structure formed by overlapping the mask layer and the photoresist layer, and the pattern and size of the opening are sequentially transmitted, so that the resolution and fidelity of the opening pattern are improved, and the accurate control of the key size of the opening pattern is realized. Therefore, the key size of the trench can be accurately controlled, and the key size of the trench can be further reduced. The key size of the trench is reduced, and the channel length of the memory device is correspondingly reduced, so that the effective current and the read window of the memory device can be increased.

Owner:WUHAN XINXIN SEMICON MFG CO LTD

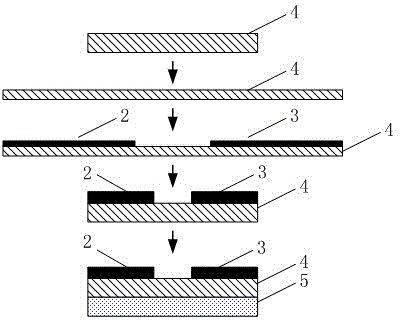

Preparation method of thin film transistor of flexible electronic device

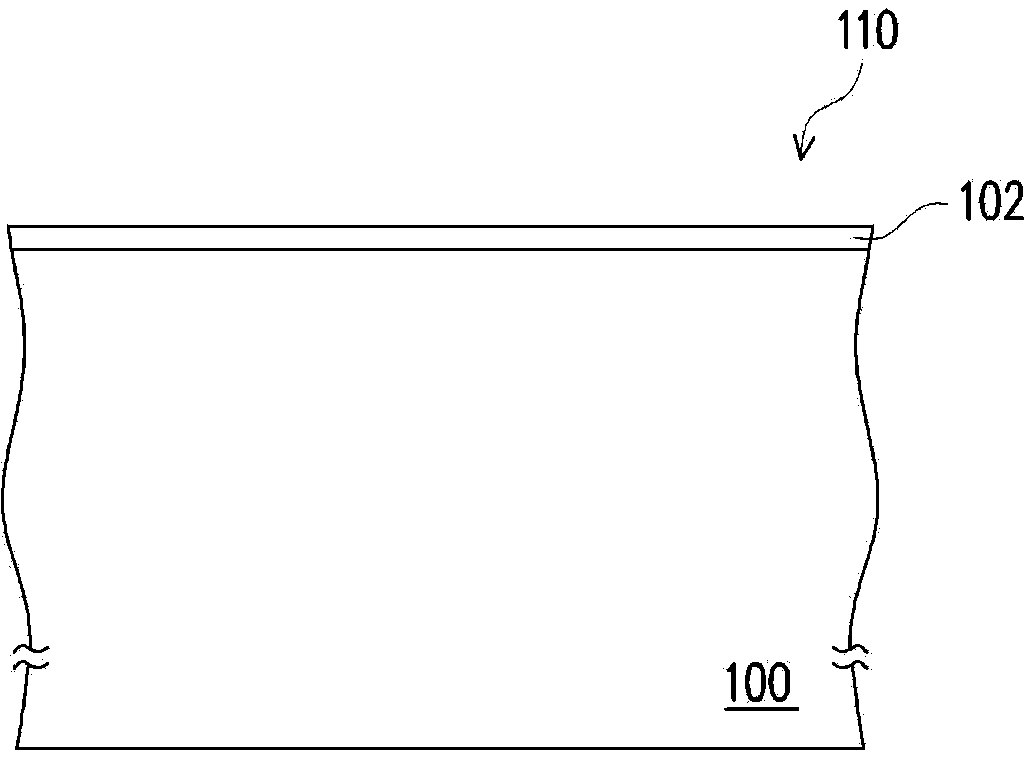

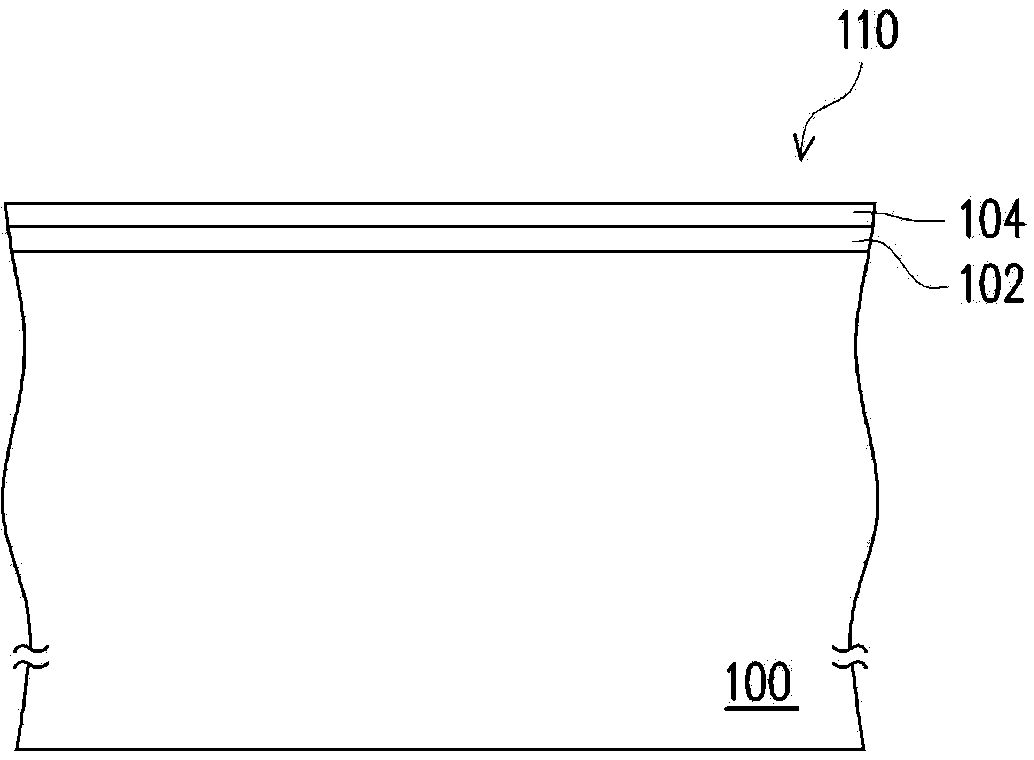

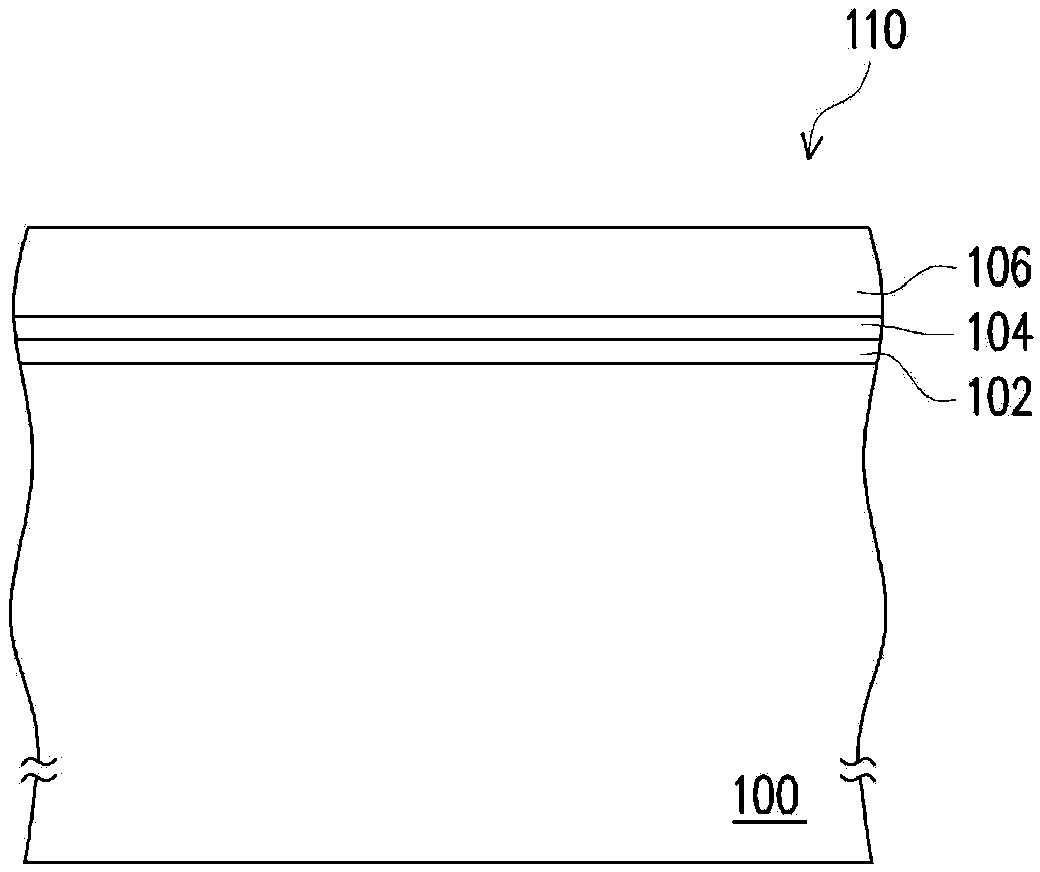

ActiveCN102169960BAchieving autofocusNo change in footprintSolid-state devicesSemiconductor/solid-state device manufacturingAdhesiveEngineering

The invention provides a preparation method of a thin film transistor of a flexible electronic device. The method comprises the following steps of: (1) preparing a bendable and stretchable substrate; (2) stretching the substrate, and coating an adhesive on a surface of a stretched rubber substrate; (3) depositing a gate on the substrate; (4) depositing an organic dielectric layer unit on the device which is processed in the step (3); (5) respectively depositing a source unit layer and a drain unit layer on the organic dielectric layer unit; (6) loosening the substrate, releasing loads which are acted on the substrate, and carrying out heat treatment to eliminate an interface stress and a pressure stress of the device; and (7) depositing the organic dielectric layer unit. The invention provides the method for mechanically stretching the substrate, so the channel width of the device is reduced, manufacturing accuracy is improved effectively, and the resolution ratio of the flexible electronic device is improved.

Owner:WUHAN INTELLIGENT EQUIP IND INST CO LTD

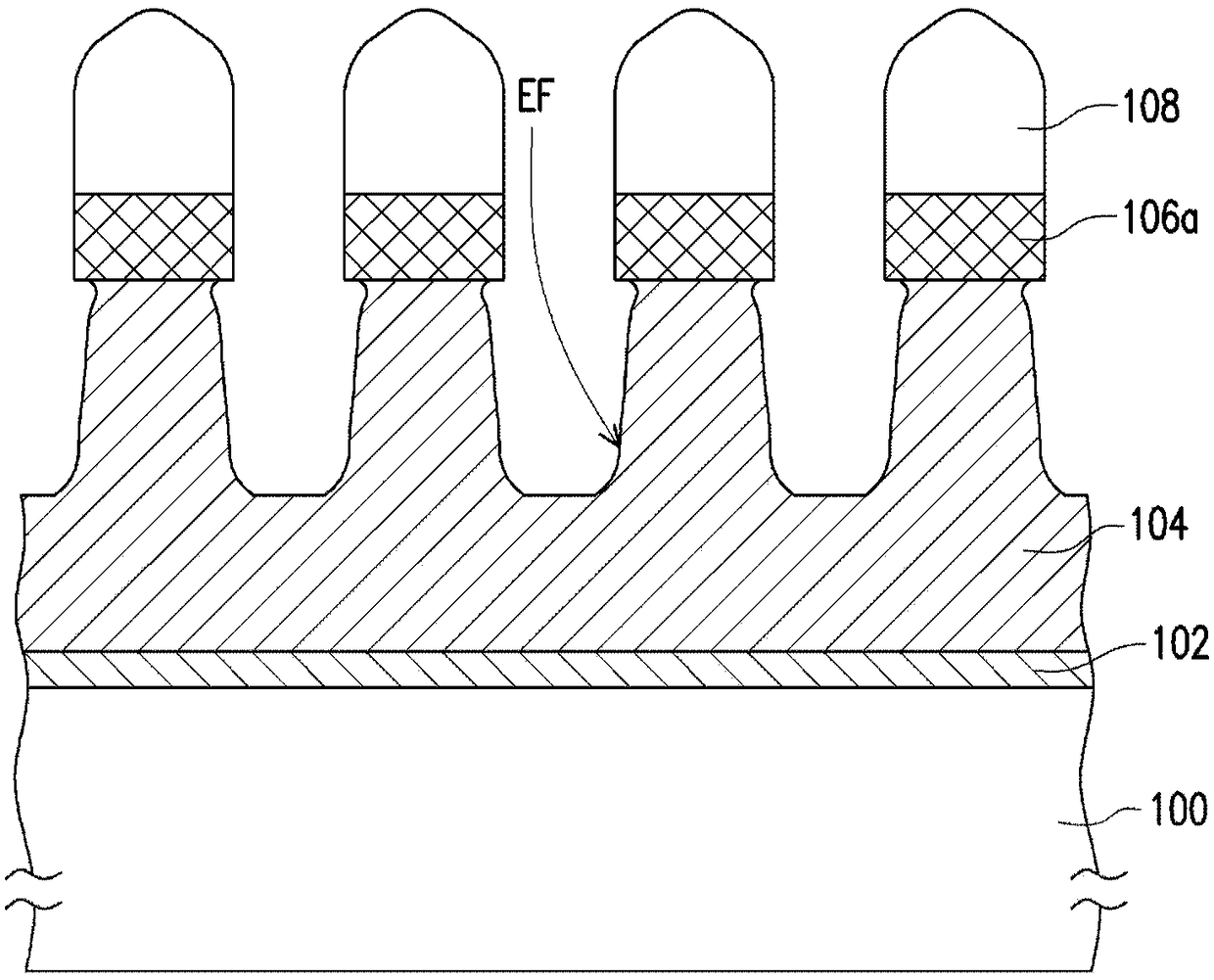

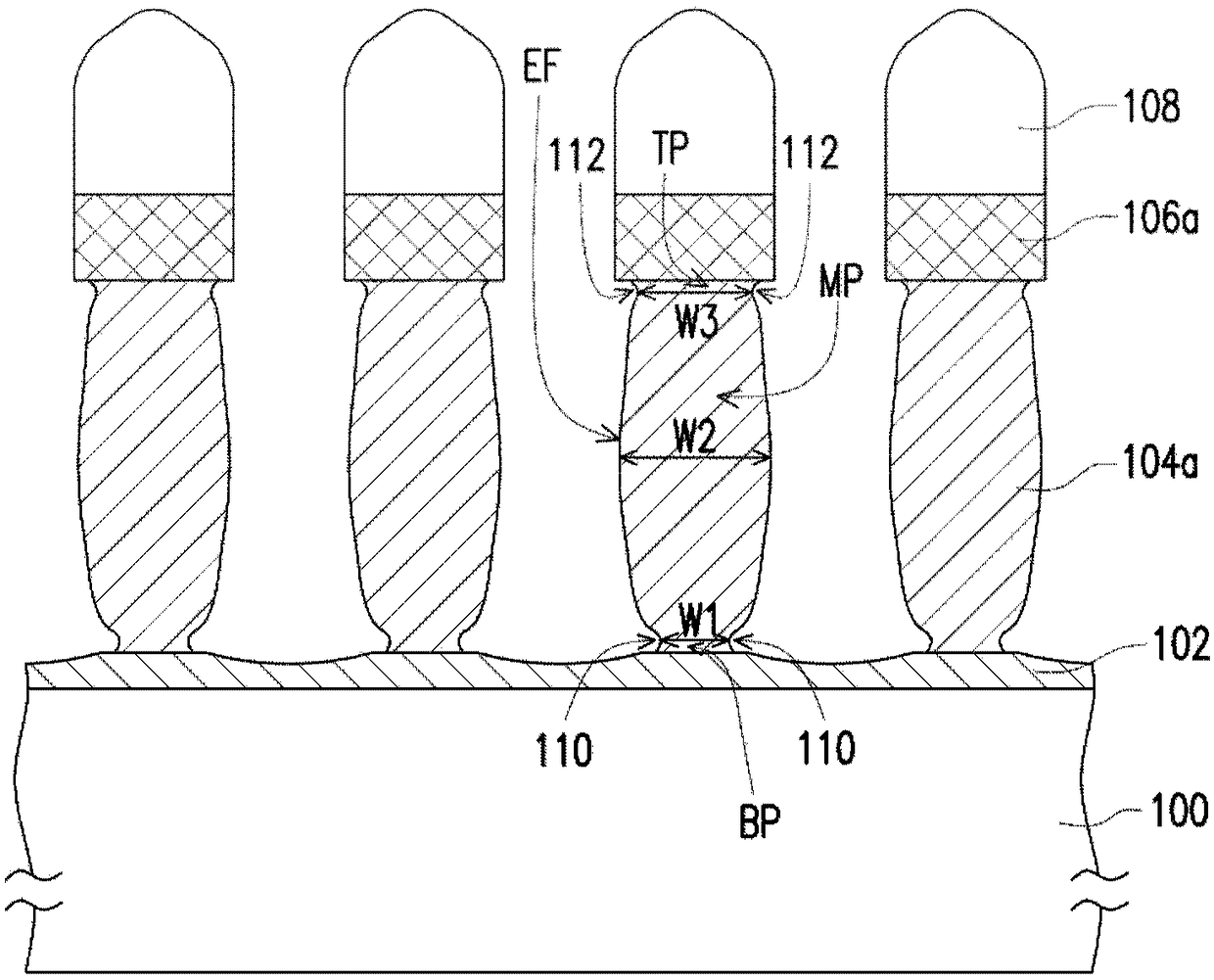

Interconnection structure and manufacturing method thereof

ActiveCN108400128AReduce critical sizeIncrease Overlap MarginSemiconductor/solid-state device detailsSolid-state devicesInterconnectionEngineering

An interconnection structure comprises a substrate and a conductive pattern, wherein the conductive pattern comprises a bottom part, the bottom part of the conductive pattern is arranged on a substrate, and the conductive pattern is provided with gaps in two side walls of the bottom part.

Owner:MACRONIX INT CO LTD

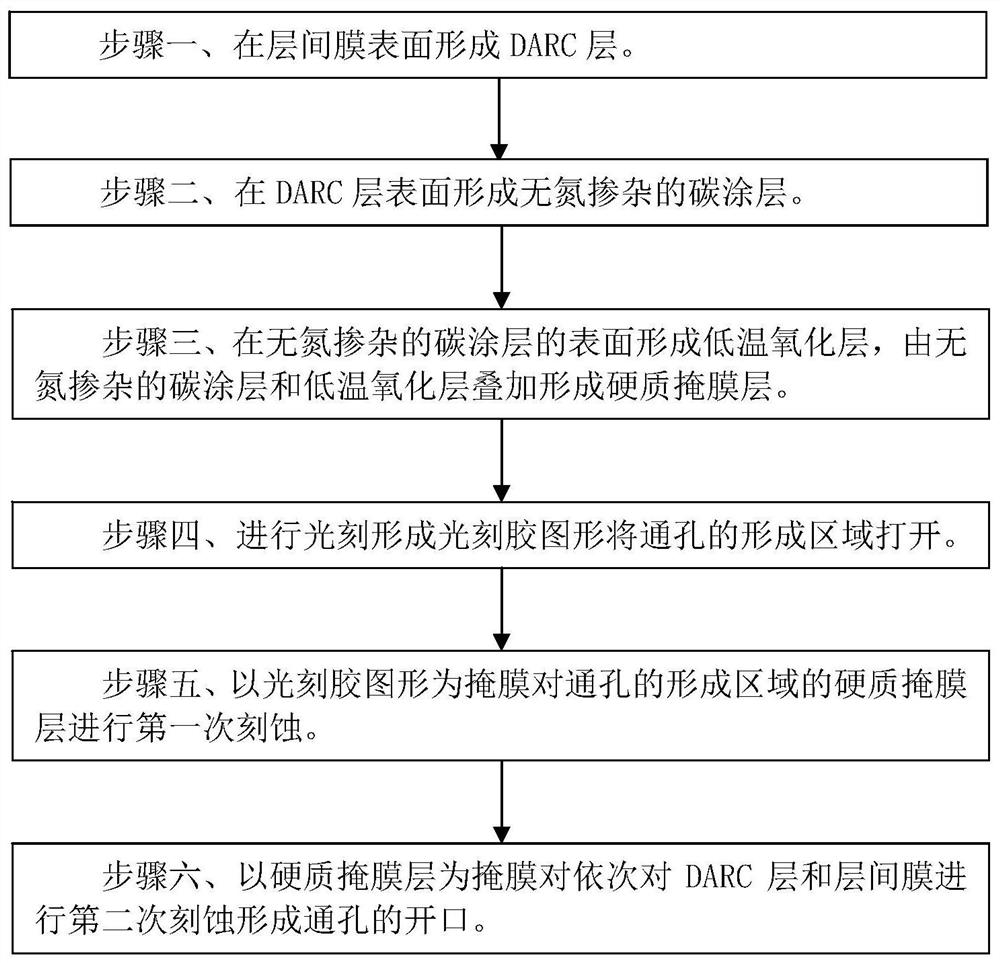

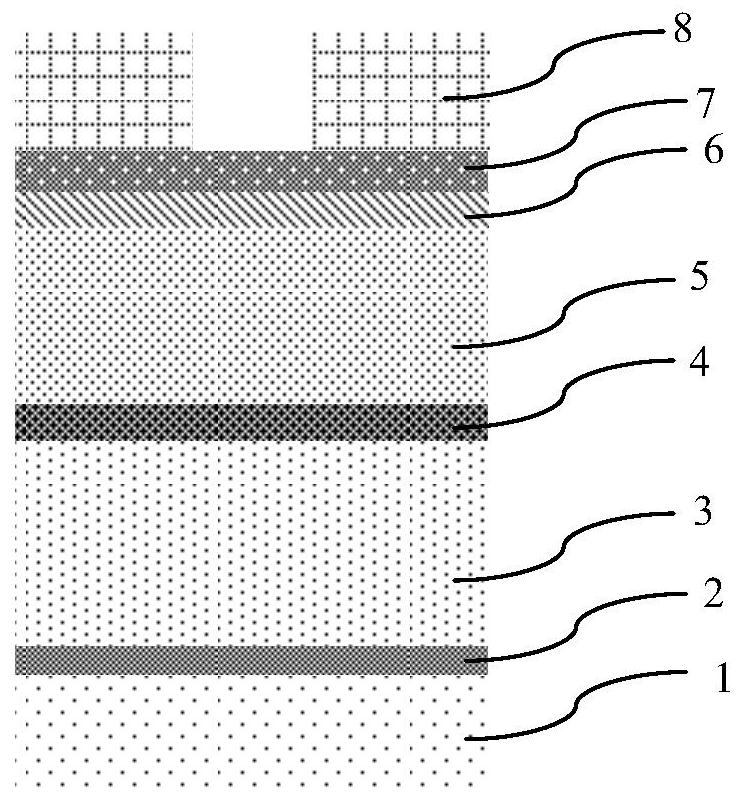

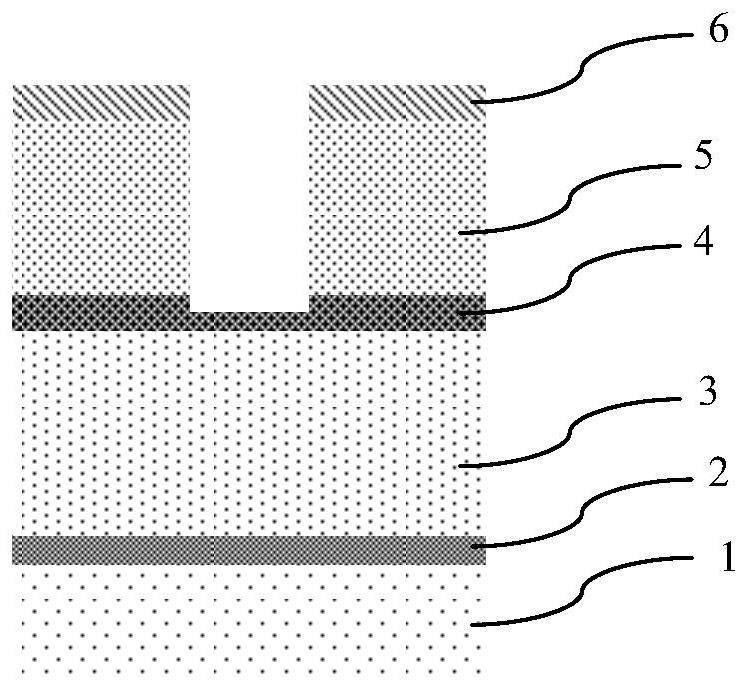

Manufacturing method of through hole

InactiveCN112635397AReduce critical sizeSmall sizeSemiconductor/solid-state device manufacturingMembrane surfacePhotoresist

The invention discloses a manufacturing method of a through hole. The manufacturing method comprises the following steps: 1, forming a DARC layer on the surface of an interlayer film; 2, forming a nitrogen-free doped carbon coating on the surface of the DARC layer; 3, forming a low-temperature oxide layer on the surface of the nitrogen-free doped carbon coating, and superposing the nitrogen-free doped carbon coating and the low-temperature oxide layer to form a hard mask layer; 4, carrying out photoetching to form a photoresist pattern, and opening a forming area of the through hole; 5, performing first etching on the hard mask layer in the forming area of the through hole by taking the photoresist pattern as a mask; and 6, etching the DARC layer and the interlayer film for the second time in sequence by taking the hard mask layer as a mask to form an opening of the through hole. According to the invention, the through hole with small size and high depth-to-width ratio can be obtained.

Owner:HUA HONG SEMICON WUXI LTD +1

Programming method for flash memory device

ActiveCN104183273AShorten the critical dimensionIncrease cell densityRead-only memoriesControl gridUnit device

Owner:SHANGHAI HUALI MICROELECTRONICS CORP

Manufacturing method of groove and manufacturing method of memory device

PendingCN114005749AGood plasma resistanceLateral etch rate weakensSolid-state devicesSemiconductor/solid-state device manufacturingWaferElectrical performance

The invention provides a manufacturing method of a groove and a manufacturing method of a memory device. The manufacturing method comprises the following steps: providing a front-end device; forming an ODL layer; baking the ODL layer to enable the ODL layer to be more compact, and weakening the lateral etching rate; the opening of the corresponding groove formed in the ODL layer does not expand outwards and being not etched laterally, so that the key size of the opening corresponding to the groove is effectively controlled. A photoresist layer, an SHB layer and an ODL layer are etched layer by layer to pattern the photoresist layer, the SHB layer and the ODL layer, a multi-layer film layer structure is adopted to etch corresponding openings of a groove, the patterns and sizes of the openings are transmitted in sequence, the resolution and fidelity of the patterns of the openings are improved, accurate control over the key sizes of the patterns of the openings is achieved, and therefore the key sizes of the groove can be accurately controlled, and the key size of the groove can be further reduced. The key size of the groove is reduced, the channel length of the memory device is correspondingly reduced, a semi-floating gate buried channel with small size and effective vertical morphology is formed, the electrical performance of the semi-floating gate device is improved, and the yield of a memory device wafer is improved.

Owner:WUHAN XINXIN SEMICON MFG CO LTD

Method for shortening analytic period of mfg. process

InactiveCN1466171AReduce critical sizeImprove qualityPhotomechanical apparatusSemiconductor/solid-state device manufacturingComputational physicsSecondary phase

This invention relates to a method for reducing an analytical period of a process including: using a light mask to form a first light resistance layer on part of a basic material and a first material layer on sidewall of the layer, removing the first layer to form a first material layer on part of the basic material at the first stage, carrying out a second process to form a second light resistance layer on the first material layer sidewall, removing the first light resistance layer to form a ditch on the basic material and form a second material layer on sidewall of the ditch, finally, removing the second light resistance layer to form a complex layer of the first and second material layers, so, the first and second layer and contacted together.

Owner:MACRONIX INT CO LTD

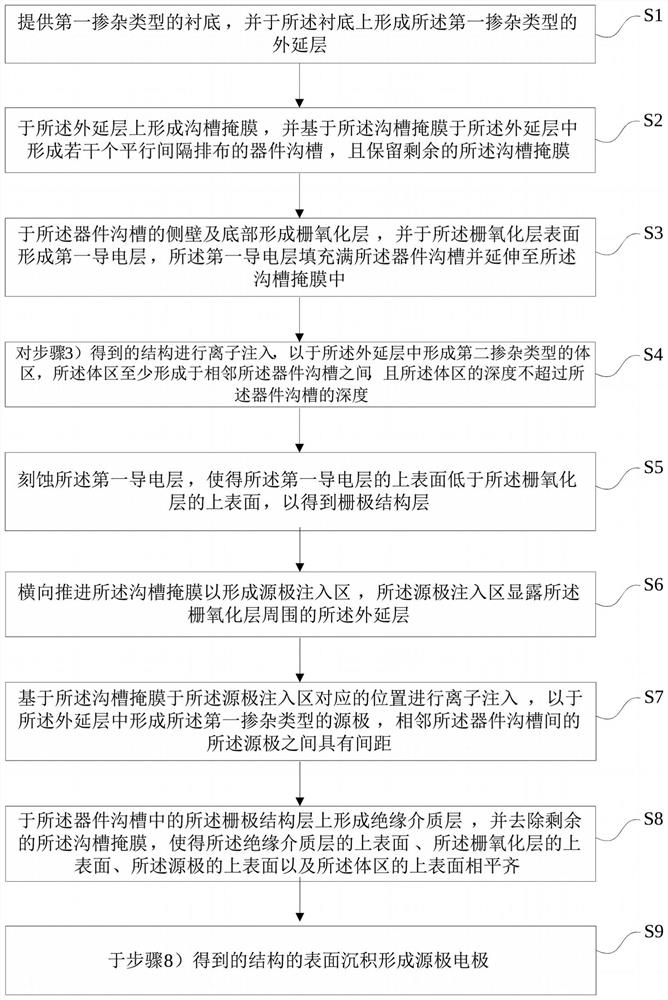

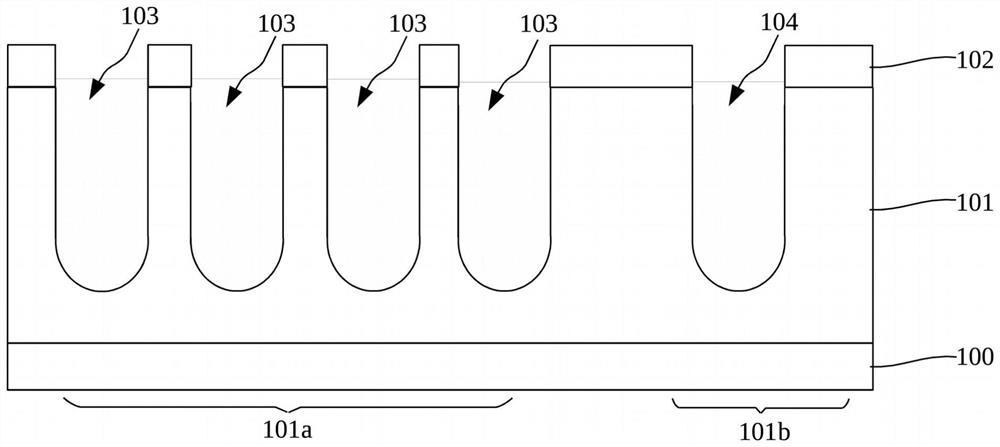

Trench type field effect transistor structure and preparation method thereof

ActiveCN112530867AHigh densityReduce critical sizeTransistorSemiconductor/solid-state device manufacturingEngineeringField effect

The invention provides a trench type field effect transistor structure and a preparation method thereof. The preparation method comprises the steps: providing a substrate of a first doping type, forming an epitaxial layer of the first doping type, forming a trench mask, forming a device trench, forming a gate oxide layer, forming a first conductive layer, forming a body region of a second doping type, forming a source injection region, forming a source electrode of the first doping type based on the trench mask, forming an insulating dielectric layer, enabling the upper surface of the insulating dielectric layer, the upper surface of the gate oxide layer, the upper surface of the source electrode and the upper surface of the body region to be flush, and forming a source electrode. According to the invention, the advantages of a self-alignment process are retained, cell density is effectively increased, a transistor structure and process are improved, the effective electrical extractionof the source electrode and the body region is realized, the key size of a cell is reduced, the electrical extraction mode of the source electrode and the body region is changed while the cell density is improved, the EAS capability of a device is improved, the doping uniformity of the body region is improved, and an extra body region leading-out region does not need to be prepared.

Owner:CHINA RESOURCES MICROELECTRONICS (CHONGQING) CO LTD

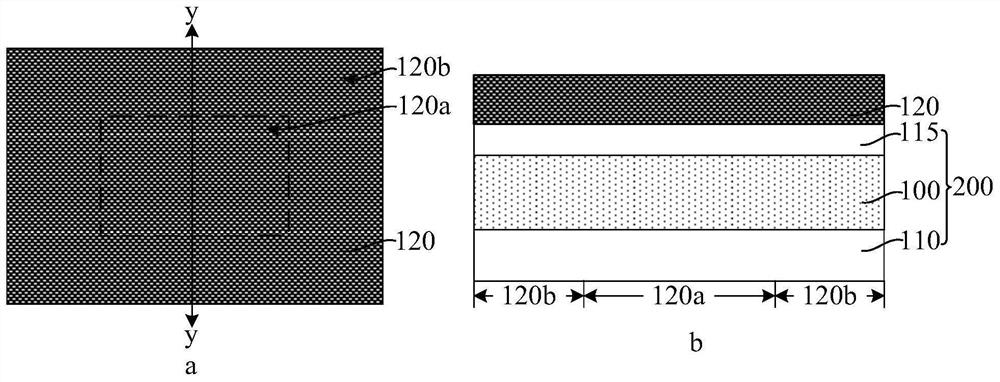

Formation method of semiconductor structure and mask

PendingCN114388430AReduce critical sizeHigh densitySolid-state devicesSemiconductor/solid-state device manufacturingSemiconductor structureStructural engineering

The invention discloses a semiconductor structure forming method and a mask, and the method comprises the steps: providing a substrate which comprises a target layer; forming a core material layer on the substrate, wherein the core material layer comprises a first region and a second region surrounding the first region; ion doping is carried out on the core material layer of the second area, the etching resistance of the core material layer is improved, the core material layer located in the second area serves as an etching resistance layer, and the core material layer located in the first area serves as a core layer; forming a first groove penetrating through at least part of the core material layer in the first region along the first direction, and reserving part of the core material layer in the first region on two sides of the first groove in the second direction; a side wall is formed on the side wall of the first groove, so that a first groove is defined by the side wall; removing the core layer to form a second groove; and etching the target layer below the first groove and the second groove by taking the anti-etching layer and the side wall as masks to form a target pattern. The embodiment of the invention is beneficial to further compressing the pitch between the target patterns.

Owner:SEMICON MFG INT (SHANGHAI) CORP +1