Method for manufacturing ultra-small magnetic random access memory array

A random access memory, ultra-small technology, applied in the fields of magnetic field-controlled resistors, electric solid-state devices, semiconductor devices, etc., can solve the problems of reduced sidewall trimming efficiency, difficult sidewall damage, etc., to improve trimming efficiency and reduce shadows effect, reducing the effect of redeposition

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

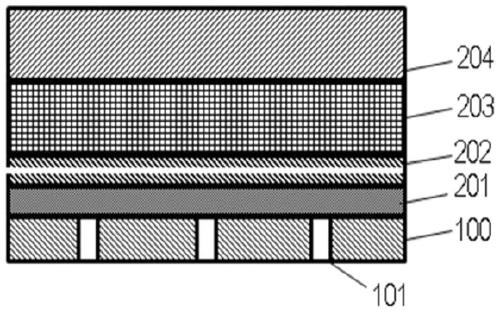

[0051] Step 1, such as figure 1 As shown, a substrate 100 with a surface-polished CMOS VIA101 is provided, and a bottom electrode 201 , a magnetic tunnel junction 202 of a multilayer film structure, a film layer of a hard mask 203 and a film layer of a sacrificial mask 204 are deposited on the substrate.

[0052] Among them, the thickness of the bottom electrode is 5nm-80nm, and its constituent materials are Ti, TiN, Ta, TaN, W, WN or any combination thereof, generally using physical vapor deposition (Physical Vapor Deposition, PVD), usually after deposition, Chemical-mechanical polishing is performed on it to achieve surface flatness for making magnetic tunnel junctions.

[0053] The multilayer film thickness of the magnetic tunnel junction (MTJ) 202 is 8nm-40nm, which can be a bottom pinned (Bottom Pinned) structure consisting of a reference layer, a barrier layer and a memory layer stacked upwards in sequence, or a memory layer, a barrier layer Layers and reference layers ...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More