Method for reducing critical size of copper interconnection groove

A trench and interconnect trench technology, applied in electrical components, semiconductor/solid-state device manufacturing, circuits, etc., can solve the problems of poor resolution, large window pattern, and high cost

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0034] The specific embodiment of the present invention will be further described below in conjunction with accompanying drawing:

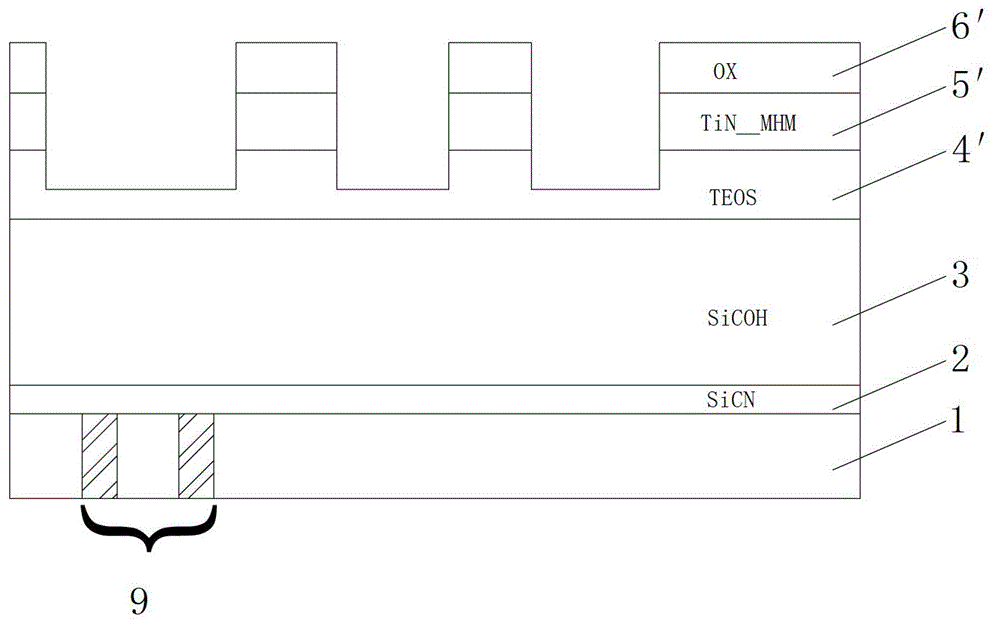

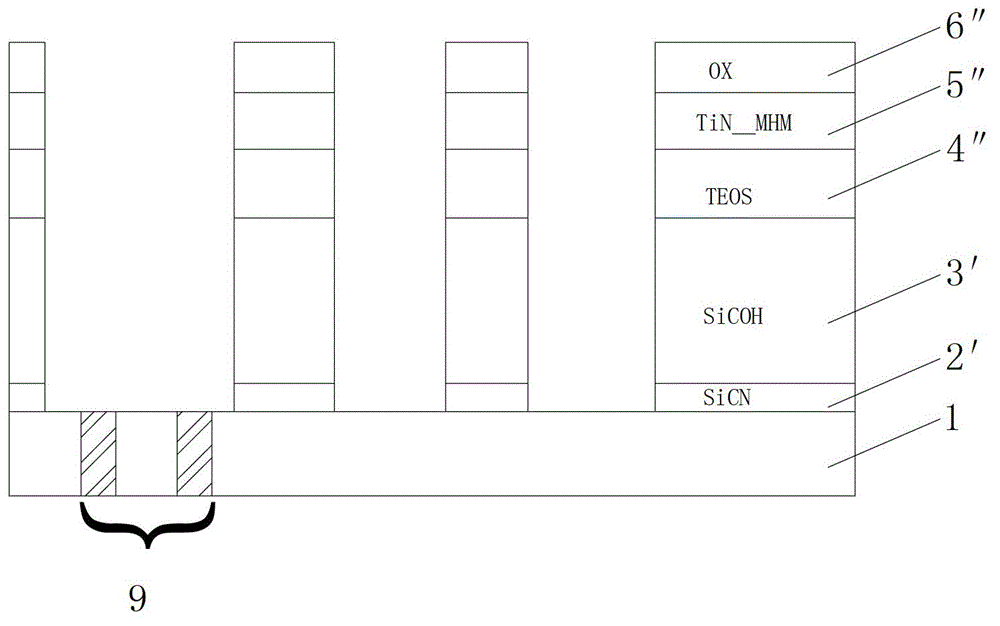

[0035] An embodiment of the present invention is provided below for further elaboration, Figure 7-12 A flow chart of a preparation method for reducing the critical dimension of copper interconnect trench etching provided by the present invention, specifically comprising the following steps:

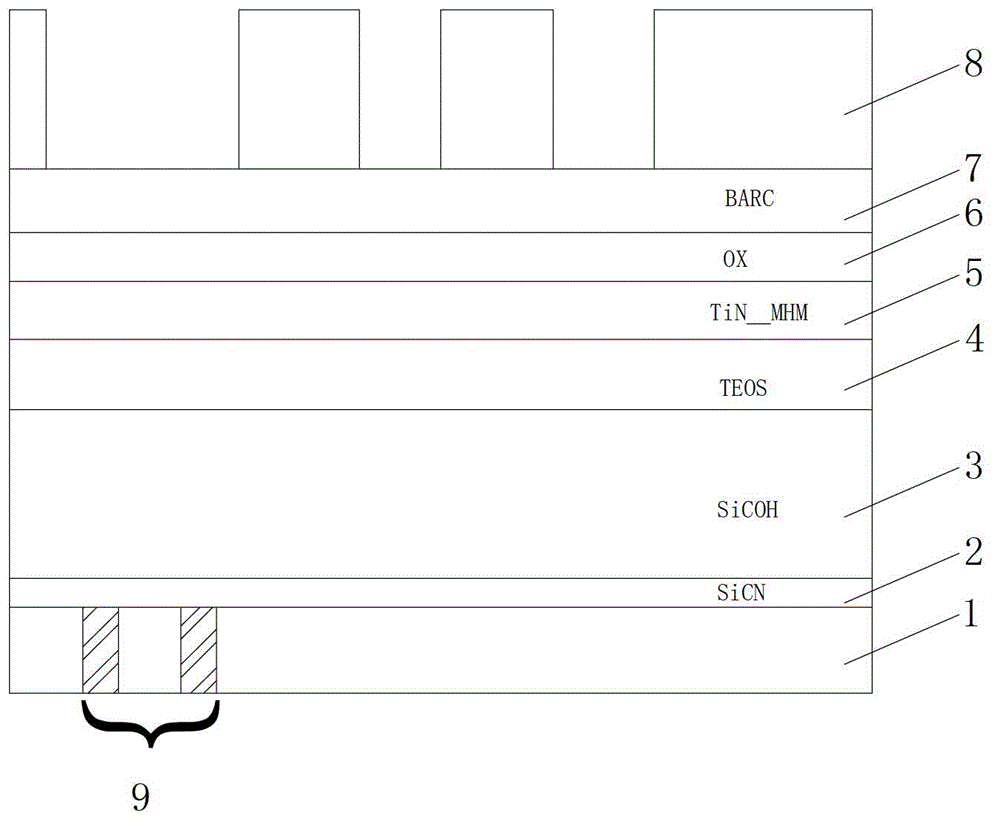

[0036]Step S1, providing a semiconductor structure, the semiconductor structure includes a substrate 1, and the substrate 1 is sequentially formed with a dielectric layer, a metal hard mask 5 (TiN_MHM) and an oxide layer 6 (OX) from bottom to top, wherein the dielectric The layers include the first dielectric layer 2 (SiCN), the second dielectric layer 3 (SiCOH), and the third dielectric layer 4 (TEOS) from bottom to top; there is a metal via area 9 in the substrate 1, and the metal via area 9 Partially filled with tungsten. In the trench etching process o...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More