Trench type field effect transistor structure and preparation method thereof

A field-effect transistor, trench-type technology, used in transistors, semiconductor/solid-state device manufacturing, semiconductor devices, etc., can solve the problems of poor electrical connection in the body region, low EAS capability, etc., to improve EAS capability, The effect of improving doping uniformity and increasing cell density

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

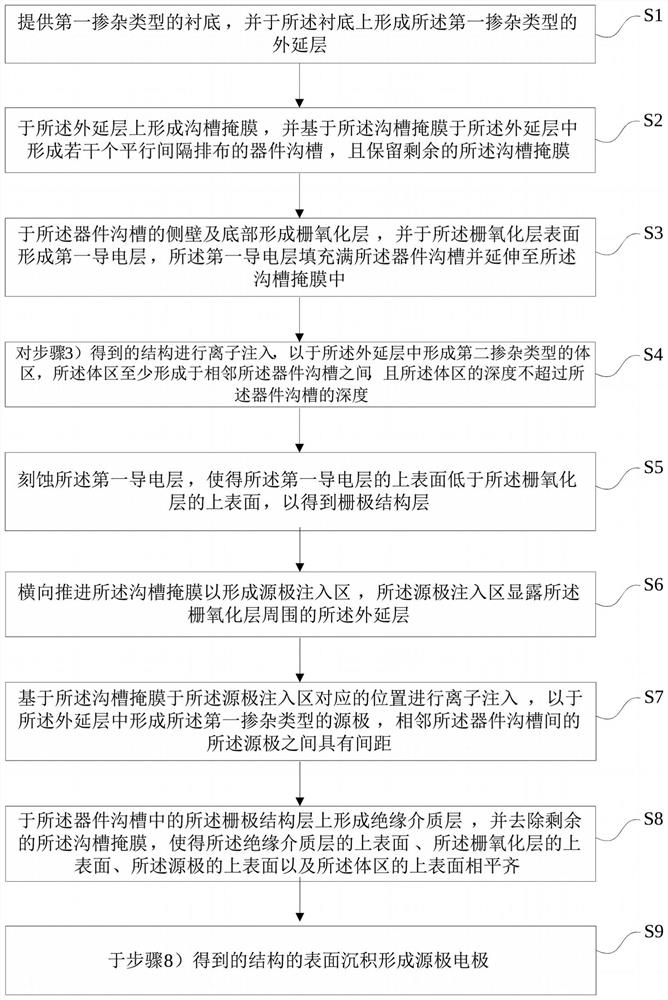

[0081] Such as Figure 1-14 As shown, the present invention provides a method for preparing a trench field effect transistor structure, the preparation method of the trench field effect structure at least includes the following steps:

[0082] 1) providing a substrate of a first doping type, and forming an epitaxial layer of the first doping type on the substrate;

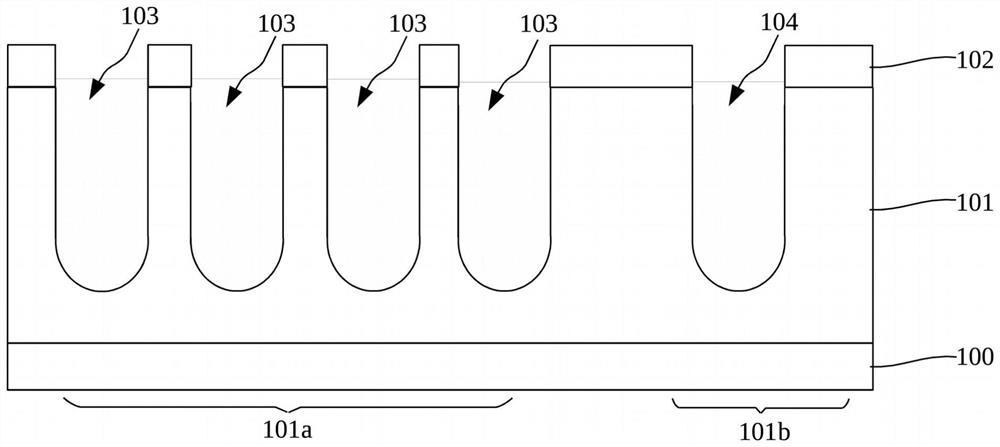

[0083] 2) Forming a trench mask on the epitaxial layer, and forming a plurality of device trenches arranged in parallel at intervals in the epitaxial layer based on the trench mask, and retaining the rest of the trench mask ;

[0084] 3) forming a gate oxide layer on the sidewall and bottom of the device trench, and forming a first conductive layer on the surface of the gate oxide layer, the first conductive layer fills the device trench and extends to the In the trench mask;

[0085] 4) performing ion implantation on the structure obtained in step 3), so as to form a body region of the second doping type in the...

Embodiment 2

[0129] Such as Figure 14 shown, see Figure 1-13 , the present invention also provides a trench type field effect transistor structure, the trench type field effect structure at least includes:

[0130] a substrate 100 of a first doping type;

[0131] The epitaxial layer 102 of the first doping type, the epitaxial layer 102 is formed on the substrate 100;

[0132] a plurality of device trenches 103 arranged in parallel at intervals, the device trenches 103 are formed in the epitaxial layer 102;

[0133] a gate oxide layer 106 formed on the sidewall and bottom of the device trench 103;

[0134] a gate structure layer 111 formed on the surface of the gate oxide layer 106, and the upper surface of the gate structure layer 111 is lower than the upper surface of the gate oxide layer 106;

[0135] A body region 110 of a second doping type, the body region 110 is formed between adjacent device trenches 103 and the depth of the body region 110 does not exceed the depth of the dev...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More