Method for forming micro-graphic pattern on floating grid

A micro-pattern, floating gate technology, applied in electrical components, semiconductor/solid-state device manufacturing, circuits, etc., can solve problems such as high cost, inability to meet the requirements of critical dimensions for detection, and small process tolerance, achieving easy implementation, good The effect of pattern reproducibility and process cycle saving

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment

[0039] Take the case of forming a floating gate structure of NAND flash memory with 0.22 μm line and 80 nm interval as an example.

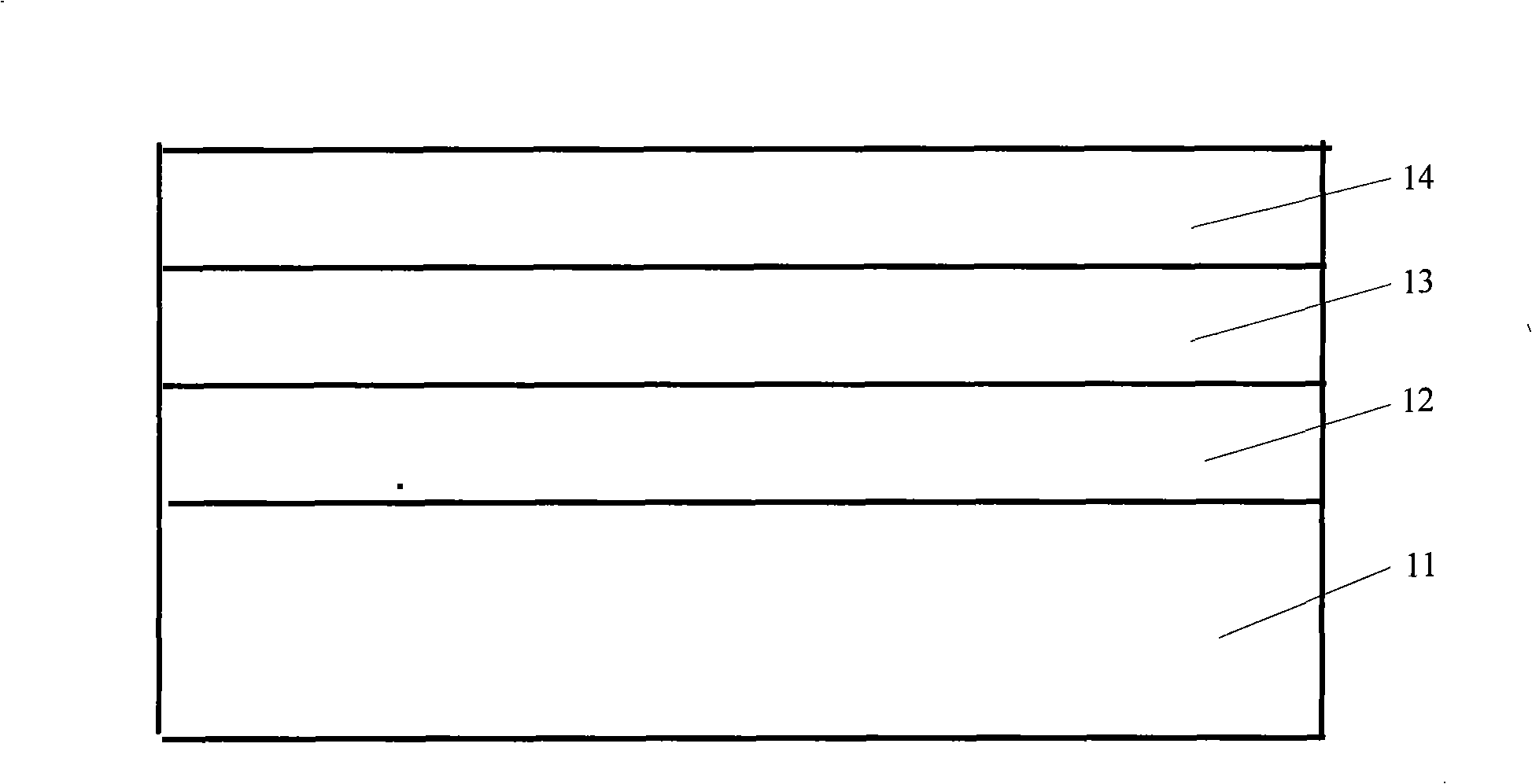

[0040] A polysilicon layer 22 is sequentially formed on a silicon substrate 21 with a thickness of 7500 The photoresist layer 23, such as Figure 2A shown;

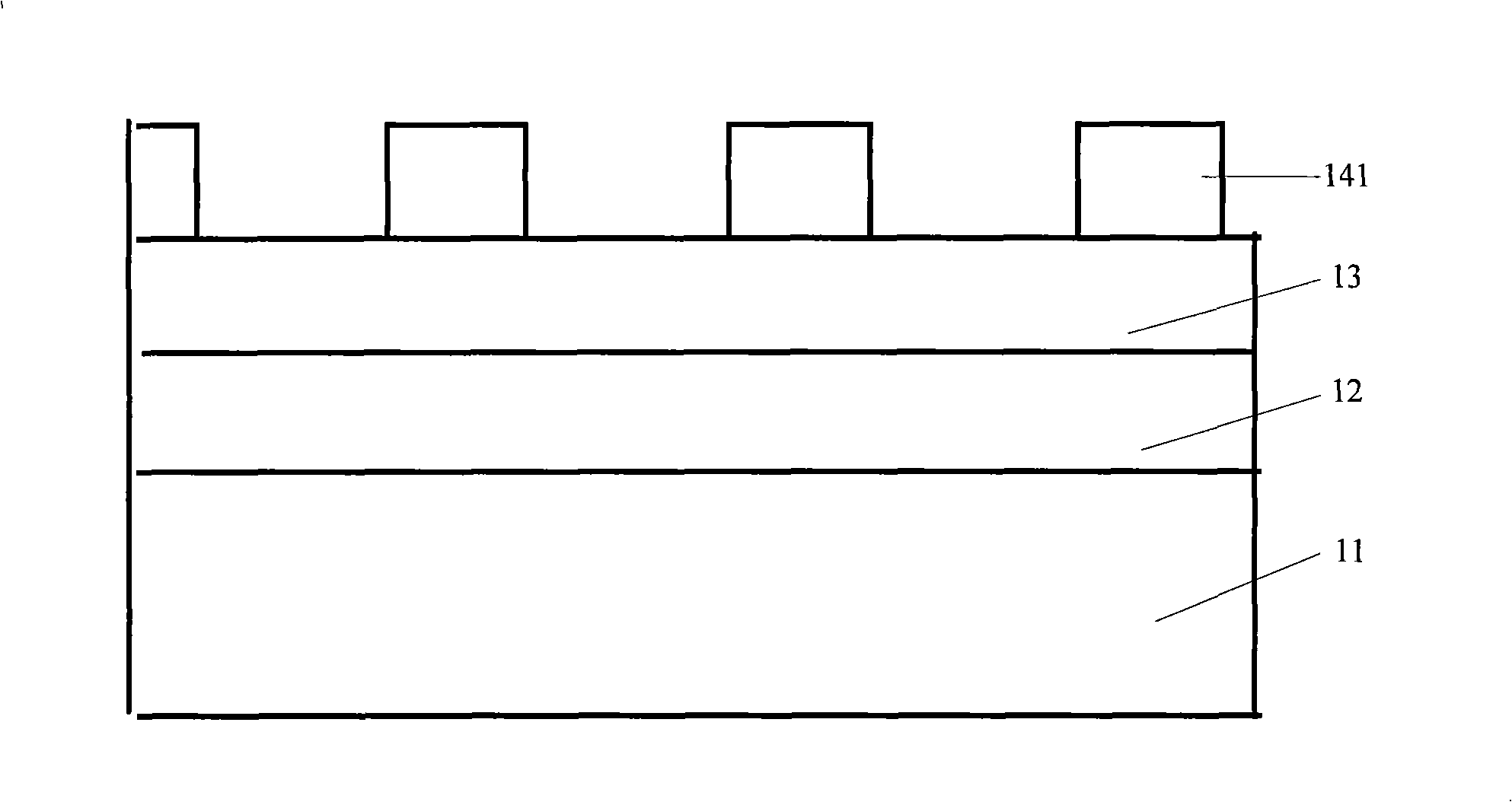

[0041] Use a KrF (ASML PAS / 850C) scanner to expose and develop the photoresist layer 23 to form a pattern 231 with a line width of 0.14 μm and a space of 0.16 μm, as Figure 2B shown;

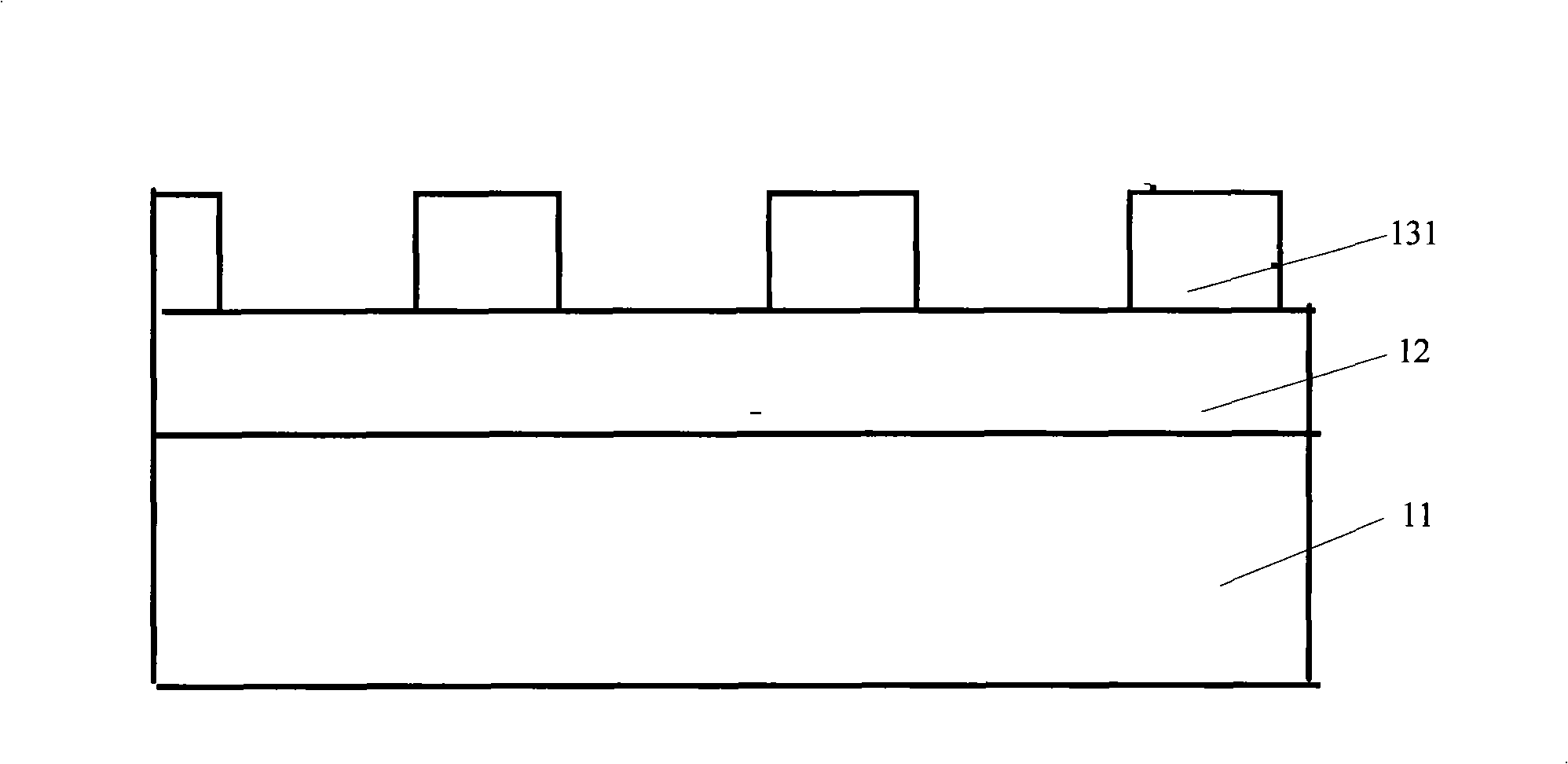

[0042] The formed photoresist pattern is generally baked at a temperature between 80° C. and the glass transition temperature (Tg) of the photoresist for 80 to 200 seconds, and the baking is performed on a heating plate.

[0043] After the above process, due to the addition of a baking step after development, that is, a thermal reflow step, this step causes the photoresist to reflow, thereby making the line width of the pattern larger and rounder, and as a result, the developed size of the space will be r...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More