Patents

Literature

249results about How to "Improve compilation efficiency" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Method and device for pre-encrypting program

ActiveCN106775893AImprove compilation efficiencyImprove startup speedProgram loading/initiatingComputer scienceIntelligent equipment

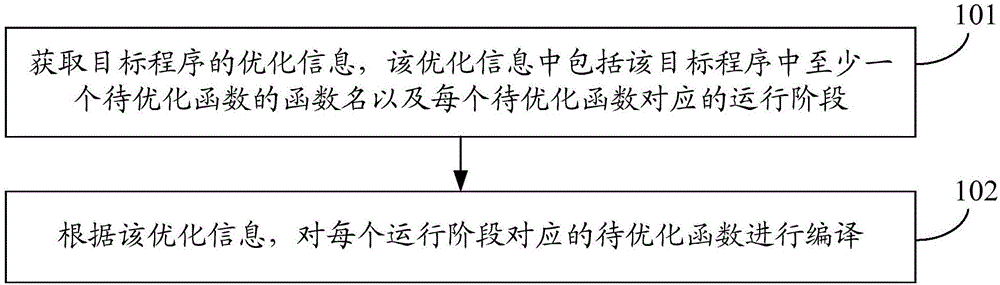

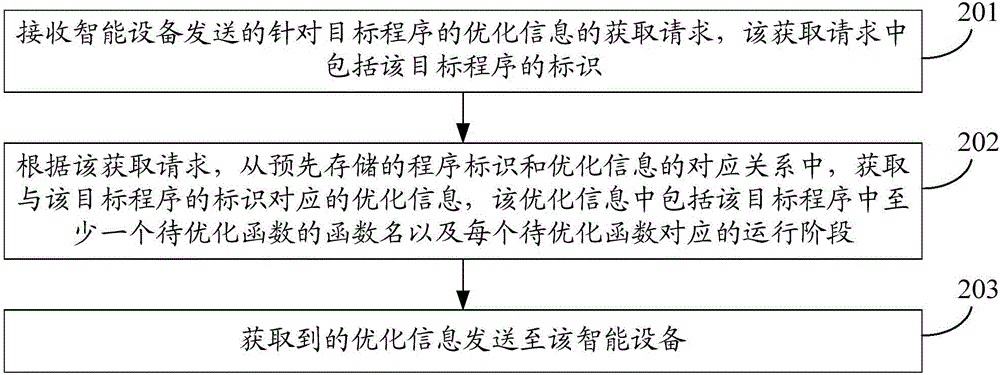

The invention relates to a method and device for pre-encrypting a program, and belongs to the field of electronic technology application. The method comprises the steps of obtaining optimization information of a target program, wherein the optimization information comprises the function name of at least one function to be optimized and a running stage corresponding to each function to be optimized in the target program; according to the optimization information, encrypting the function to be optimized corresponding to each running stage. Because in the process that intelligent equipment conducts pre-encryption on the target program, the function recorded in the optimization information can be encrypted only, all functions in the target function does not need to be encrypted an more, thus the encryption efficiency of the target program is effectively improved, and speeds for starting and running a system are increased.

Owner:BEIJING XIAOMI MOBILE SOFTWARE CO LTD

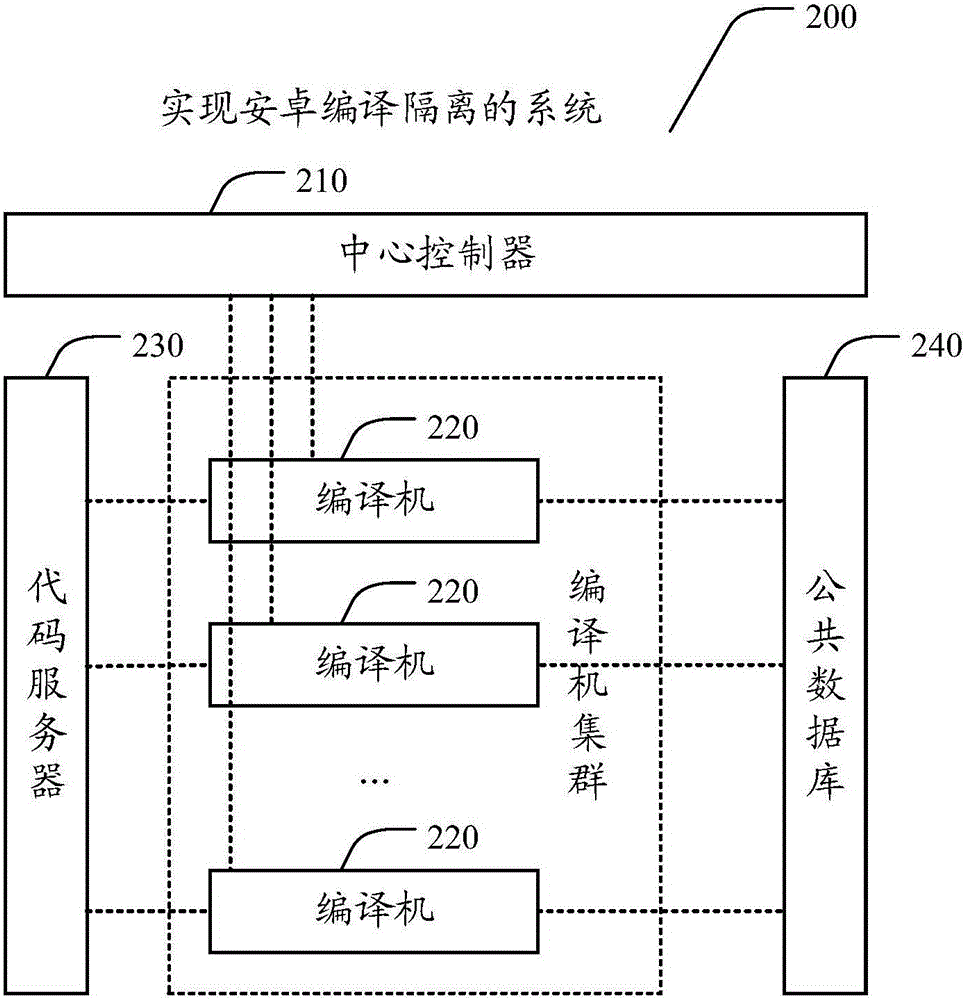

Method and system for realizing Android compiling isolation

InactiveCN106095523AQuality improvementIndependent configurationProgram controlMemory systemsOperating system

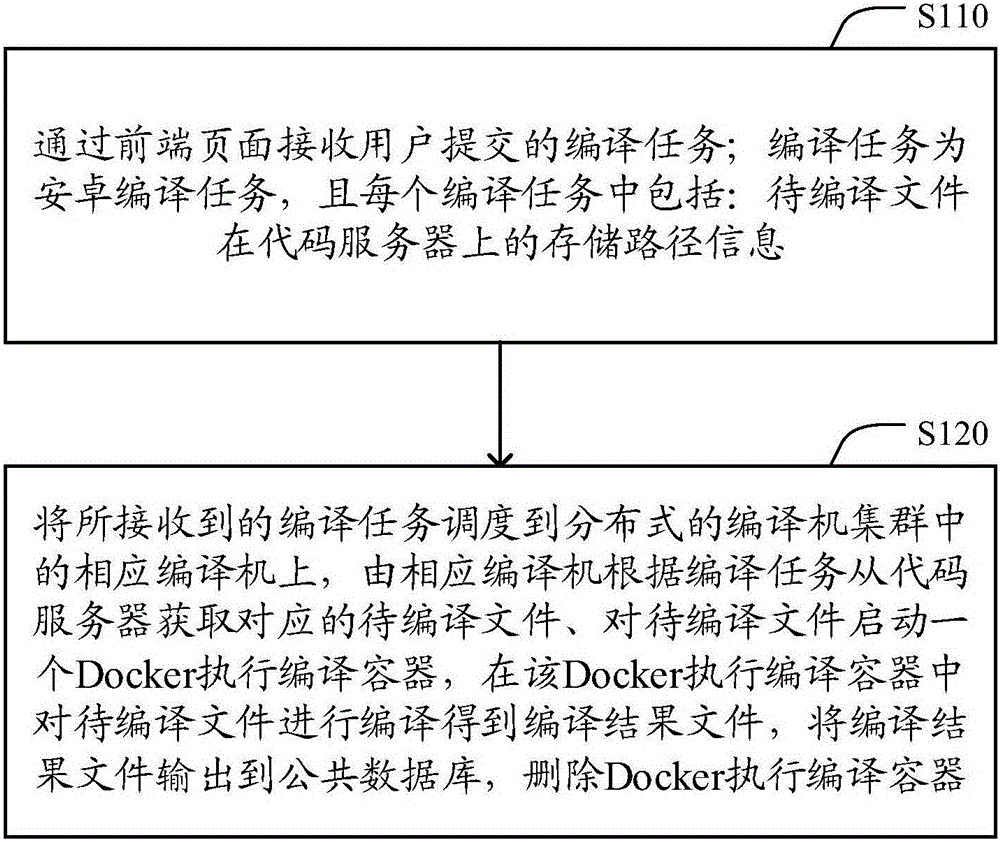

The invention discloses a method and a system for realizing Android compiling isolation. The method comprises the following steps: through a front-end page, receiving compiling tasks submitted by a user, wherein the compiling tasks are Android compiling tasks, and each compiling task comprises the storage path information of a file to be compiled on a code server; and scheduling the received compiling task onto a corresponding compiling machine in a distributed compiling machine cluster, obtaining the corresponding file to be compiled from the code server by the corresponding compiling machine according to the compiling task, starting a Docker execution compiling container for the file to be compiled, compiling the file to be compiled in the Docker execution compiling container to obtain a compiling result file, outputting the compiling result file to a common database, and deleting the Docker execution compiling container. Since the Docker execution compiling container is adopted, compiling environment can be quickly and independently configured, and meanwhile, the method occupies few resources and is high in compiling efficiency.

Owner:BEIJING QIHOO TECH CO LTD +1

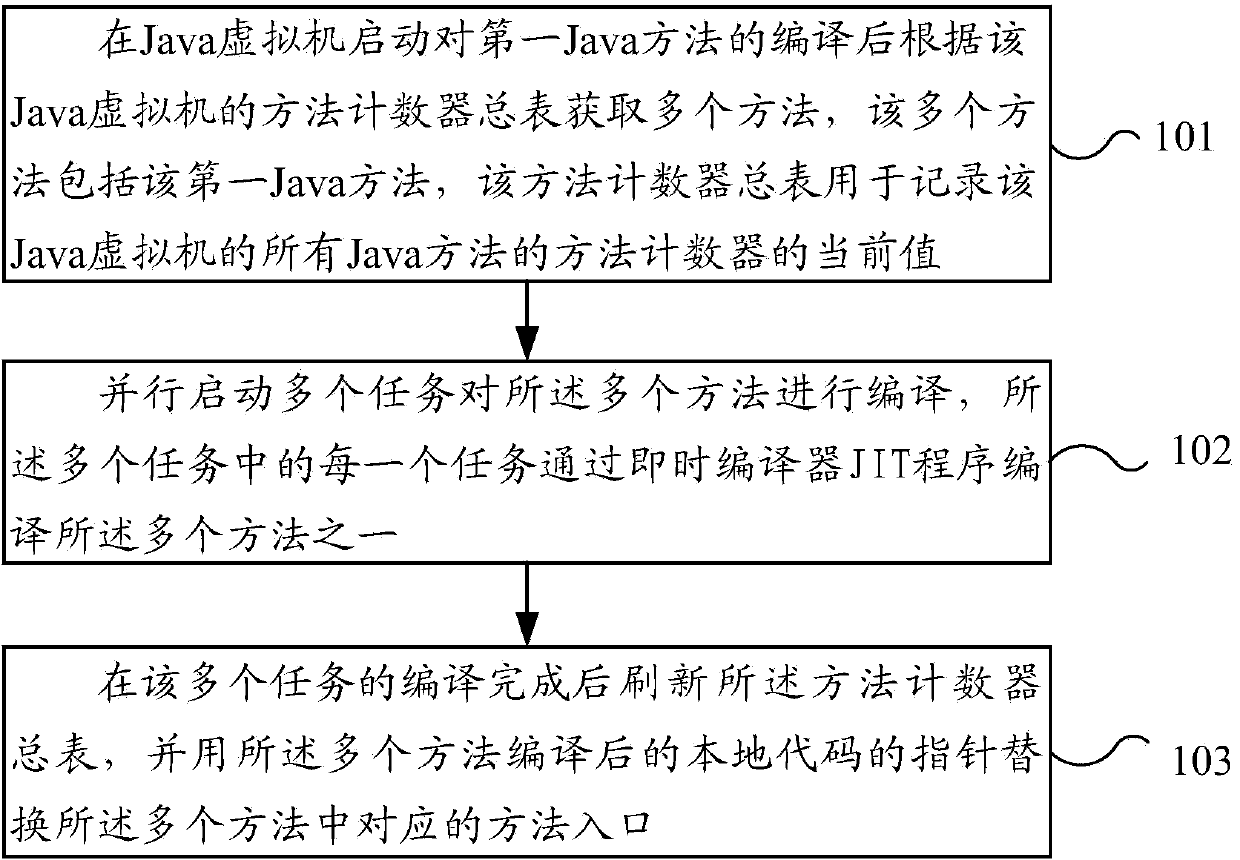

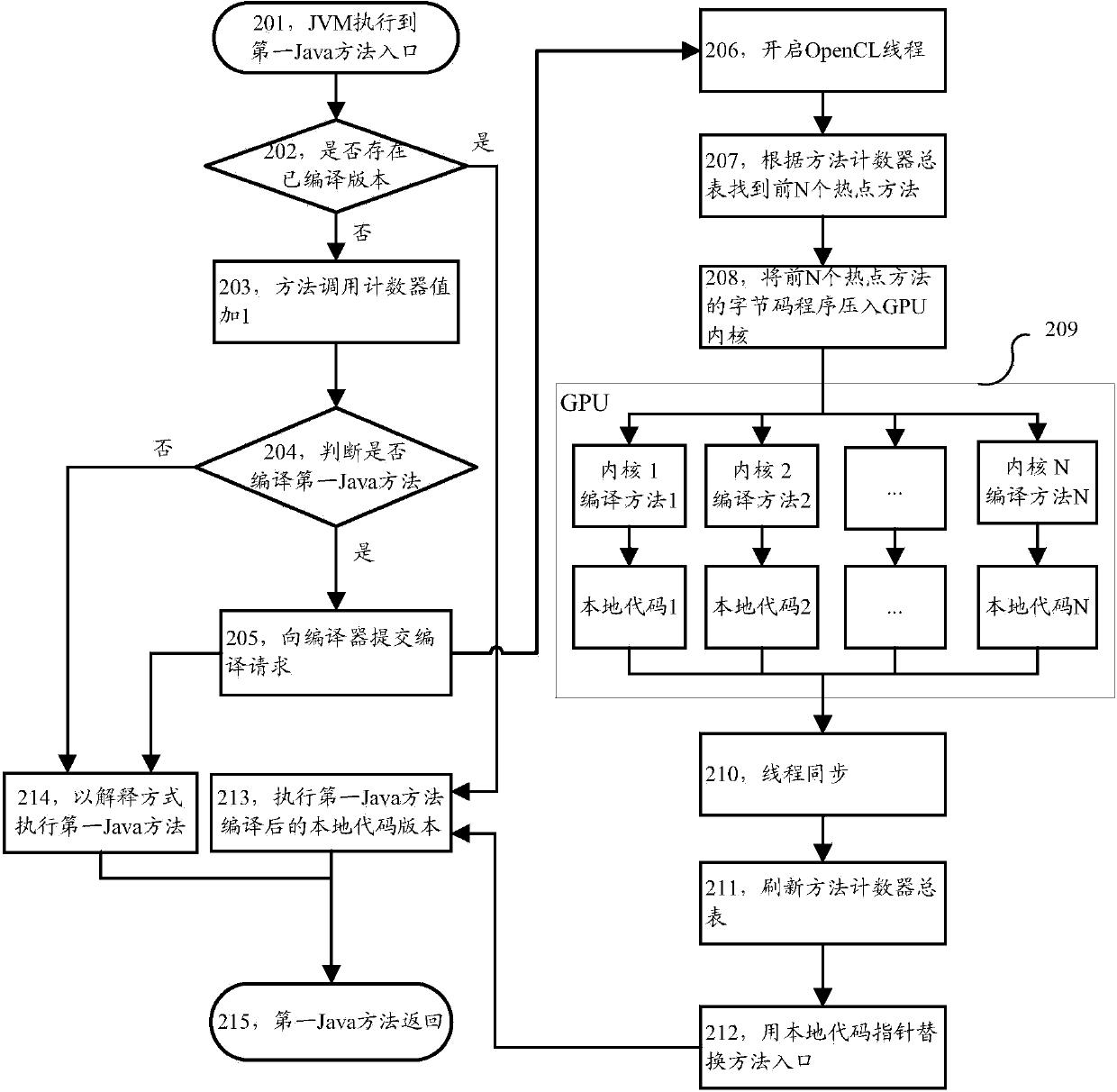

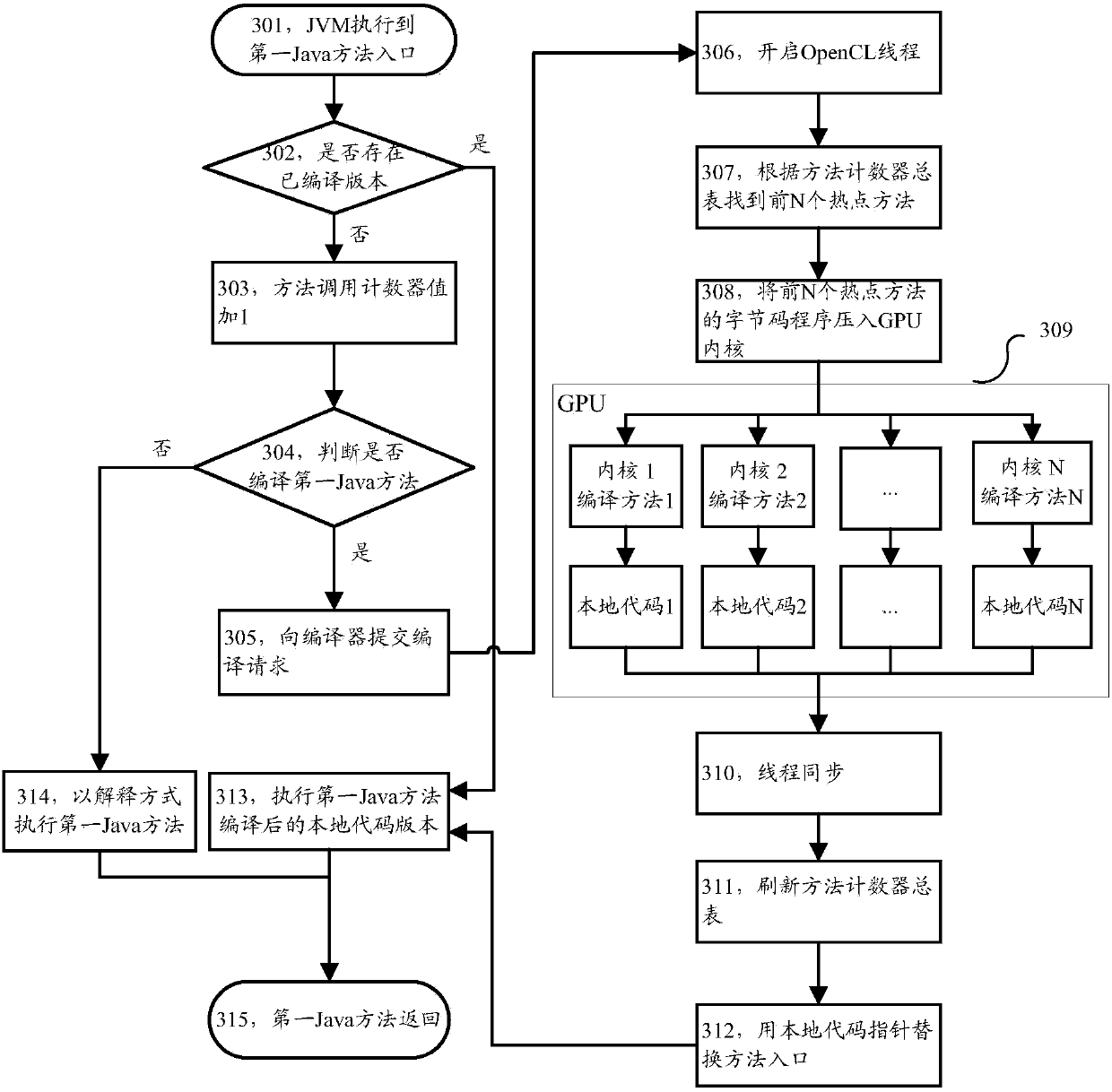

Java virtual machine (JVM) and compiling method thereof

InactiveCN103729235AImprove compilation efficiencyImprove performanceSoftware simulation/interpretation/emulationMemory systemsSoftware engineeringJava virtual machine

An embodiment of the invention provides a Java virtual machine (JVM) and a compiling method thereof. The method includes: after initiating compiling of a first Java method on the Java virtual machine, acquiring multiple methods according to a method counter general table of the Java virtual machine, wherein the multiple methods include the first Java method, and the method counter general table is used for recording current values of method counters of all the Java methods of the Java virtual machine; initiating multiple tasks in parallel to compile the methods, wherein each task in the tasks compiles one of the methods through a JIT (just in time) compiler; after compiling of the methods is completed, refreshing the method counter general table, and replacing method entries, corresponding to the methods, with pointers of local codes of the compiled methods. By the JVM and the compiling method thereof, compiling efficiency of the JVM can be improved at low cost, and performance of the JVM is optimized.

Owner:HUAWEI TECH CO LTD

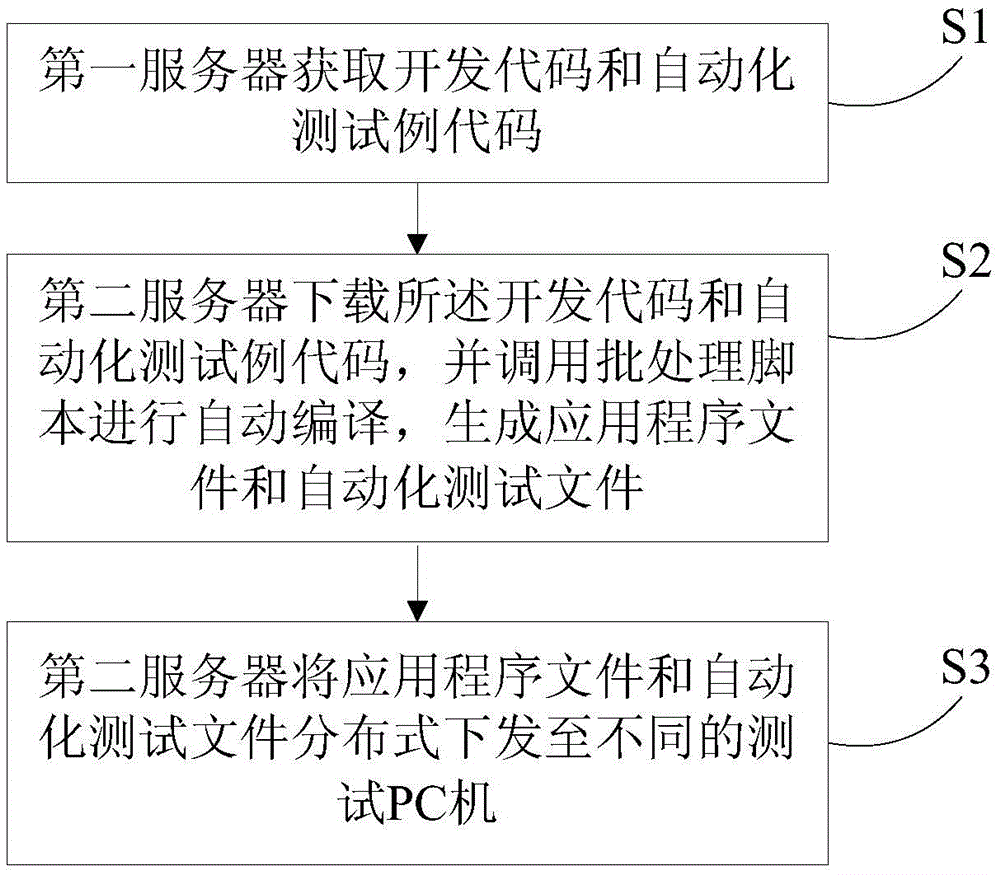

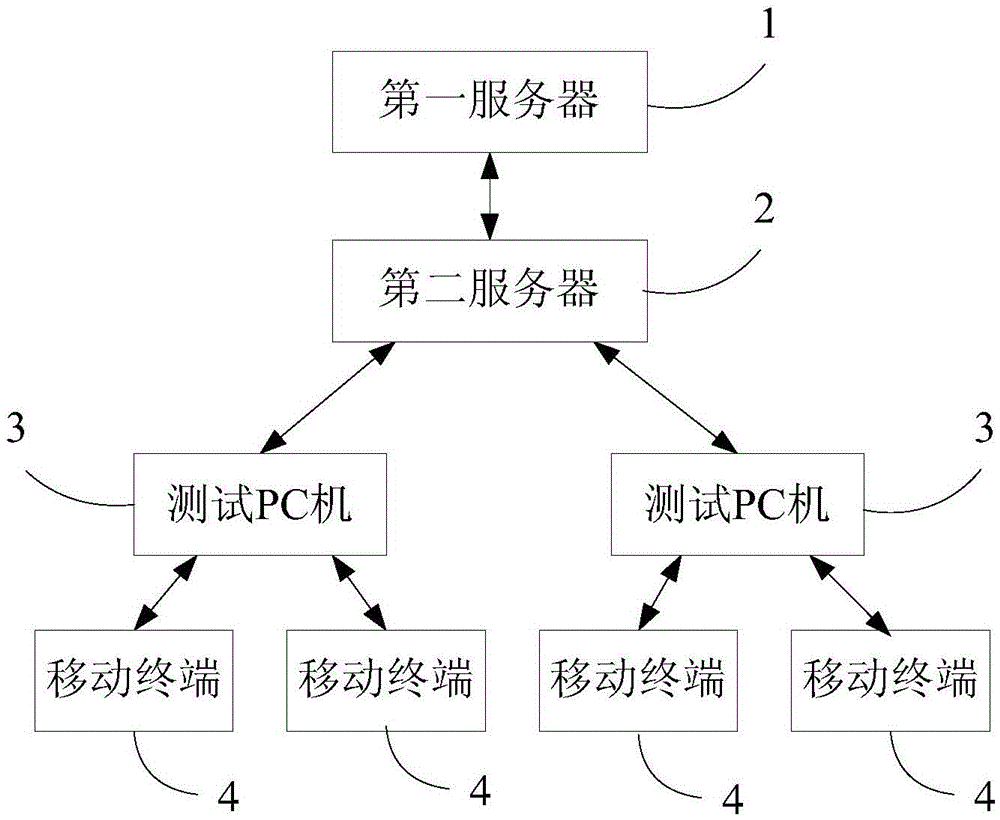

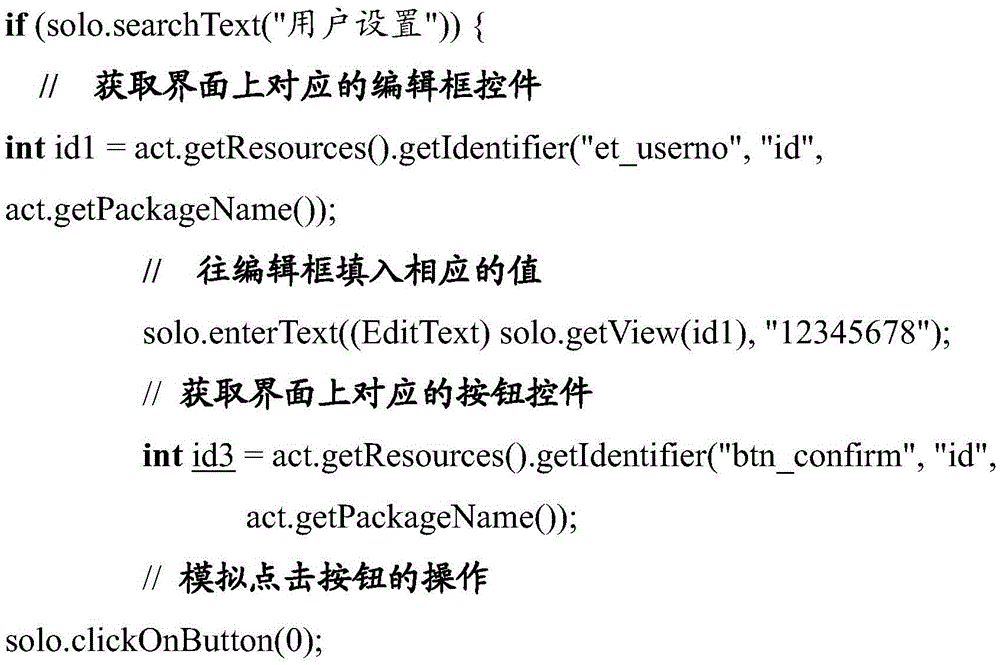

Distributed automatic construction method and system

InactiveCN105550001ASave storage spaceImplement asynchronous testingSoftware testing/debuggingProgram loading/initiatingBatch processingAutomatic testing

The invention discloses a distributed automatic construction method and system. The method comprises the following steps: obtaining a development code and an automatic test case code by a first server; downloading the development code and the automatic test case code by a second server, and calling a batch processing script to carry out automatic compiling so as to generate an application program file and an automatic test file; and distributing the application program file and the automatic test file to different test PC machines by the second server in a distributed manner. According to the distributed automatic construction method and system, the development period of a plurality of application programs can be greatly shortened and favorable software quality can be ensured.

Owner:XIAMEN MEIYA PICO INFORMATION

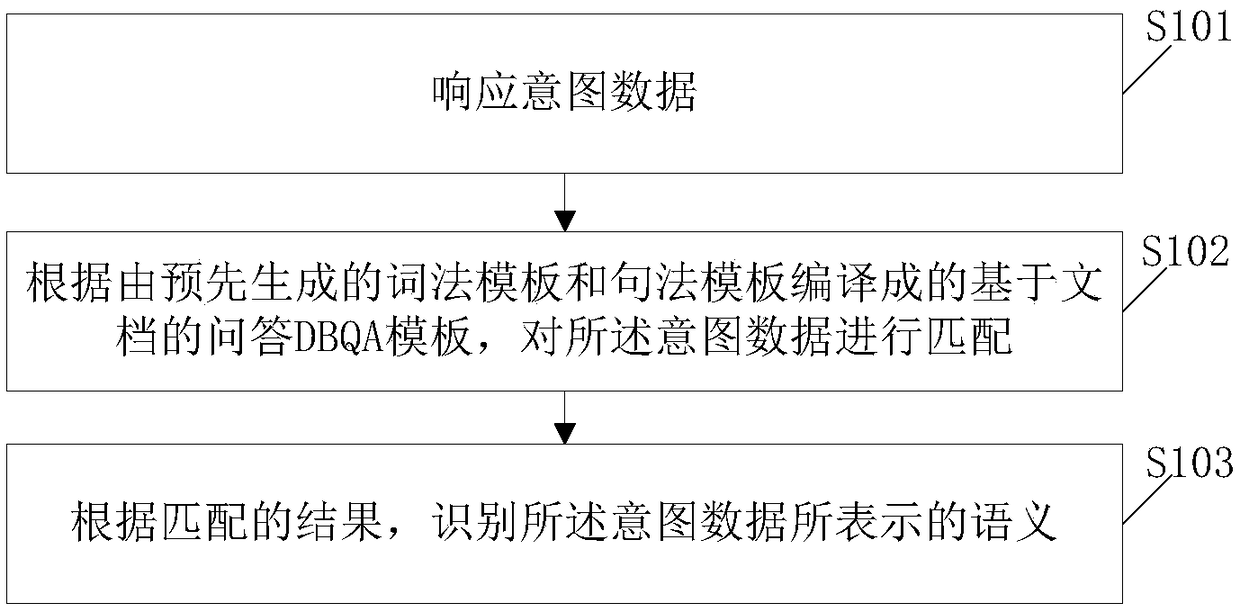

Intent identification method, intent identification device, intent identification equipment and storage medium

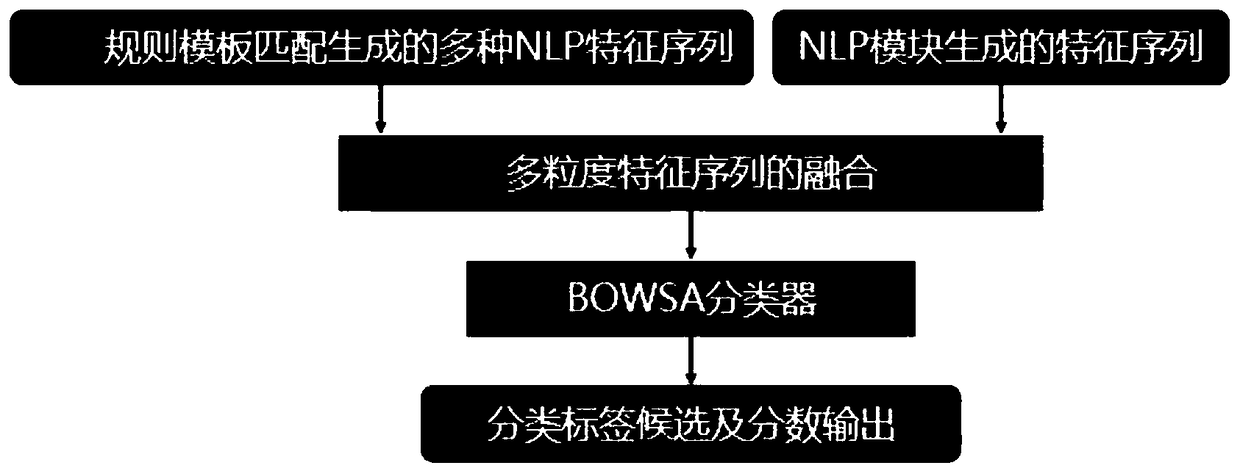

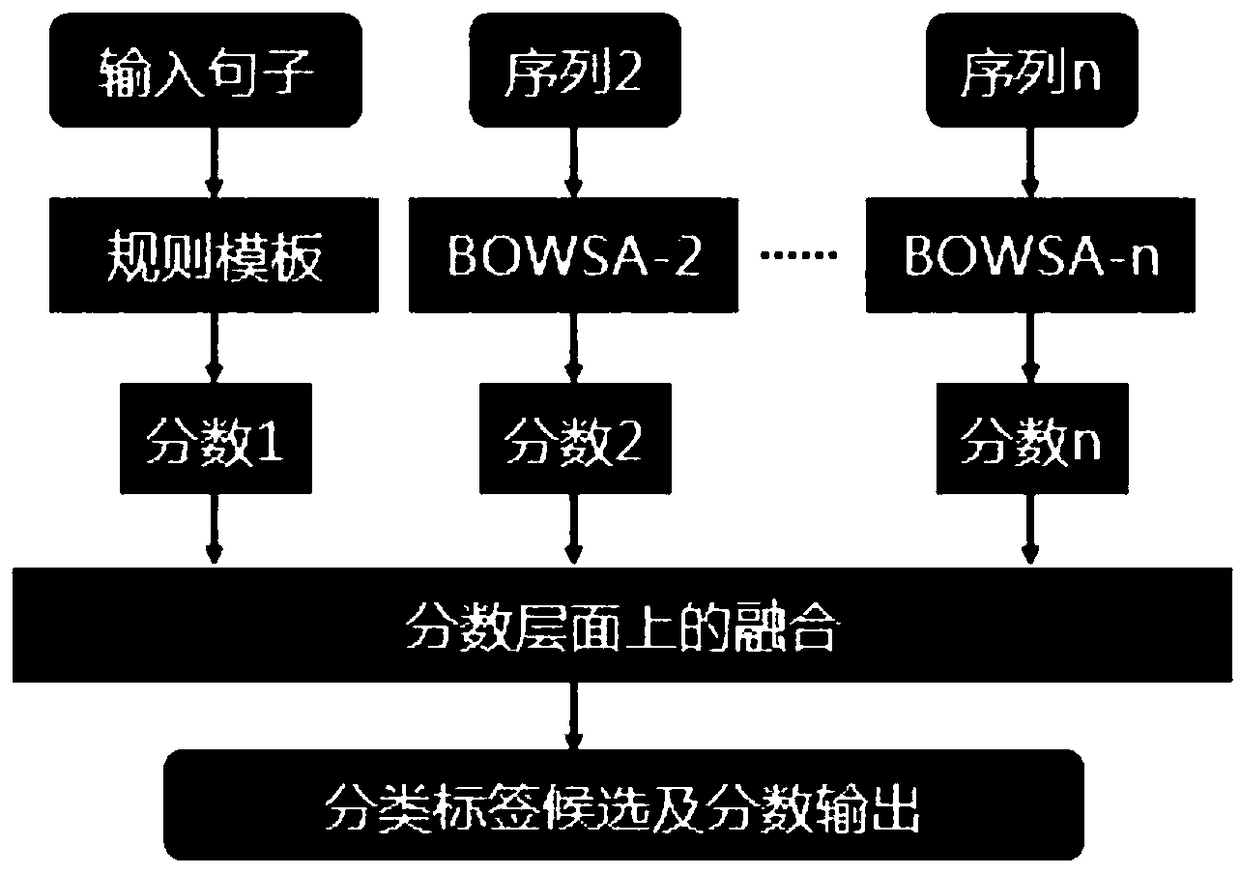

ActiveCN108874917AAchieve decouplingReduce implementation complexitySemantic analysisSpecial data processing applicationsSemanticsIdentification device

The invention discloses an intent identification method, an intent identification device, intent identification equipment and a storage medium. The intent identification method includes: responding tointent data; carrying out matching on the intent data according to document-based question answering (DBQA) templates compiled by pre-generated morphology templates and syntax templates; and identifying, according to a result of matching, semantics represented by the intent data. The method effectively improves an accuracy rate of user intent identification, effectively reduces realization complexity of the DBQA templates, and effectively improves compilation efficiency.

Owner:BEIJING 58 INFORMATION TTECH CO LTD

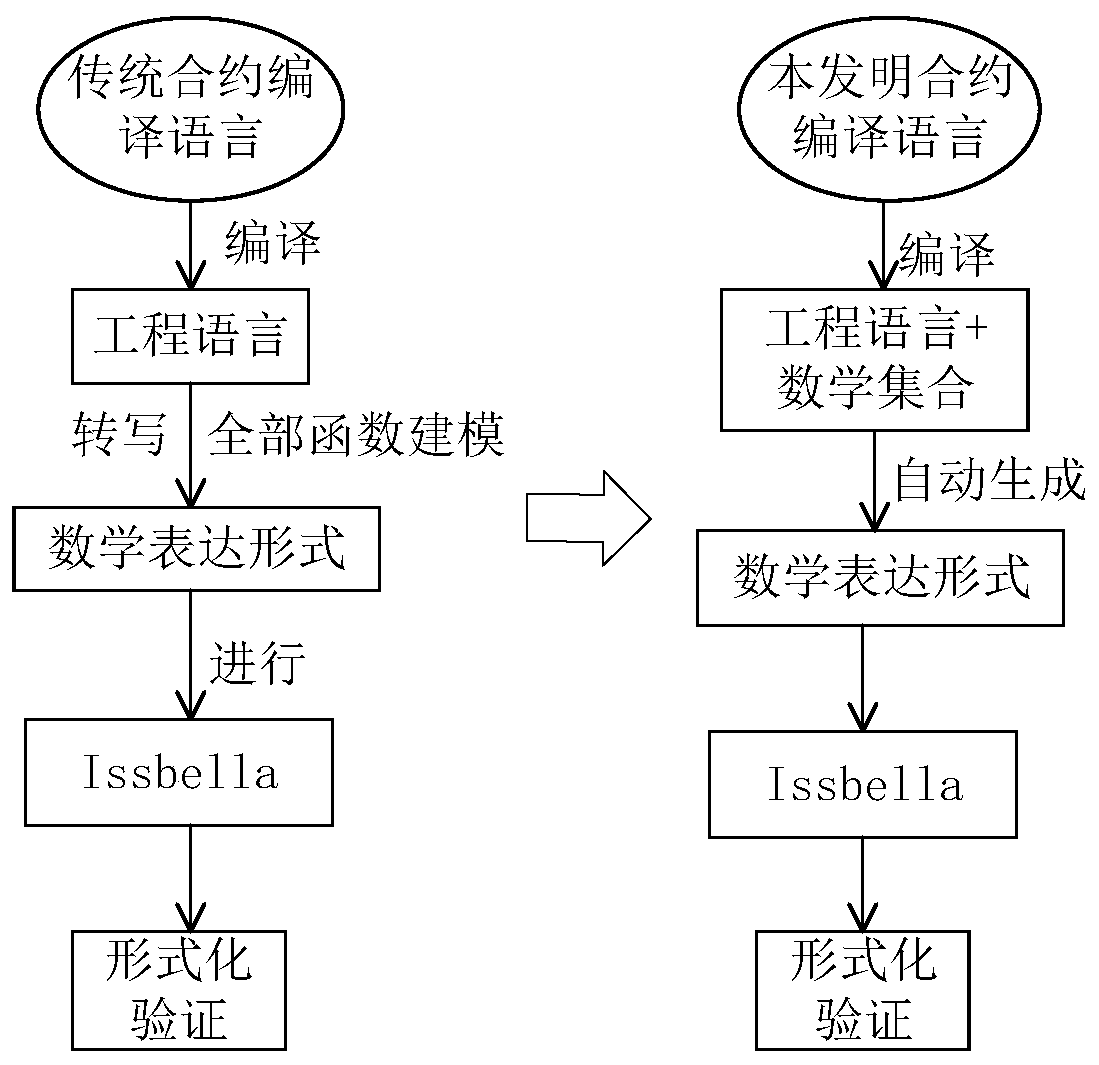

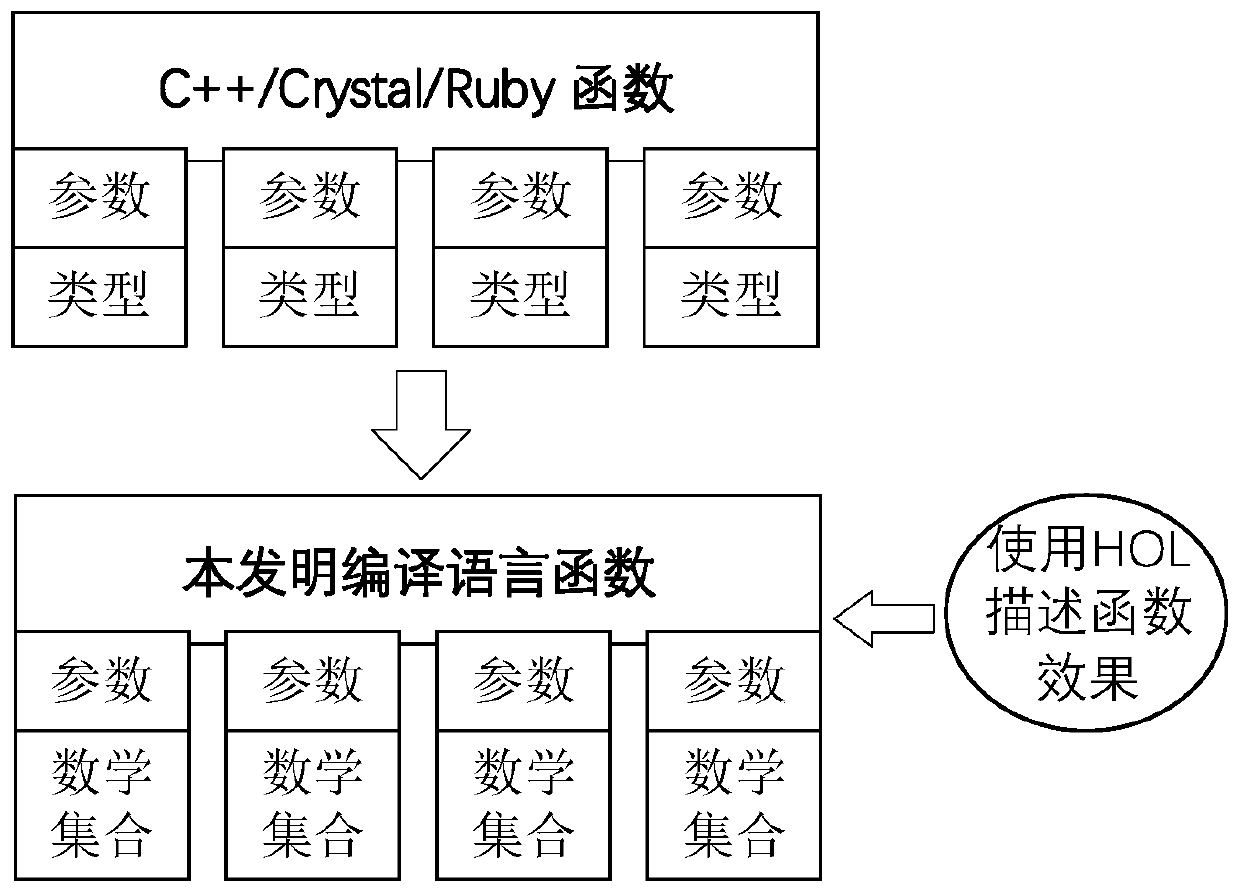

Intelligent contract compiling method suitable for formal verification

ActiveCN109753288AImprove compilation efficiencyEasy to operateCode compilationCreation/generation of source codeFormal proofSmart contract

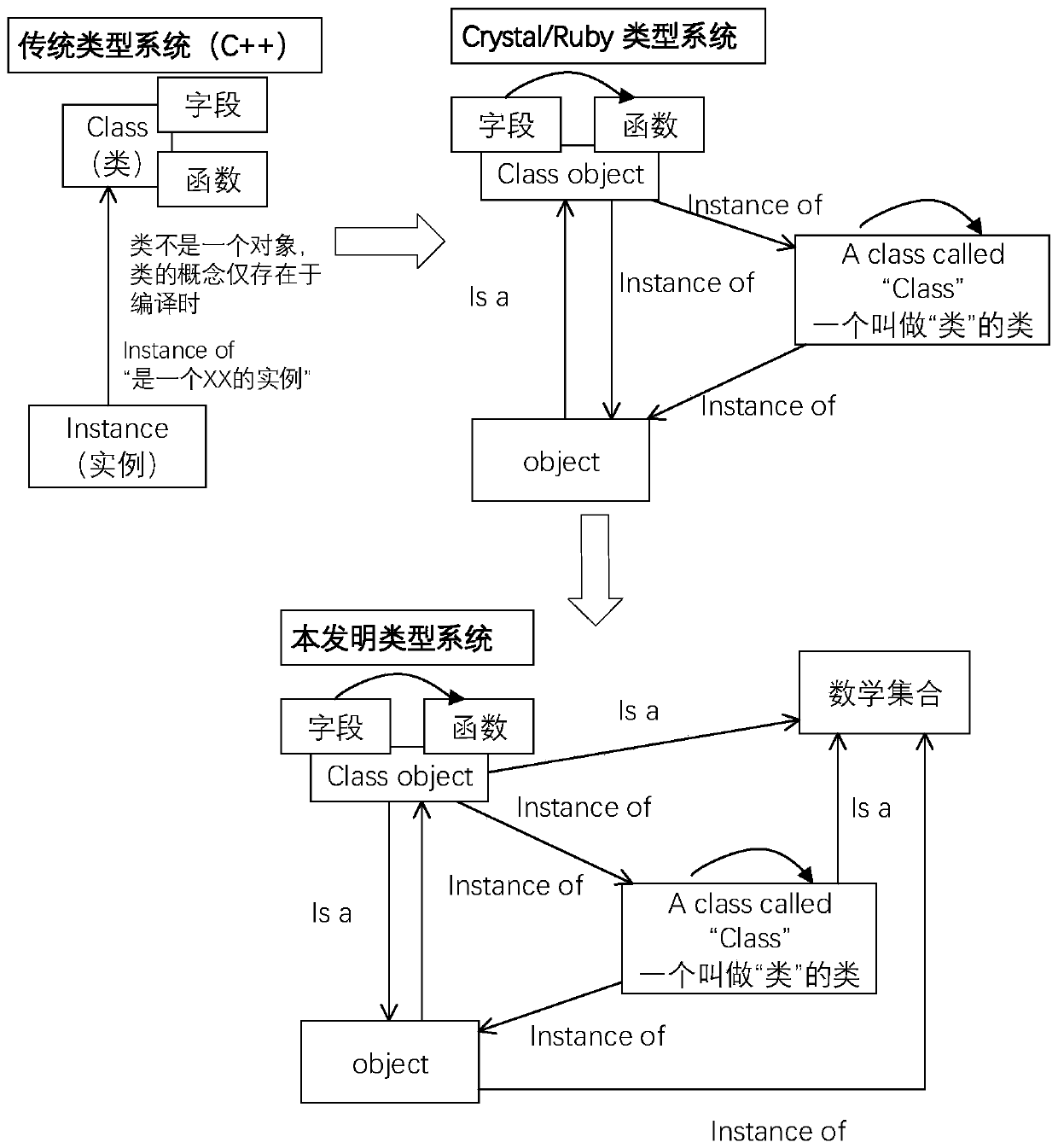

The invention discloses an intelligent contract compiling method suitable for formal verification. The novel intelligent contract compilation language comprises an engineering application and type mathematical set, all Bugs can be found before operation by utilizing formal proof in combination with language editing, it can be guaranteed that a written program can edit a language which is safe, free of vulnerability and simple to operate, and verification of an intelligent contract form test is carried out. When contract formal verification is carried out, only the used function theorem needs to be proved, function modeling is not needed, and the intelligent contract compiling efficiency is greatly improved.

Owner:HANGZHOU YUNXIANG NETWORK TECH

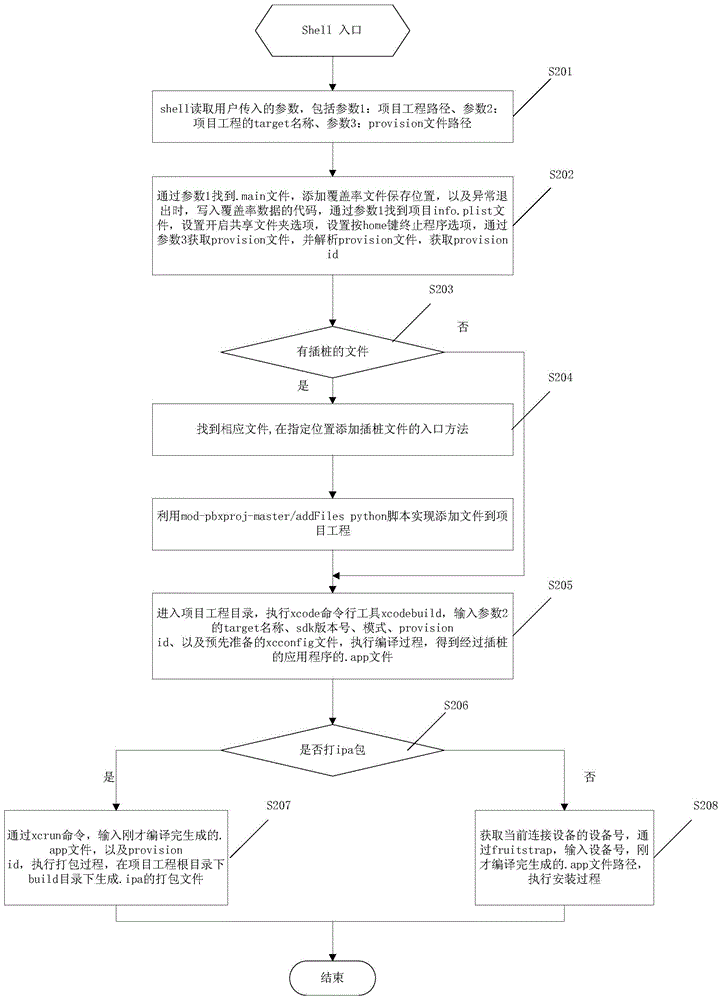

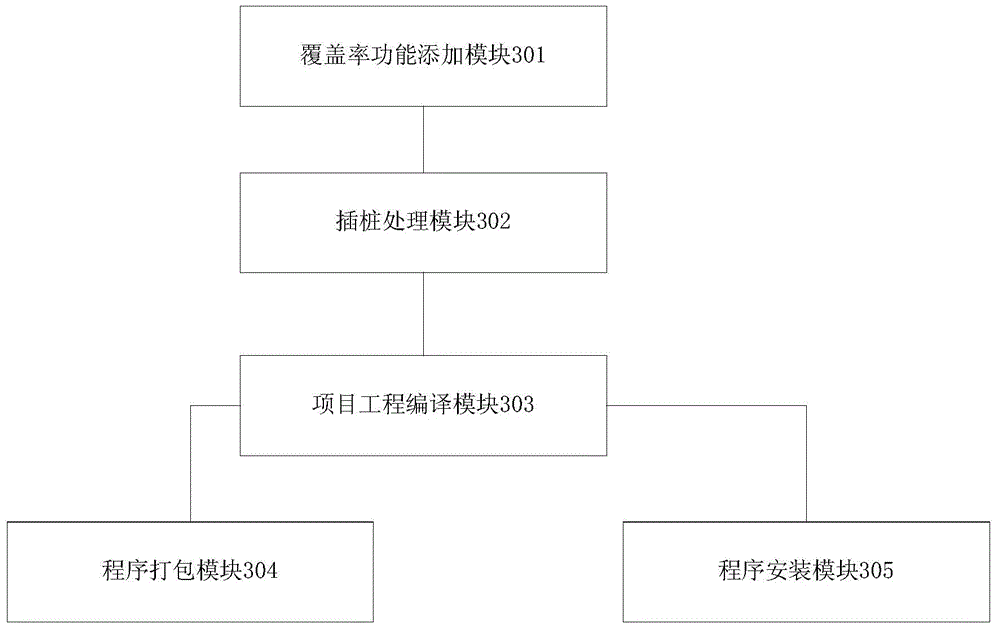

Automatic instrumentation, compiling and installing method and system

ActiveCN104598274AImprove compilation efficiencyRealize the function of inserting pilesProgram loading/initiatingProgramming languageCode coverage

The invention discloses an automatic instrumentation, compiling and installing method and a system. The method comprises the following steps of searching a main program file from appointed project engineering; adding a storage position of a coverage rate file which is used for storing a code coverage rate result to the main program file, and adding a code for writing coverage rate data into the coverage rate file at the storage position when the program abnormally exits; acquiring an equipment-associated file, and analyzing the equipment-associated file to obtain an equipment-associated file mark; obtaining a preset compiling configuration file for setting and starting a coverage rate statistical function; adding an instrumentation file to the project engineering, adding an instrumentation entry function which is used for calling the instrumentation file code to the code file, and compiling to obtain the instrumented application program; if a packaging option is needing to be packed, executing the packaging step, or else, executing the program installation step. According to the automatic instrumentation, compiling and installing method and system, the instrumentation and compiling of the project engineering are automatically executed; the instrumentation and compiling efficiency are improved.

Owner:BEIJING JINGDONG SHANGKE INFORMATION TECH CO LTD +1

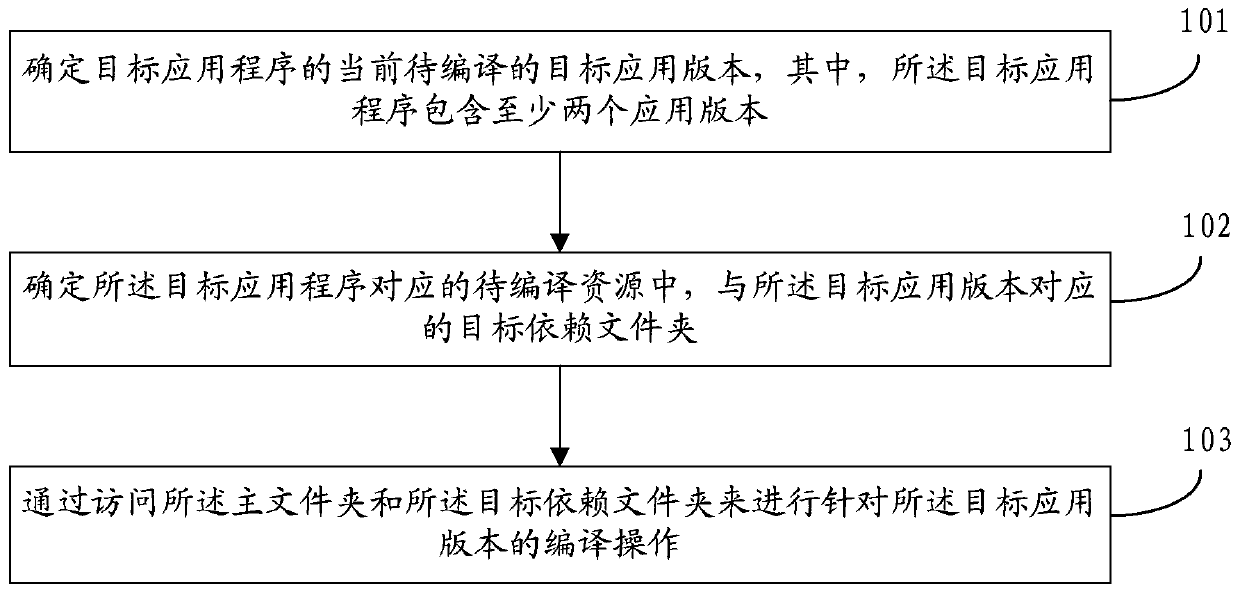

Application installation package compiling method and device, storage medium and terminal

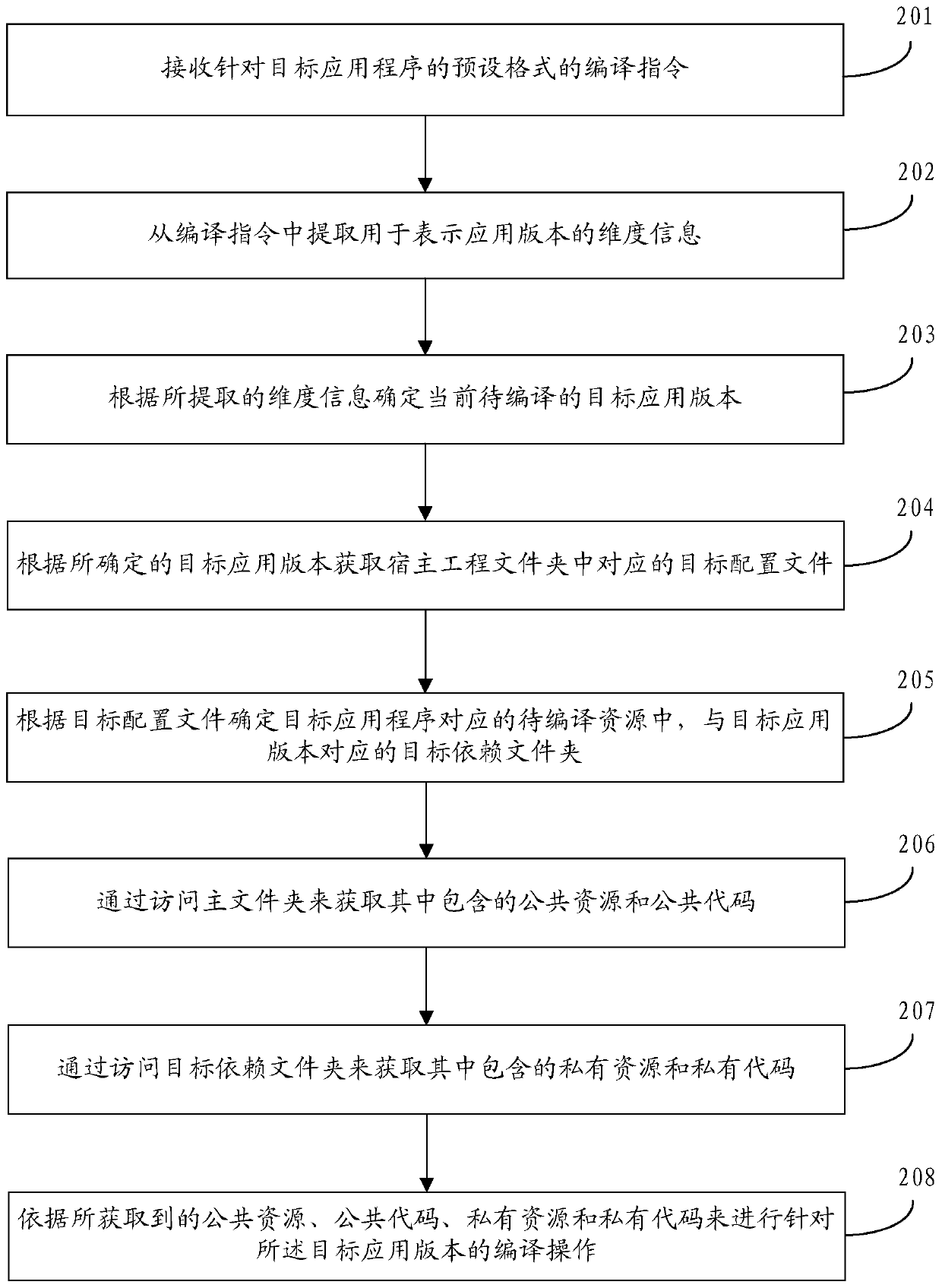

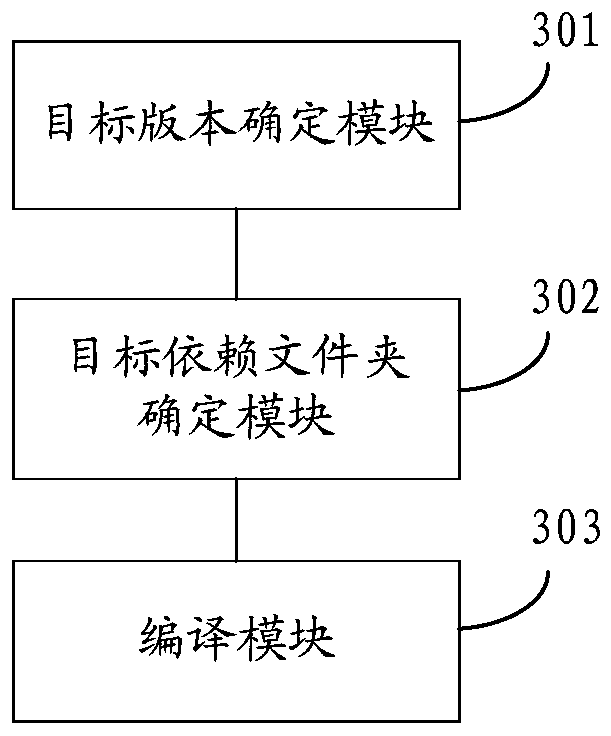

PendingCN109857405AImprove compilation efficiencyFacilitate parallel developmentCode compilationPublic resourceApplication software

The embodiment of the invention discloses an application program installation package compiling method and device, a storage medium and a terminal. The method comprises the following steps: determining a current to-be-compiled target application version of the target application program, determining target dependent folder corresponding to target application version in to-be-compiled resources corresponding to target application program; wherein the to-be-compiled resources comprise a main folder corresponding to the target application program and at least two dependent folders, the main folder comprises public resources and public codes corresponding to all application versions, and each dependent folder in the at least two dependent folders respectively corresponds to one application version and comprises private resources and private codes of the corresponding application version, and carrying out compiling operation aiming at the target application version by accessing the main folder and the target dependent folder. By adopting the technical scheme, the compiling efficiency of the application program installation package of the branch version can be improved.

Owner:GUANGDONG OPPO MOBILE TELECOMM CORP LTD

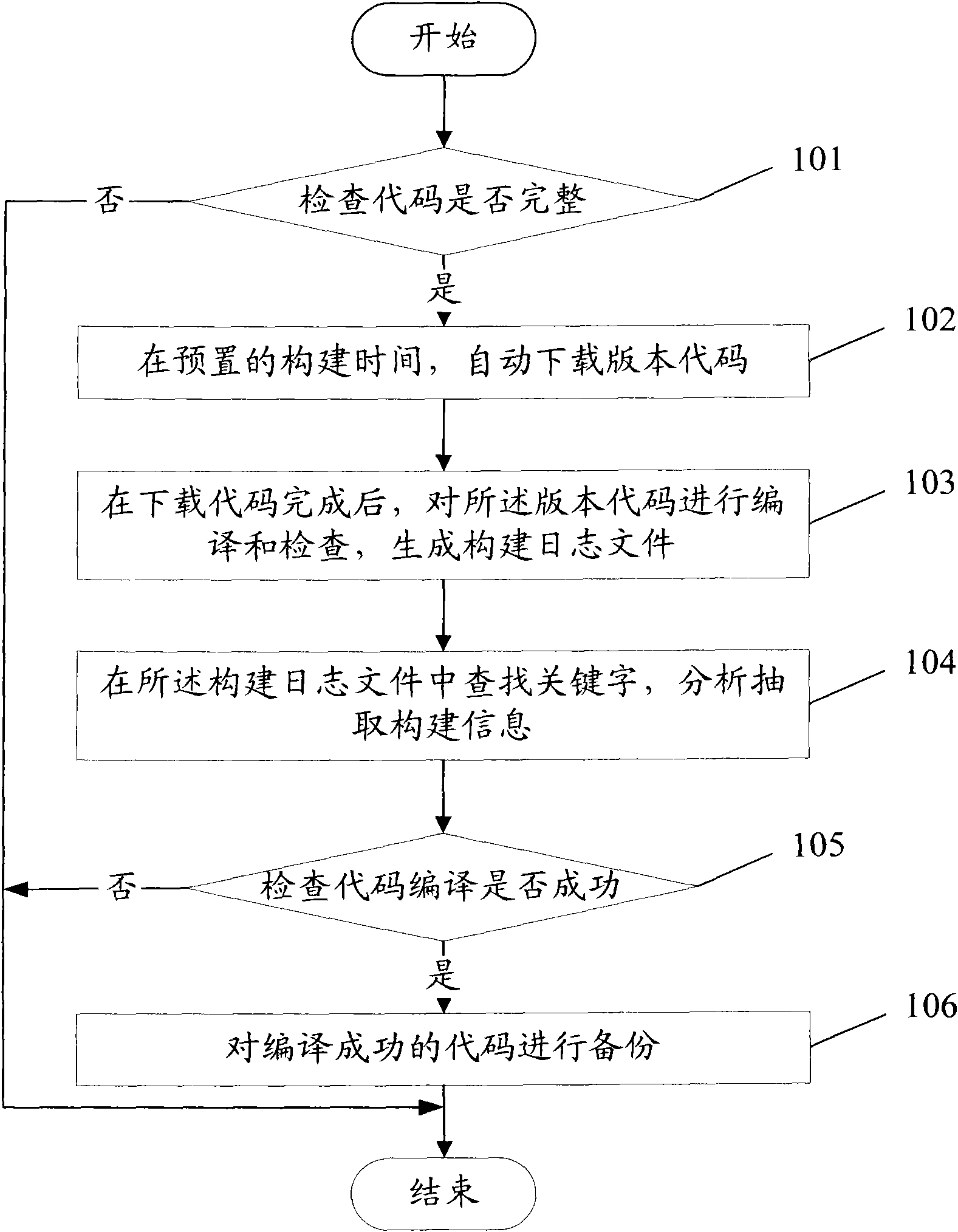

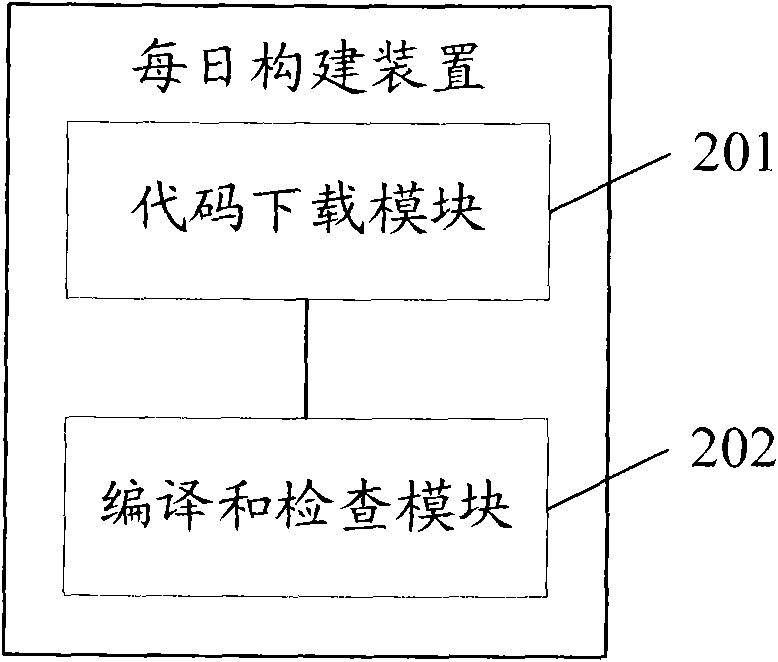

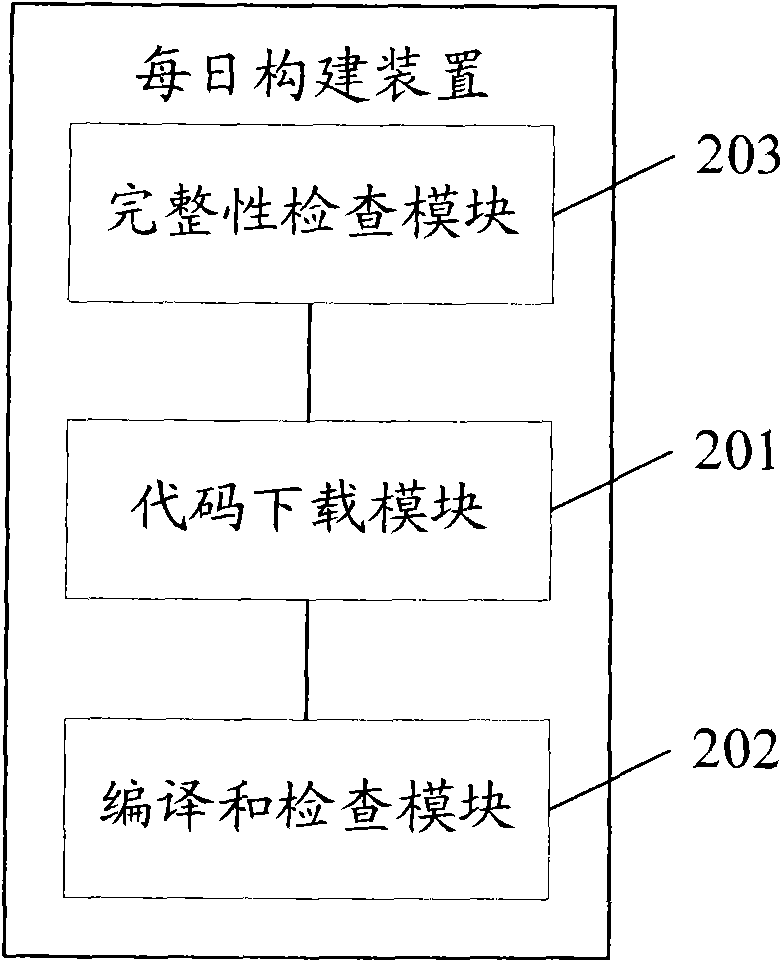

Daily constructing method and device

InactiveCN101650653AImplement integrated compilationImprove compilation efficiencySpecific program execution arrangementsQuality controlComputer engineering

The invention discloses daily constructing method and device, relating to the technical field of software and solving the problem that a constructing server cannot meet the requirements to translate and edit a great number of codes. The method comprises the following steps: automatically downloading an edition code within the preset constructing time; after finishing downloading the codes, translating, editing and checking the edition code to generate a constructed log file. The technical scheme provided by the invention is suitable for edition quality control.

Owner:ZTE CORP

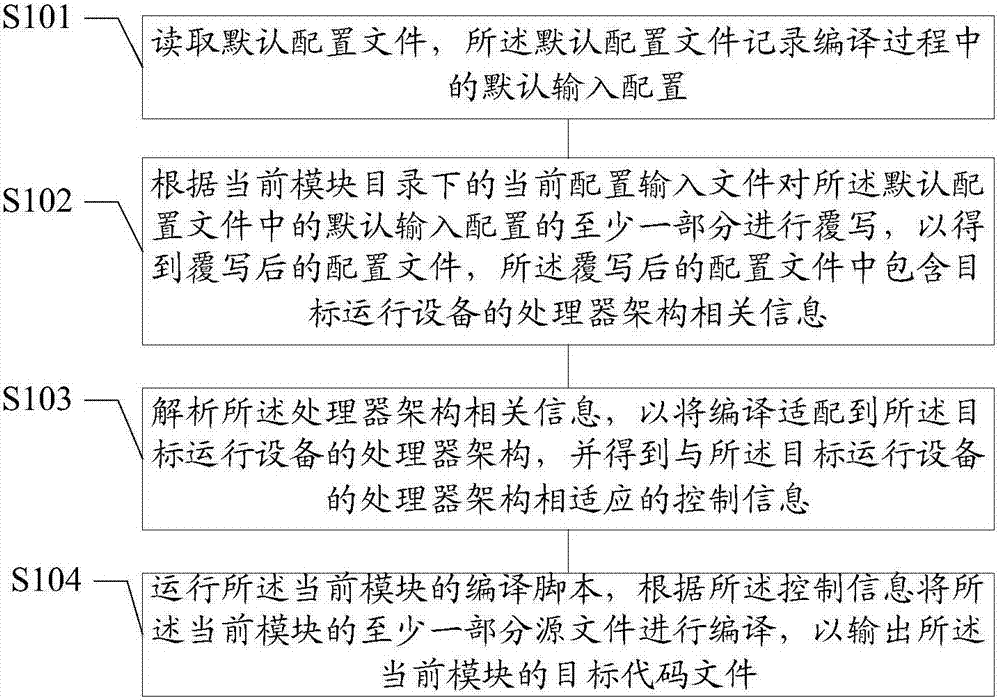

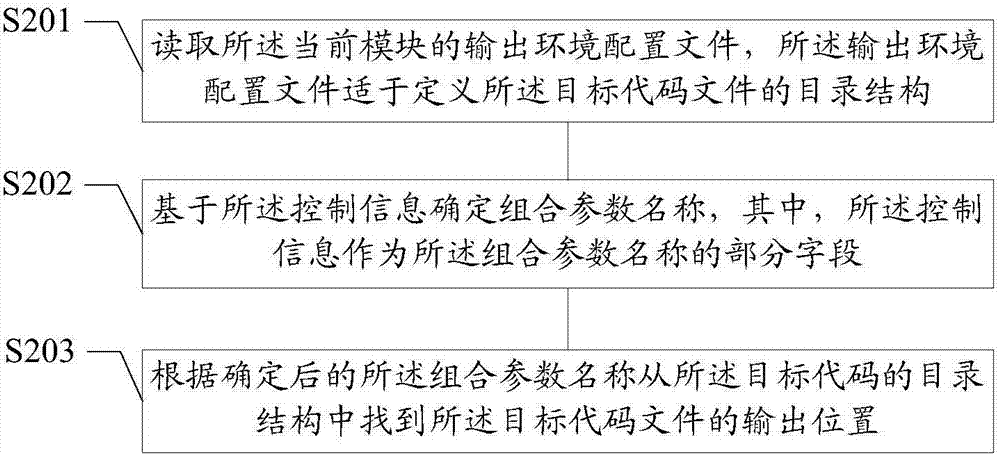

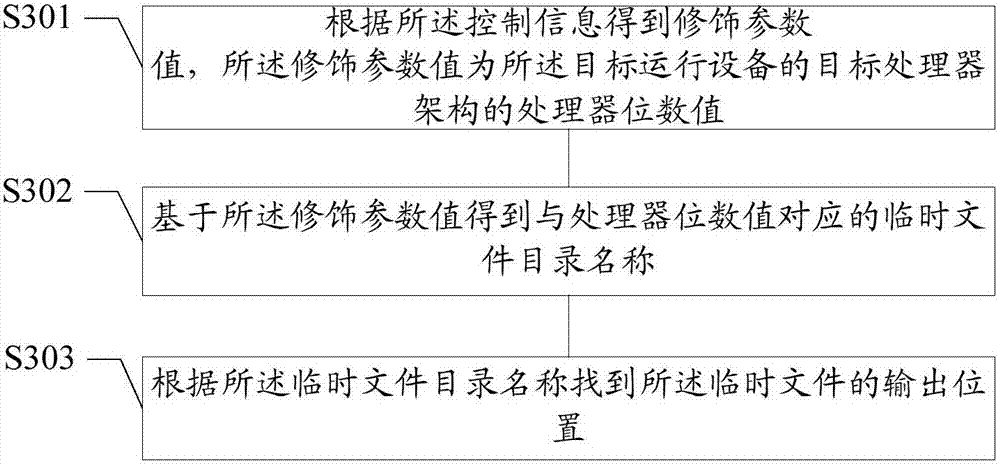

Compiling method and device adaptive to hardware architecture

ActiveCN107273176AImprove the efficiency of maintaining the compilation systemImprove compilation efficiencySoftware engineeringProgram controlRelevant informationHardware architecture

The invention discloses a compiling method and device adaptive to a hardware architecture. The method comprises the steps that a default configuration file is read, wherein the default configuration file records default input configuration in a compiling process; at least one part of the default input configuration in the default configuration file is overwritten according to a current configuration input file under a directory of a current module to obtain an overwritten configuration file, wherein the overwritten configuration file contains processor architecture relevant information of a target running device; the processor architecture relevant information is analyzed to compile a processor architecture adaptive to the target running device, and control information adaptive to the processor architecture of the target running device is obtained; and a compiling script of the current module is run, at least one part of a source file of the current module is compiled according to the control information, and a target code file of the current module is output. Through the scheme, compiling efficiency and compiling system maintenance efficiency can be improved.

Owner:SILEAD

Processor structure and instruction system representation method based on multi-dimensional variable description table

InactiveCN101645005ATo achieve compilation workScalableSpecific program execution arrangementsReverse analysisProcessor register

The invention relates to the field of reverse analysis of computer softwares, in particular to a processor structure and an instruction system representation method based on a multi-dimensional variable description table. The method adopts a multi-layer triple nested table (Table) to construct a structural characteristic library and an instruction system description template of processors, the Table is represented as [<Tp1, Ts1, Ti1>, <Tp2, Ts2, Ti2>, ..., <Tpn, Tsn, Tin>], each triple <Tpn, Tsn, Tin> represents one processor, Tpn performs the classification, indexing and screening on the processors, Tsn provides register structure information, interruption structure information, reset address information and storage space distribution information, Tin provides a machine code, an assemblyexpression and the mapping relation between the machine code and the assembly expression, data in the Table is extracted from an information database of the processors, and the information database ofthe processors can be managed and maintained. The method has strong universality, and can be used for most of the prior processors.

Owner:THE PLA INFORMATION ENG UNIV

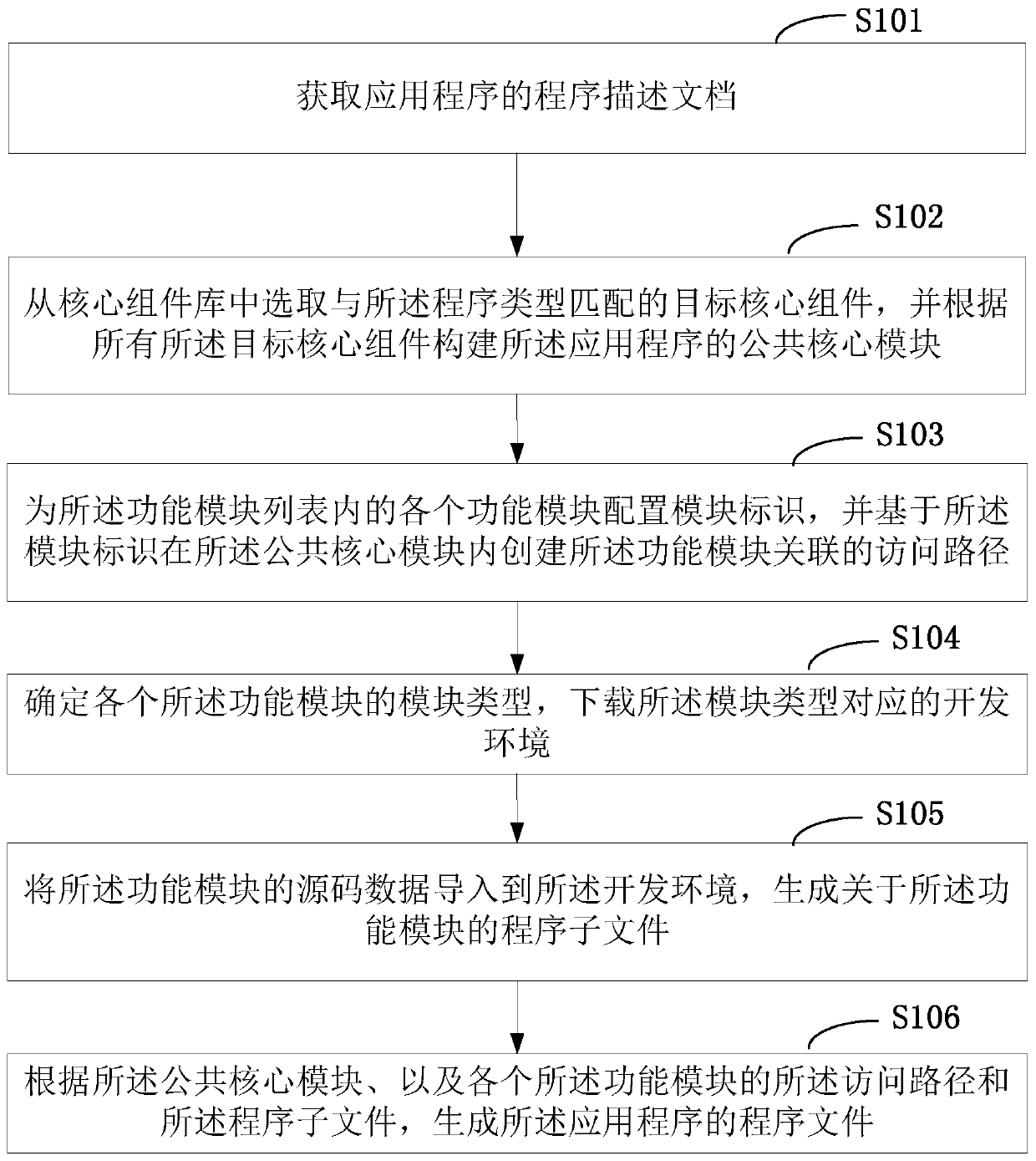

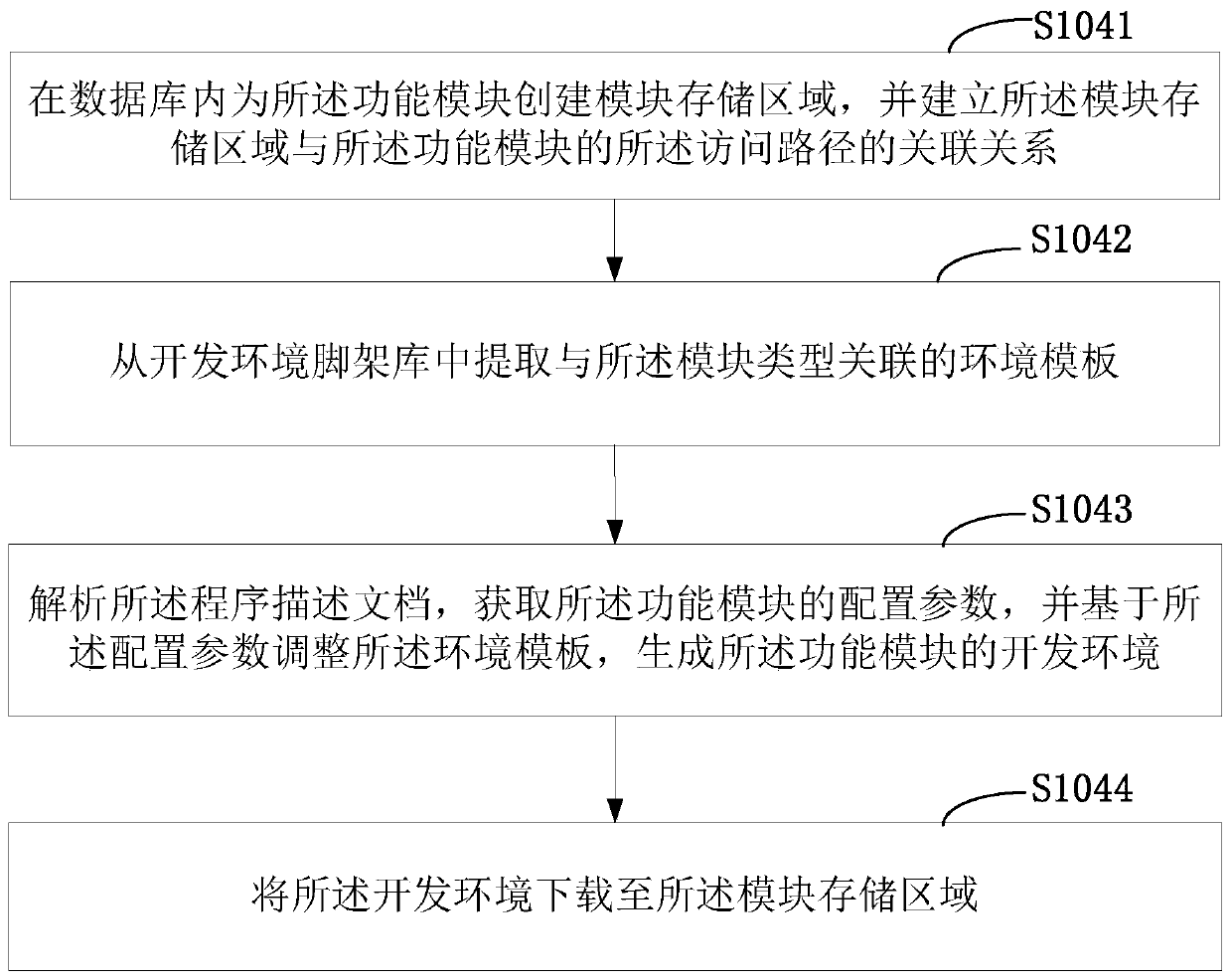

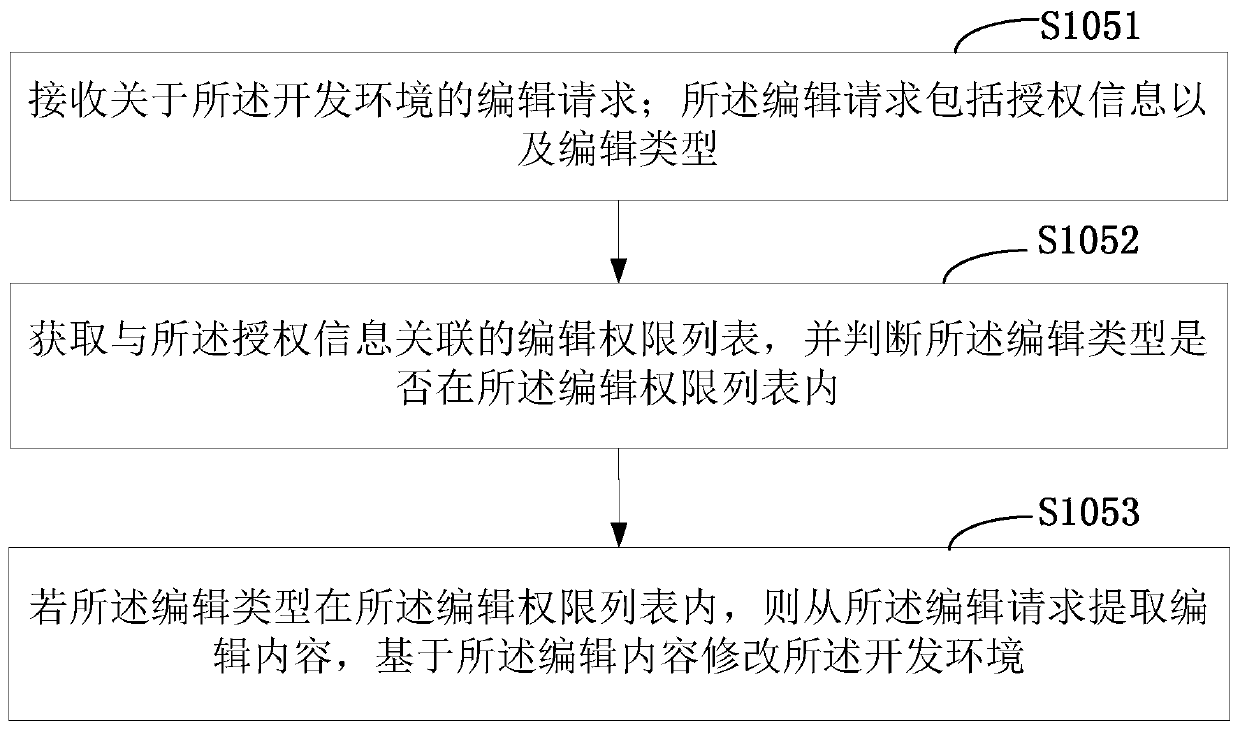

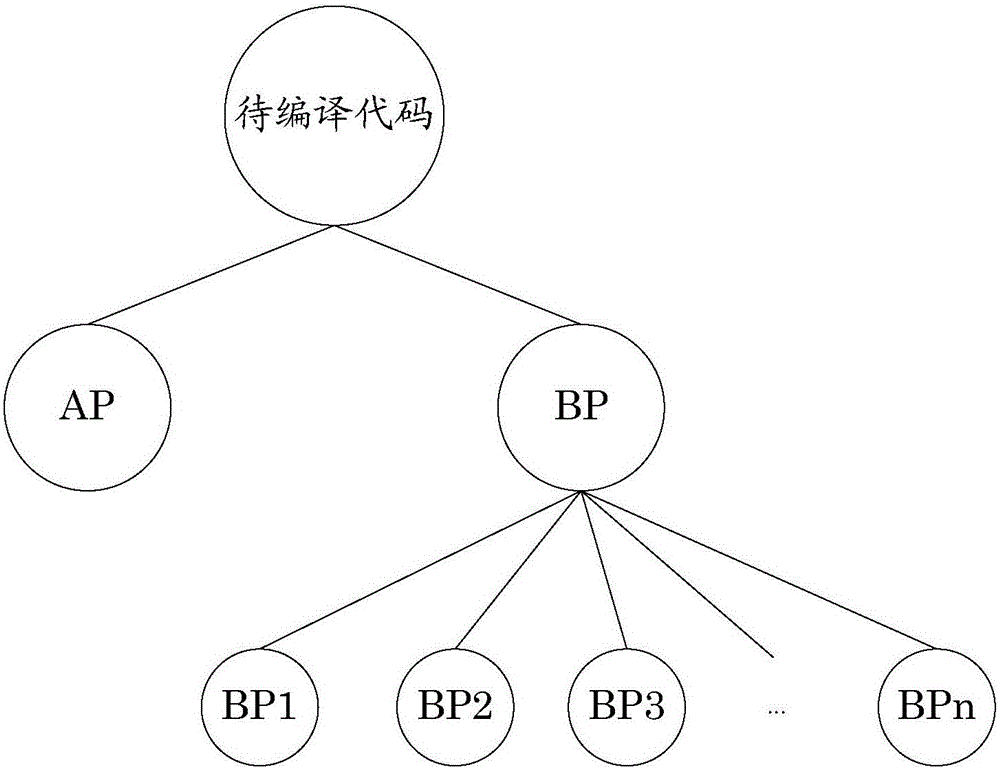

An application program generation method and device

PendingCN109885311AReduce couplingAchieve independent goalsSoftware designCode compilationCouplingCore component

The invention is suitable for the technical field of software programs, and provides an application program generation method and device. The method comprises the steps of obtaining a program description document of an application program; selecting a target core component matched with the program type from the core component library, and constructing a common core module of the application program according to all the target core components; configuring a module identifier for each functional module in the functional module list, and creating an access path associated with the functional module in the public core module based on the module identifier; determining the module type of each functional module, and downloading a development environment corresponding to the module type; importing the source code data of the function module into a development environment, and generating a program subfile related to the function module; and generating a program file of the application programaccording to the public core module and the access path and the program subfile of each functional module. According to the method and the device, the coupling degree between the modules is reduced, the purpose of independent compiling is achieved, the compiling efficiency is improved, and the development time is shortened.

Owner:PING AN TECH (SHENZHEN) CO LTD

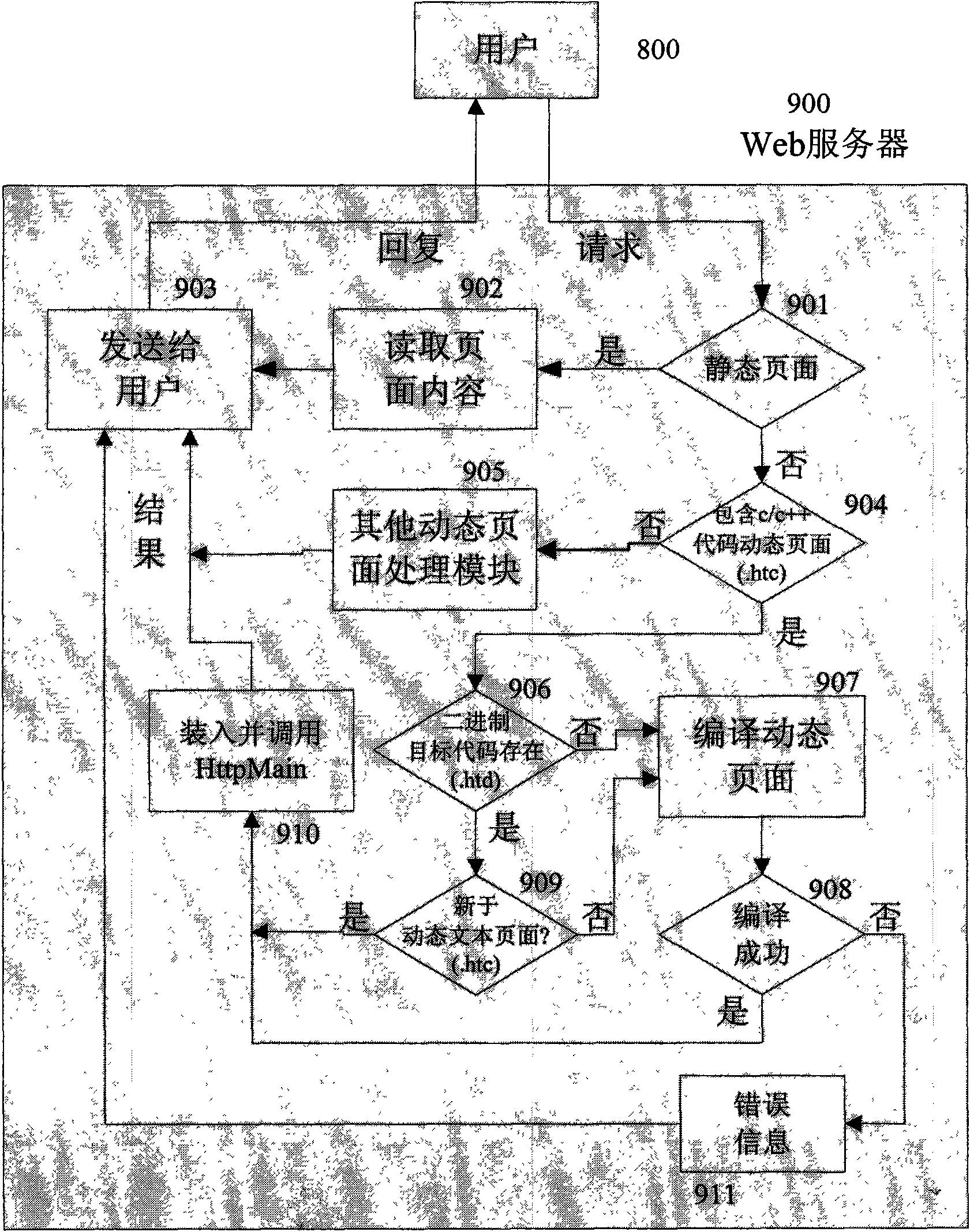

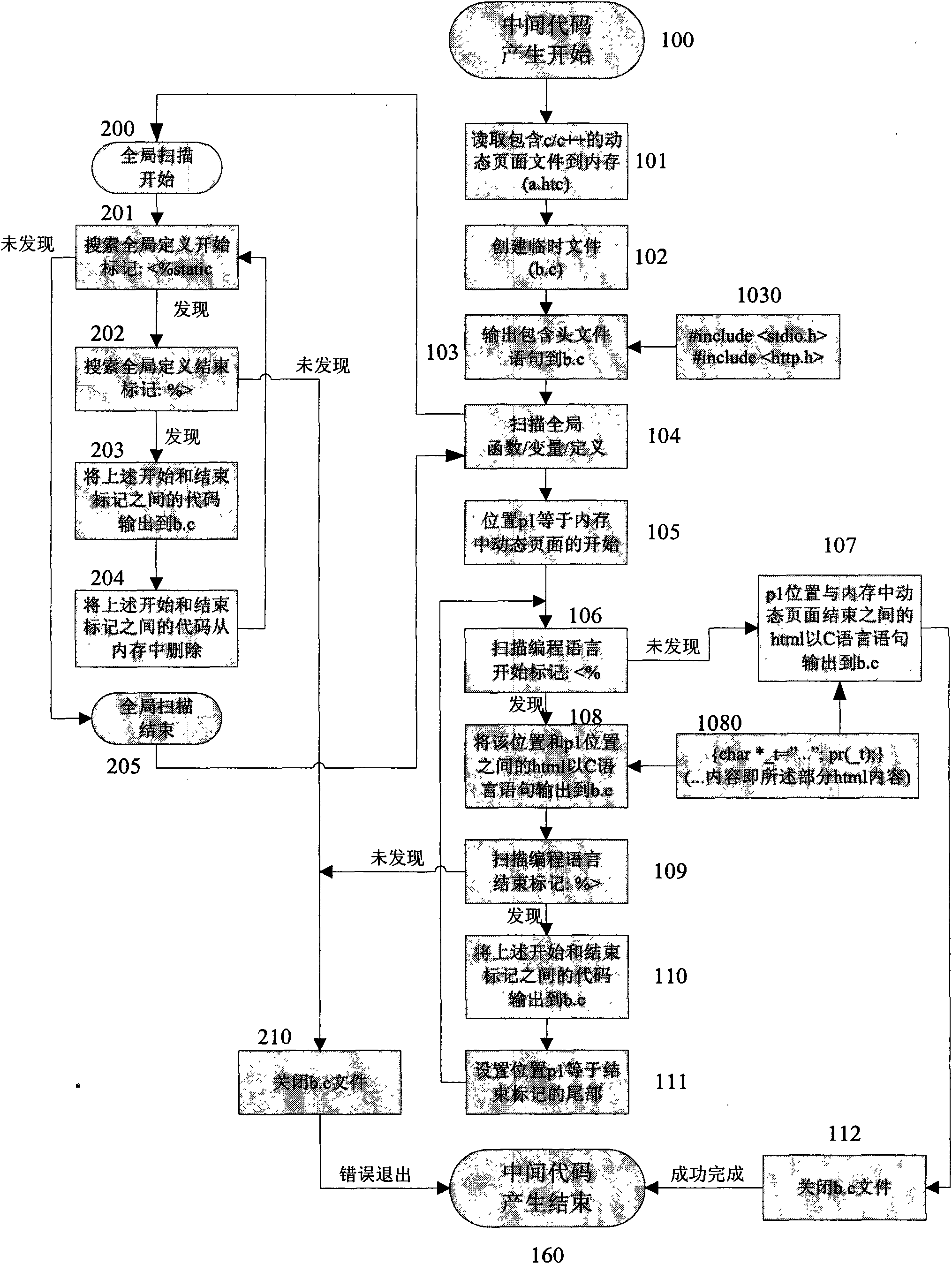

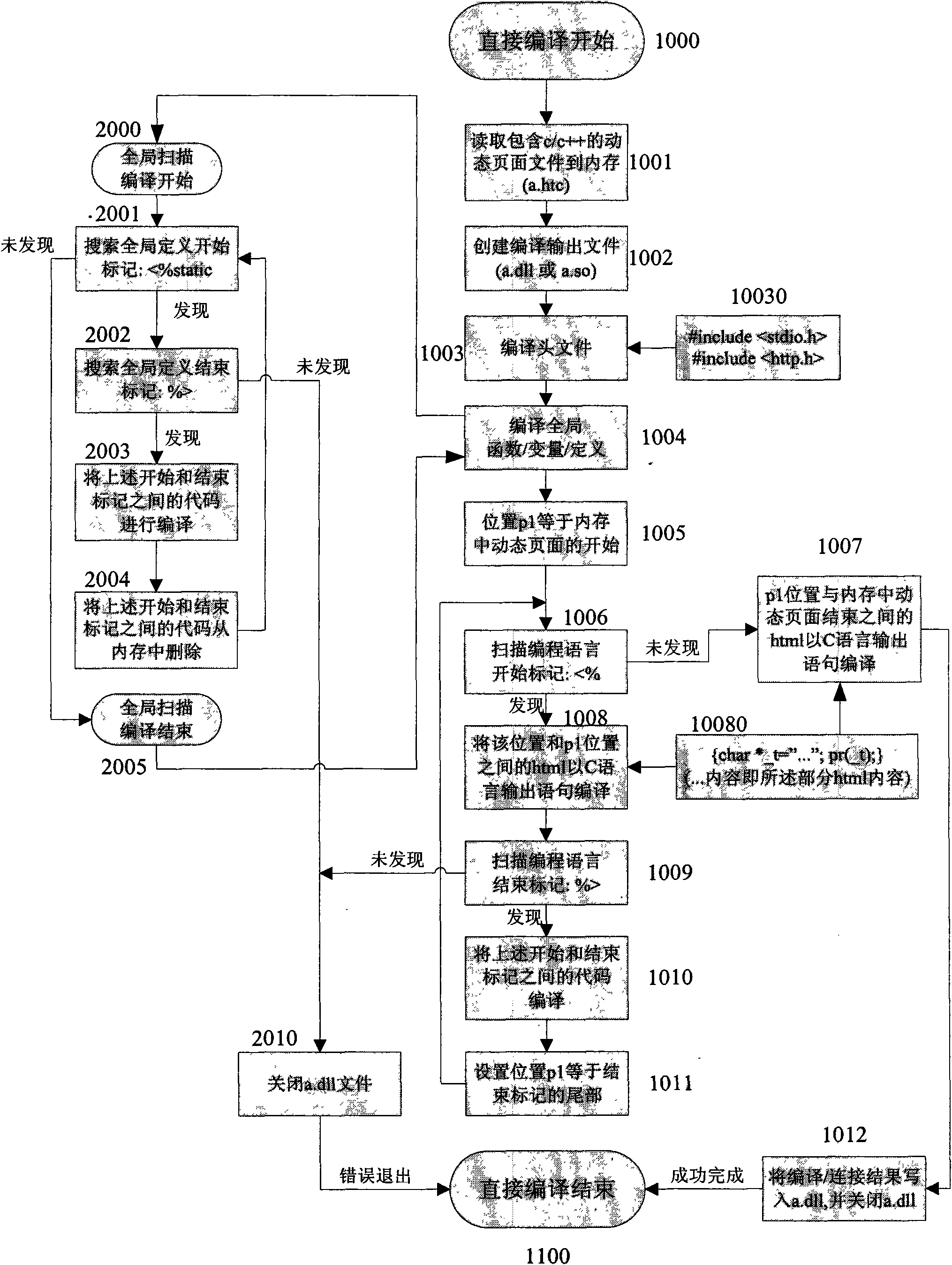

Method and system for web server

InactiveCN102141991AImprove compilation efficiencyImprove execution speedSpecial data processing applicationsWell controlHuman language

The invention relates to a method and system for a web server. The method and system provided by the invention are used for better control the performance and efficiency of the web server and comprise a dynamic webpage generating method. In the dynamic webpage generating method, c or c++ codes are used as the programming language for embedding web pages; the c / c++ codes are compiled in the server into binary machine codes which are directly operated in a CPU (Central Processing Unit); and the c / c++ codes are compiled in the first operation. The invention simultaneously provides a method used for compiling dynamic pages and an optimization method for enhancing the server based on the dynamic pages, and the methods comprise the following steps: setting a temporary storage space in the server, packing static pages or the dynamic pages and the like.

Owner:钟巨航

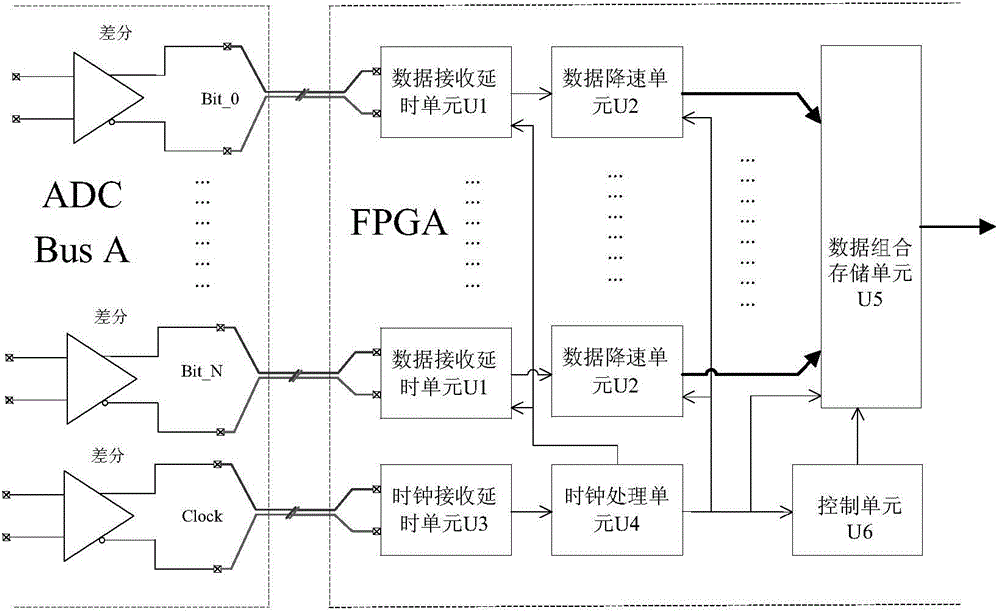

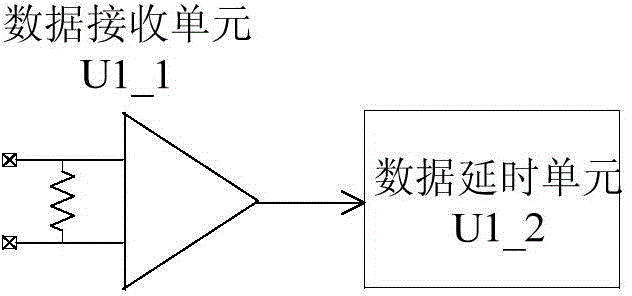

High-speed ADC (Analog to Digital Converter) sampled data receiving and buffering method and system based on FPGA (Field Programmable Gate Array)

ActiveCN104407998AEasy to handleReduce data errorsElectric digital data processingData combinationData delay

The invention provides a high-speed ADC (Analog to Digital Converter) sampled data receiving and buffering method and system based on an FPGA (Field Programmable Gate Array). The system mainly comprises a data receiving delay unit, a data speed-down unit, a clock receiving delay unit, a clock processing unit, a data combination storage unit and a control unit. Inside the FPGA, the data speed-down unit is used for lowering the speed of a data signal, a clock signal uses double-edge latch data, and the data delay unit is used for performing delay adjustment on a plurality of pairs of data signals, so that simultaneous hop of the pairs of data signals is ensured; the hop edge of the clock signal is positioned in the center of the data signal; the data combination unit is used for combining and arranging widened and slowed-down data to recover practical waveform data; the practical waveform data is stored in the data storage unit. By adopting the method and the system, a plurality of paths of data signals and clock signals accompanying the data can be received simultaneously, and the functions of circular storage, pre-trigger recording, sequential read-out and the like of the data signal are realized.

Owner:NORTHWEST INST OF NUCLEAR TECH

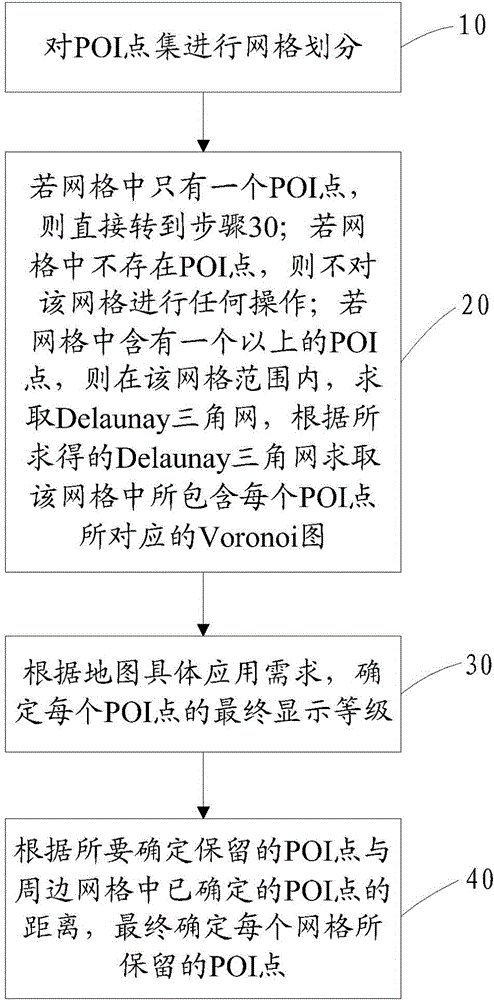

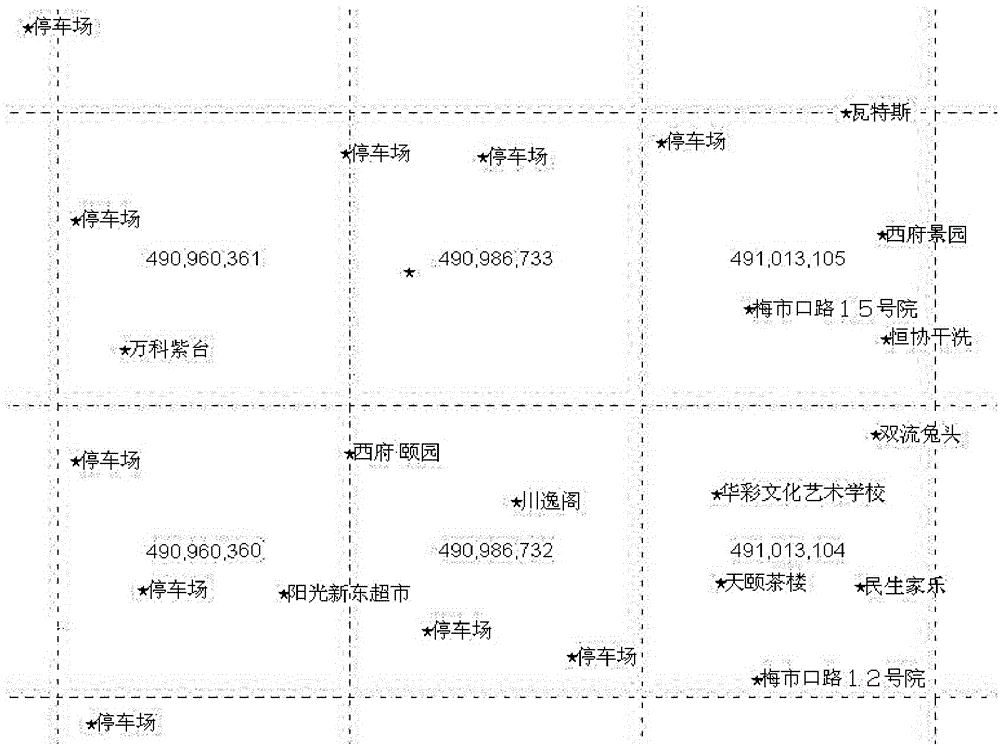

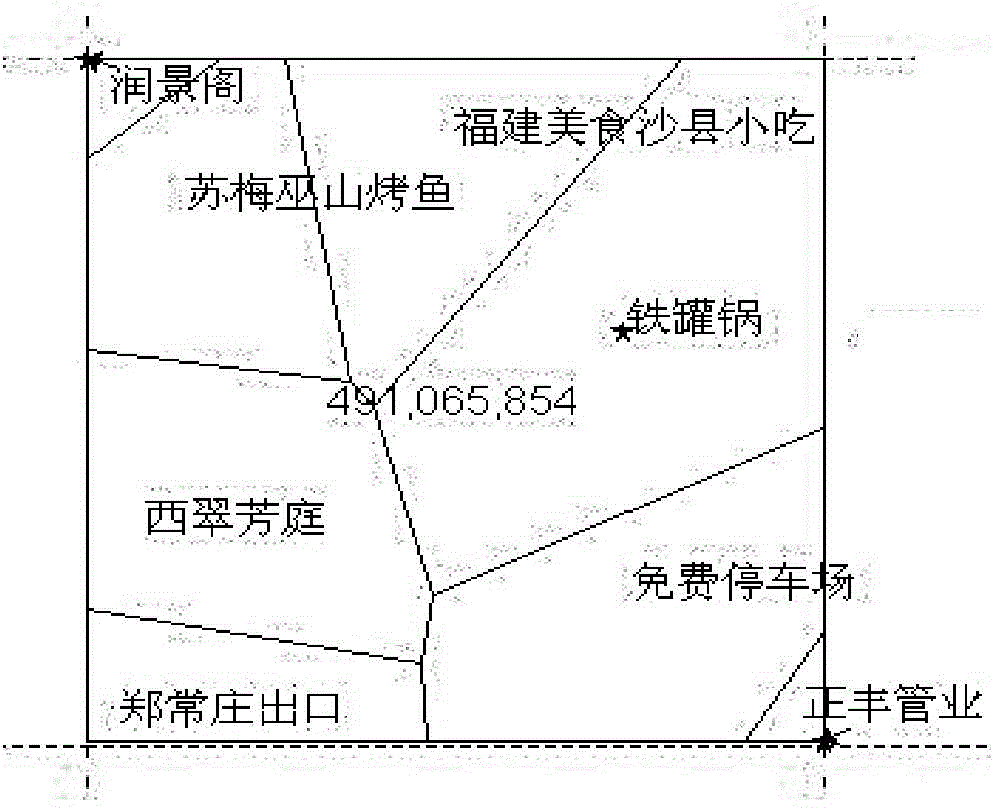

Voronoi diagram-based electronic map point element screening method

InactiveCN103824510AImprove compilation efficiencyAvoid conflictMaps/plans/chartsTheoretical computer scienceGrid partition

Owner:XIAMEN YAXON NETWORKS CO LTD

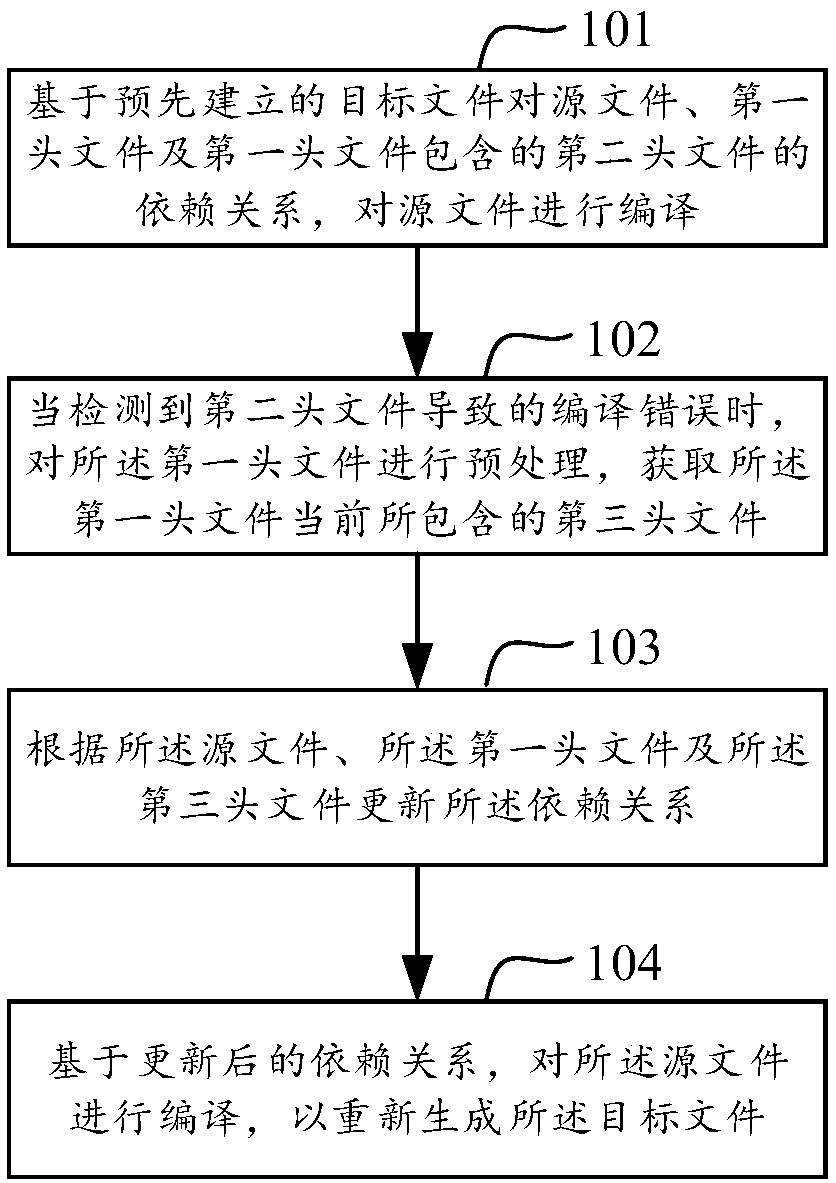

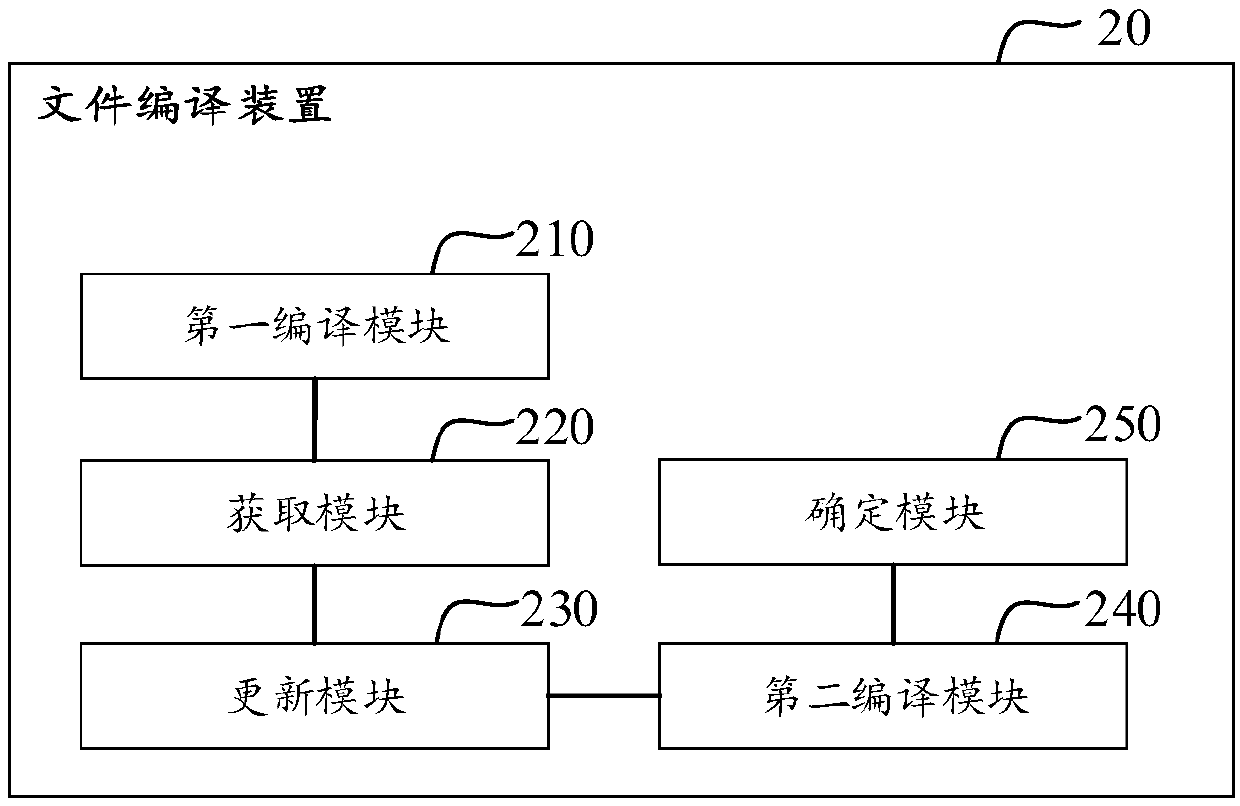

File compiling method and device

InactiveCN108153529AAchieve normal executionSave compilation timeCode compilationCompilation errorObject file

Owner:HANGZHOU DPTECH TECH

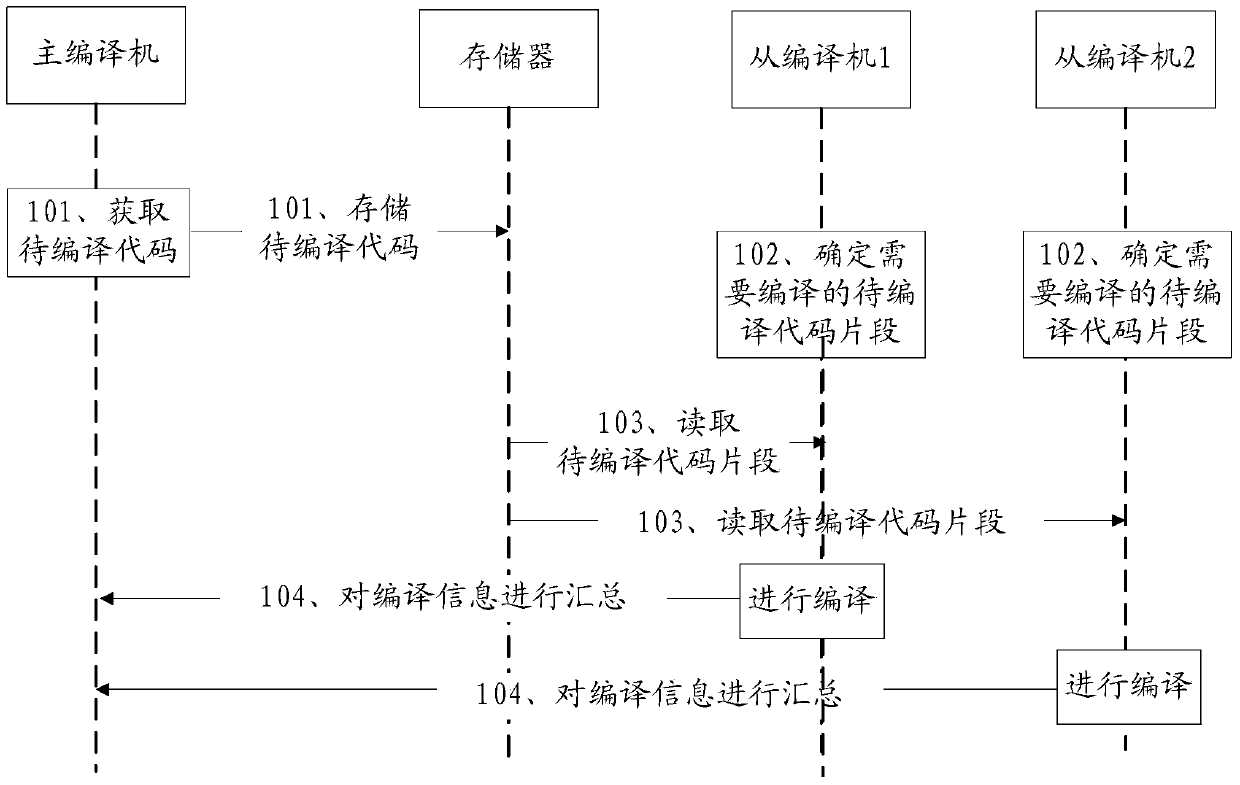

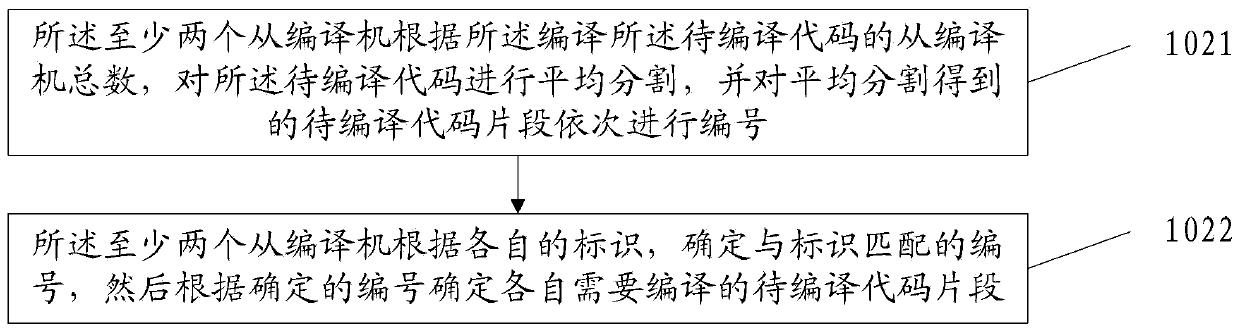

Distributed authoring and versioning method and system

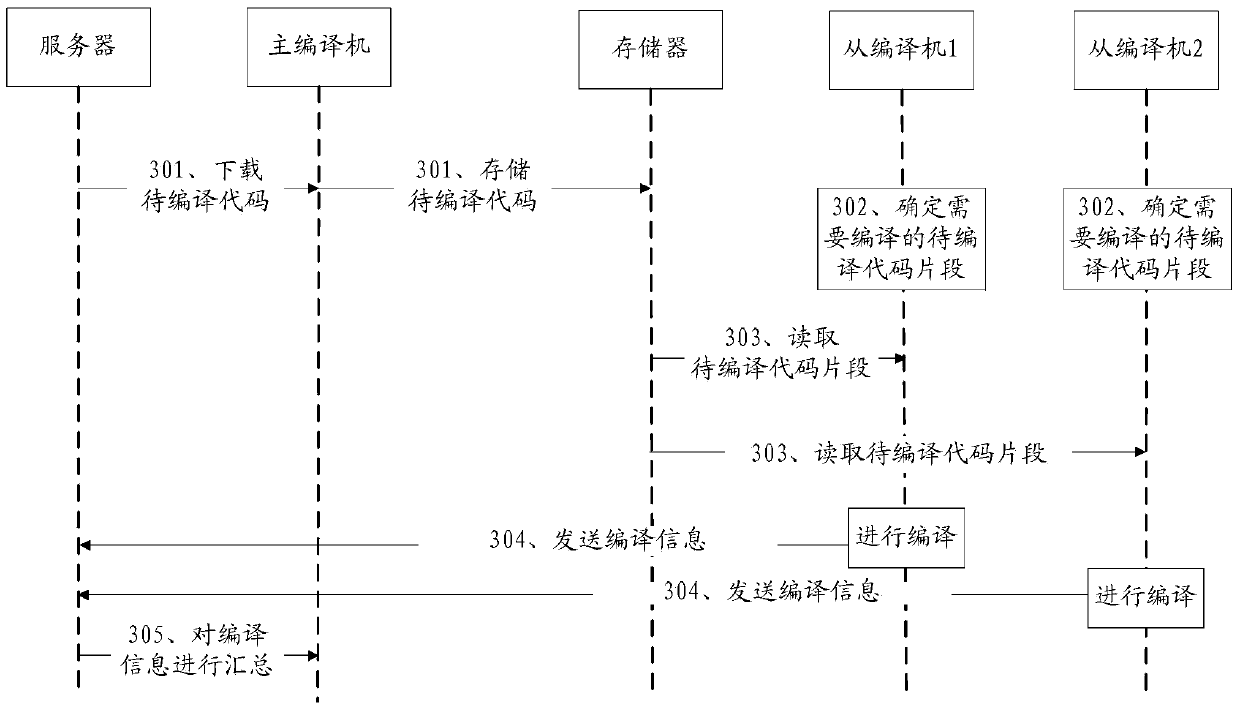

InactiveCN103440136AReduce loadImprove compilation efficiencySpecific program execution arrangementsInformation processingSoftware development

The invention discloses a distributed authoring and versioning method and a distributed authoring and versioning system, relating to the field of information processing and being used for solving the problem of long authoring and versioning time caused by low software code authoring and versioning efficiency. The method provided by the invention specifically comprises the following steps: independently determining a mode of a to-be-authored and versioned code segment needing being authored and versioned by adopting each slave server, and averagely sharing time consumption of allocating tasks to each slave server so as to increase the authoring and versioning efficiency of software and shorten the authoring and versioning time. The embodiment of the invention is mainly used in a process of developing software.

Owner:MAIPU COMM TECH CO LTD

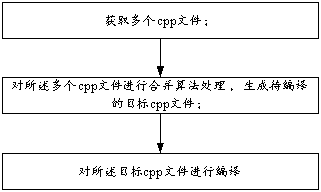

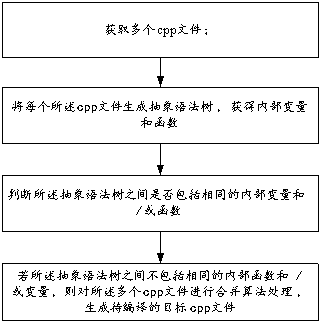

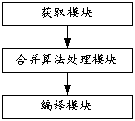

C + + program compiling method and device

The invention provides a C + + program compiling method which comprises the following steps: obtaining a plurality of cpp files, carrying out merging algorithm processing on the plurality of cpp filesto generate a to-be-compiled target cpp file, and finally compiling the target cpp file. According to the method, a large number of cpp files are prevented from being compiled; E; each cpp file needsto be independently preprocessed, compiled, assembled and compiled to generate a target link, and the combined cpp files are directly and uniformly compiled, so that various system resources and a large amount of time cost and system cost are saved, t, the compiling process of a C + + program is accelerated, and the performance of the system is improved.

Owner:北京龙创悦动网络科技有限公司

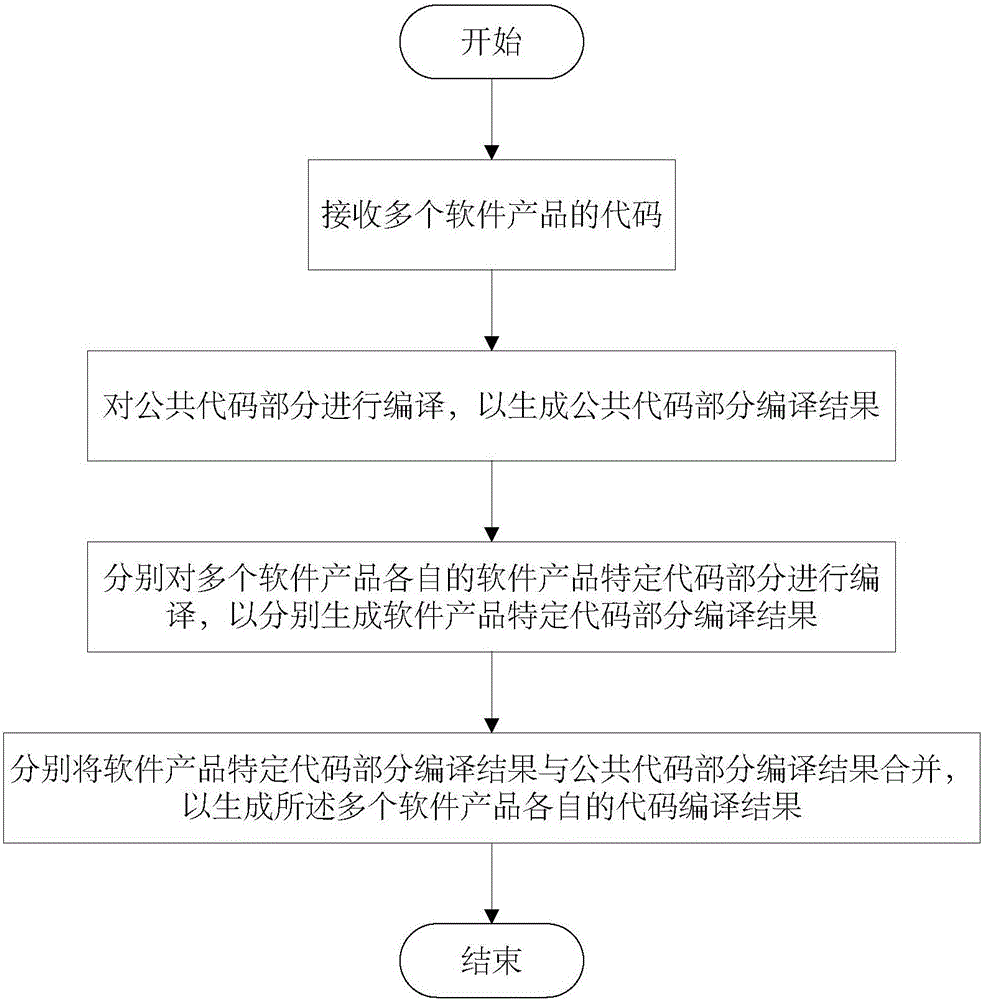

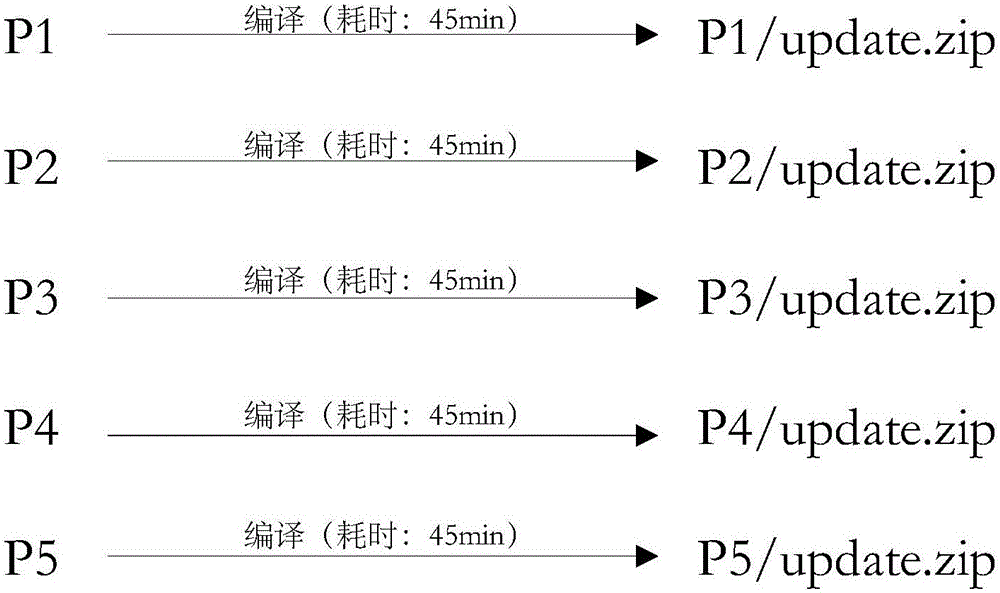

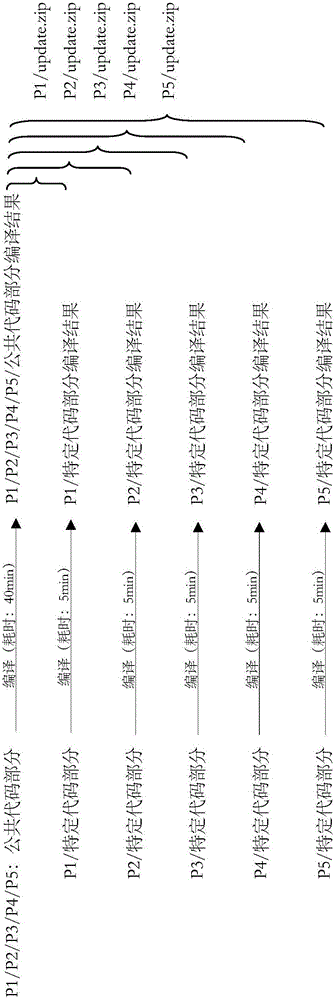

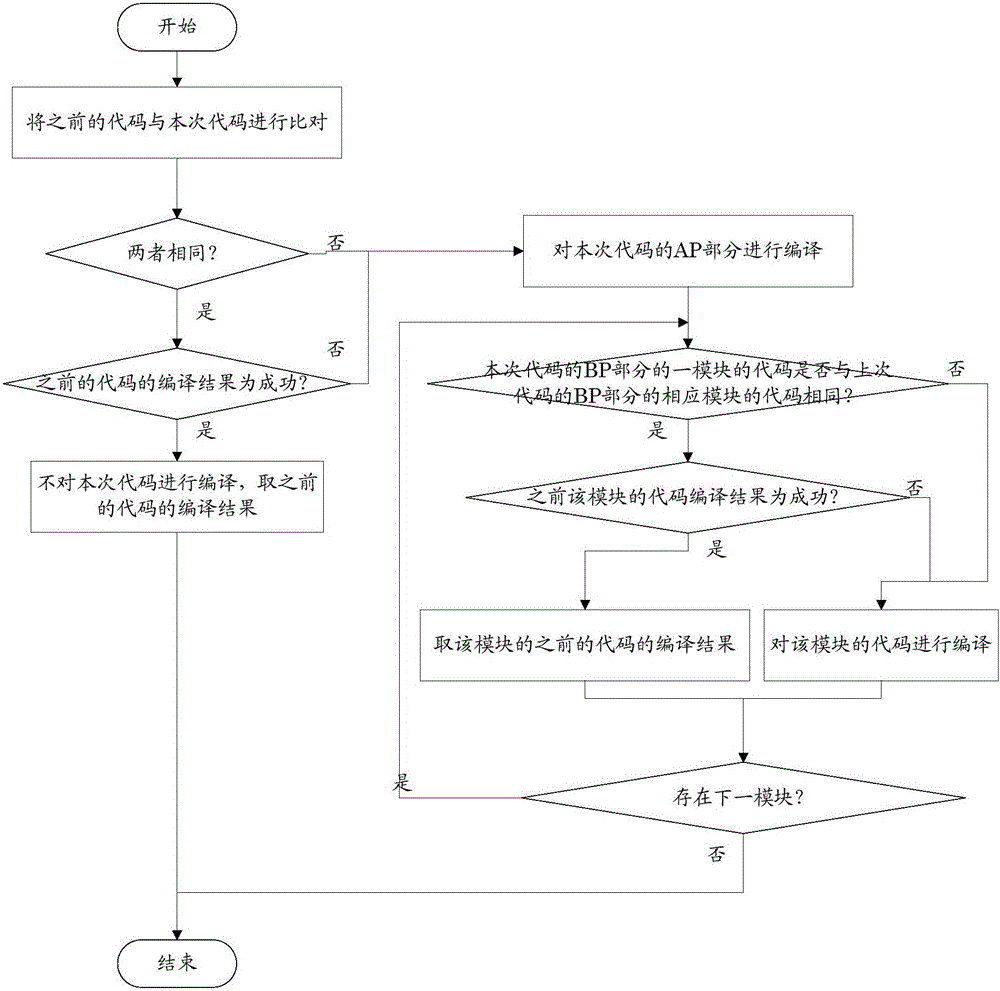

Software product compiling method and device

InactiveCN105867993ASave compilation timeSave compilation resourcesSoftware engineeringProgram controlResource consumptionSoftware engineering

The invention relates to the technical field of software, and discloses a software product compiling method and device. By means of the software product compiling method and device, the compiling process can be optimized, the compiling time and resource consumption can be reduced, and the compiling efficiency can be improved. The software product compiling method includes the steps that codes of multiple software products are received, wherein the code of each software product comprises a public code part and a software product specific code part; the public code part is compiled to generate a public code part compiling result; the software product specific code parts of the software products are compiled respectively to generate software product specific code part compiling results of the software products respectively; the software product specific code part compiling results of the software products are combined with the public code part compiling result to generate code compiling results of the software products.

Owner:LETV HLDG BEIJING CO LTD +1

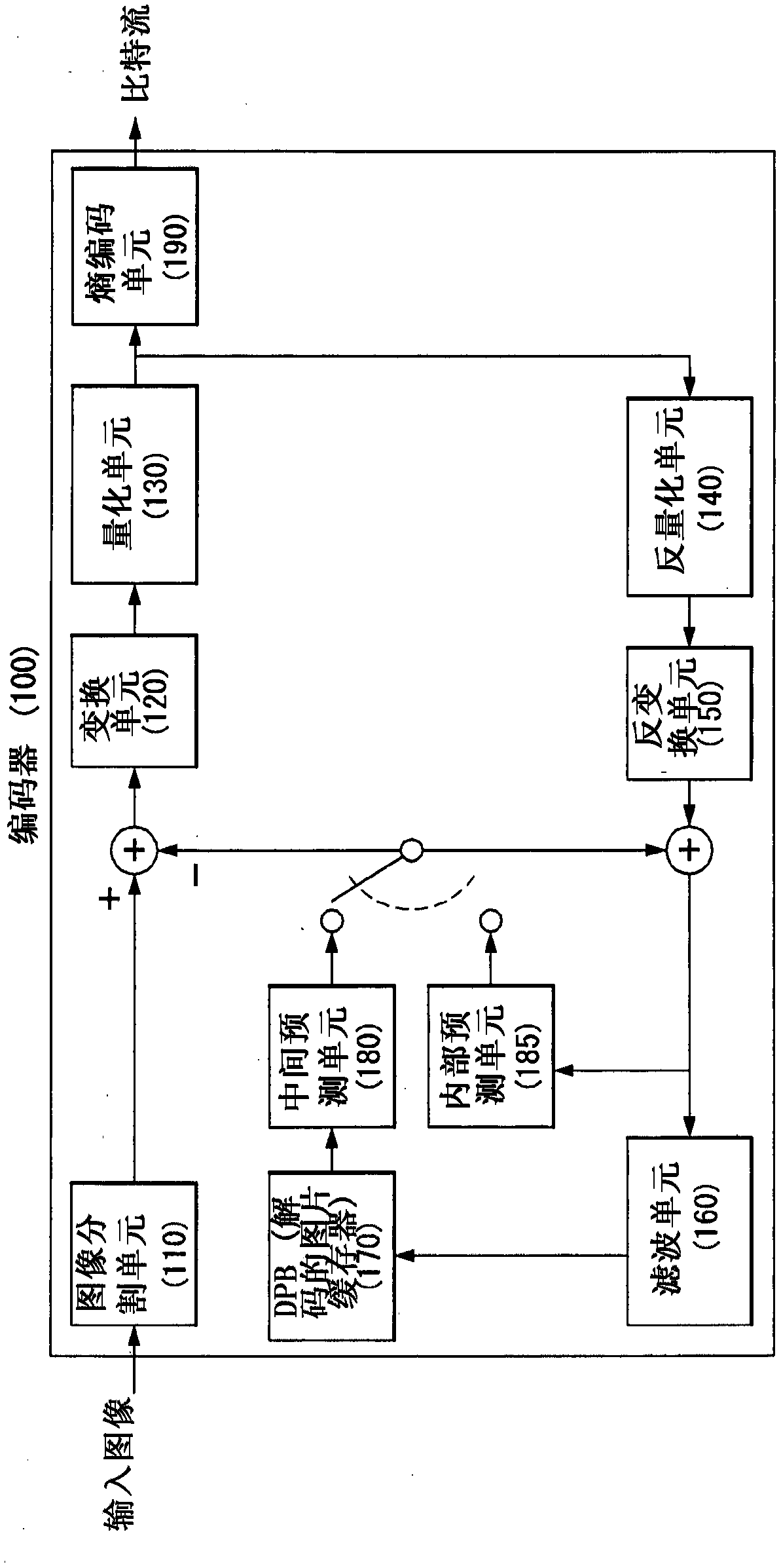

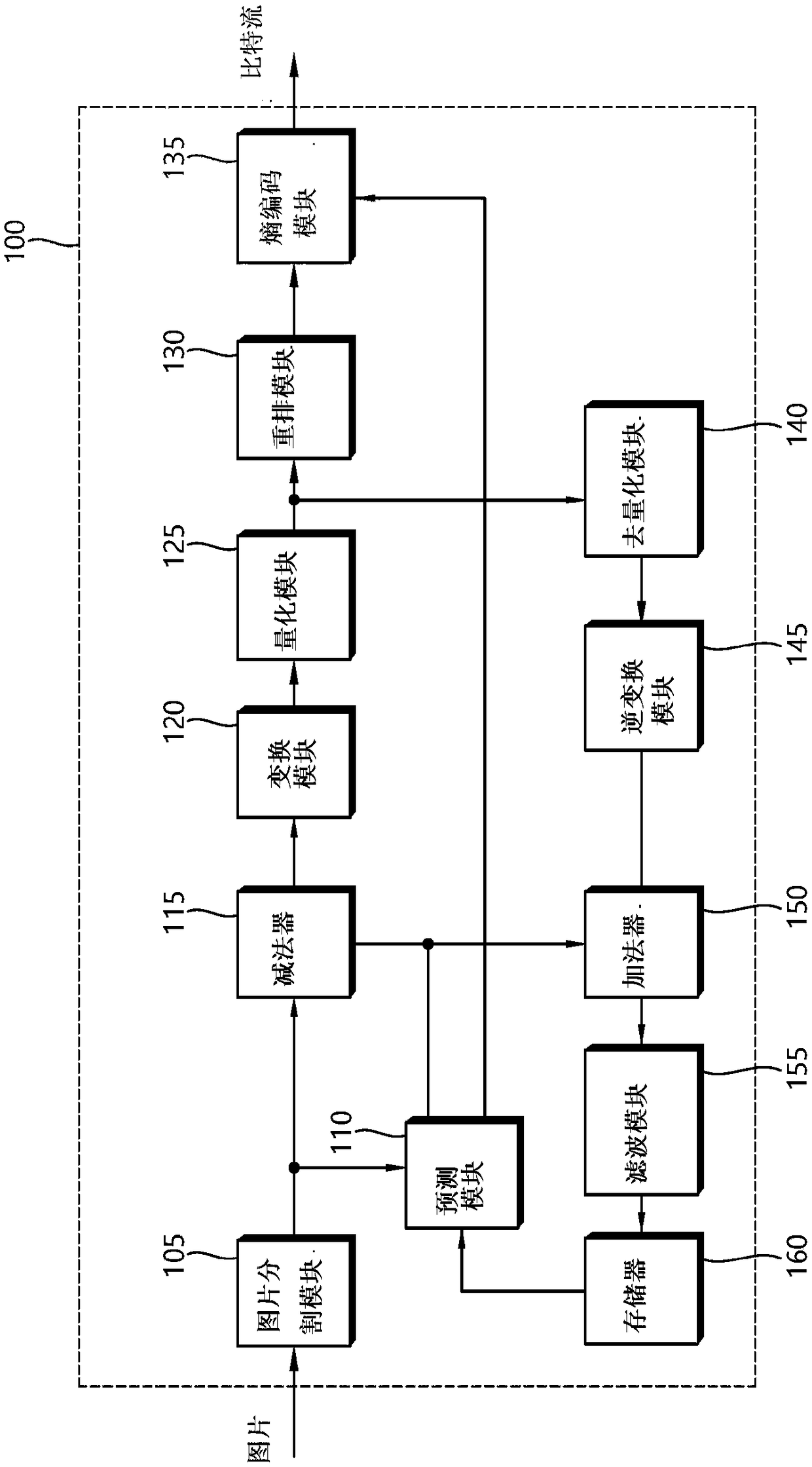

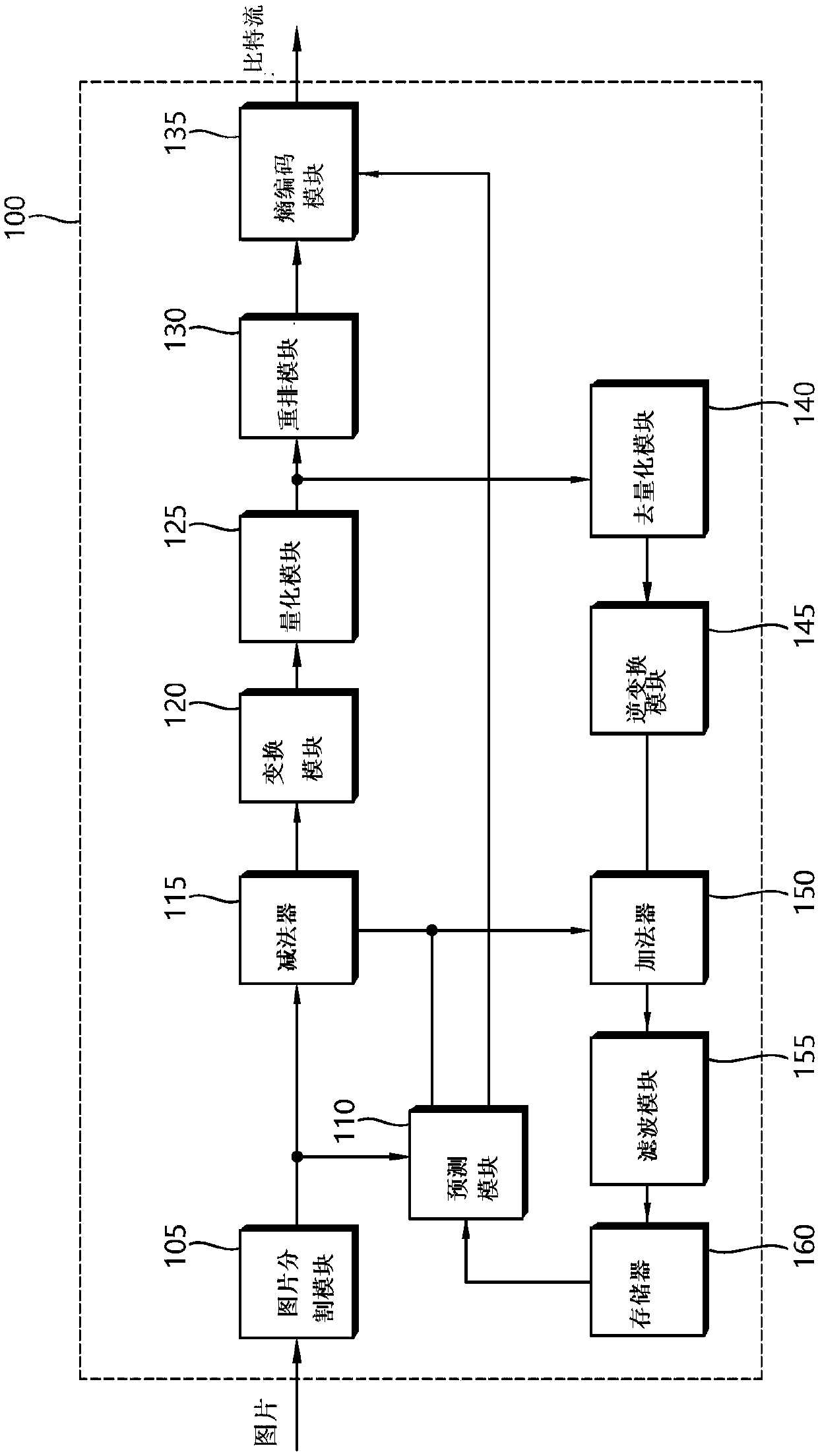

Device and method for performing transform by using singleton coefficient update

InactiveCN108028945AImprove compilation efficiencyReduce complexityMathematical modelsDigital video signal modificationAlgorithmEntropy encoding

The present invention provides a method for encoding a video signal, the method comprising: a step of selecting a transform parameter set via an optimization process for a target block, wherein the transform parameter set comprises a vertical transform set, a horizontal transform set and a transform order parameter set; a step of updating, on the basis of the selected transform parameter set, a transform block having a singleton coefficient, wherein the singleton coefficient represents a single coefficient obtained on the basis of the transform order parameter set; a step of obtaining a transform coefficient for the target block on the basis of the updated transform block; a step of quantizing the transform coefficient; and a step of entropy encoding the quantized transform coefficient.

Owner:LG ELECTRONICS INC

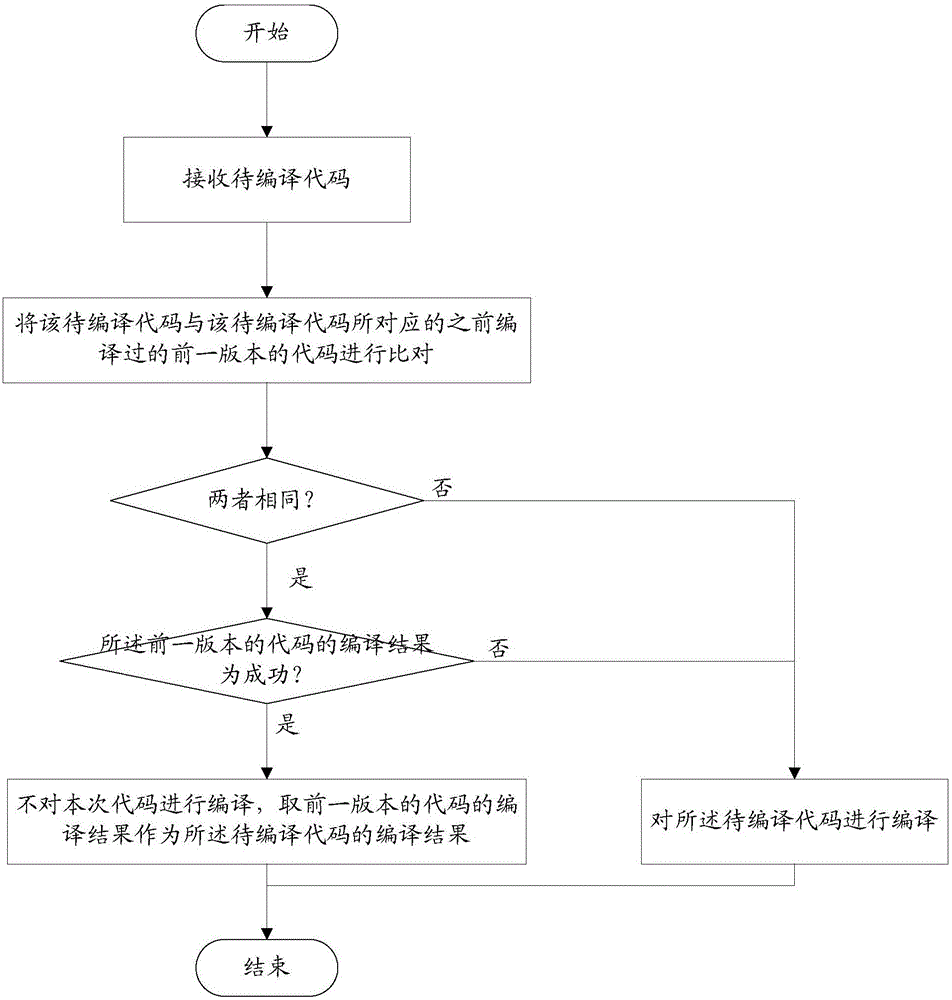

Software product compiling method and equipment

InactiveCN105843662AReduce repeated compilationImprove compilation efficiencyProgram controlMemory systemsSoftware engineeringComputers technology

The invention relates to the field of the computer technology, and discloses a software product compiling method and equipment. The software product compiling method and equipment can greatly improve compiling efficiency. In order to realize the above purpose, the invention provides the software product compiling method, which comprises the following steps: receiving a code to be compiled; comparing the code to be compiled with the compiled code of a previous version, wherein the compiled code corresponds to the code to be compiled; and according to a comparison result, determining whether the code to be compiled is compiled or not.

Owner:LETV HLDG BEIJING CO LTD +1

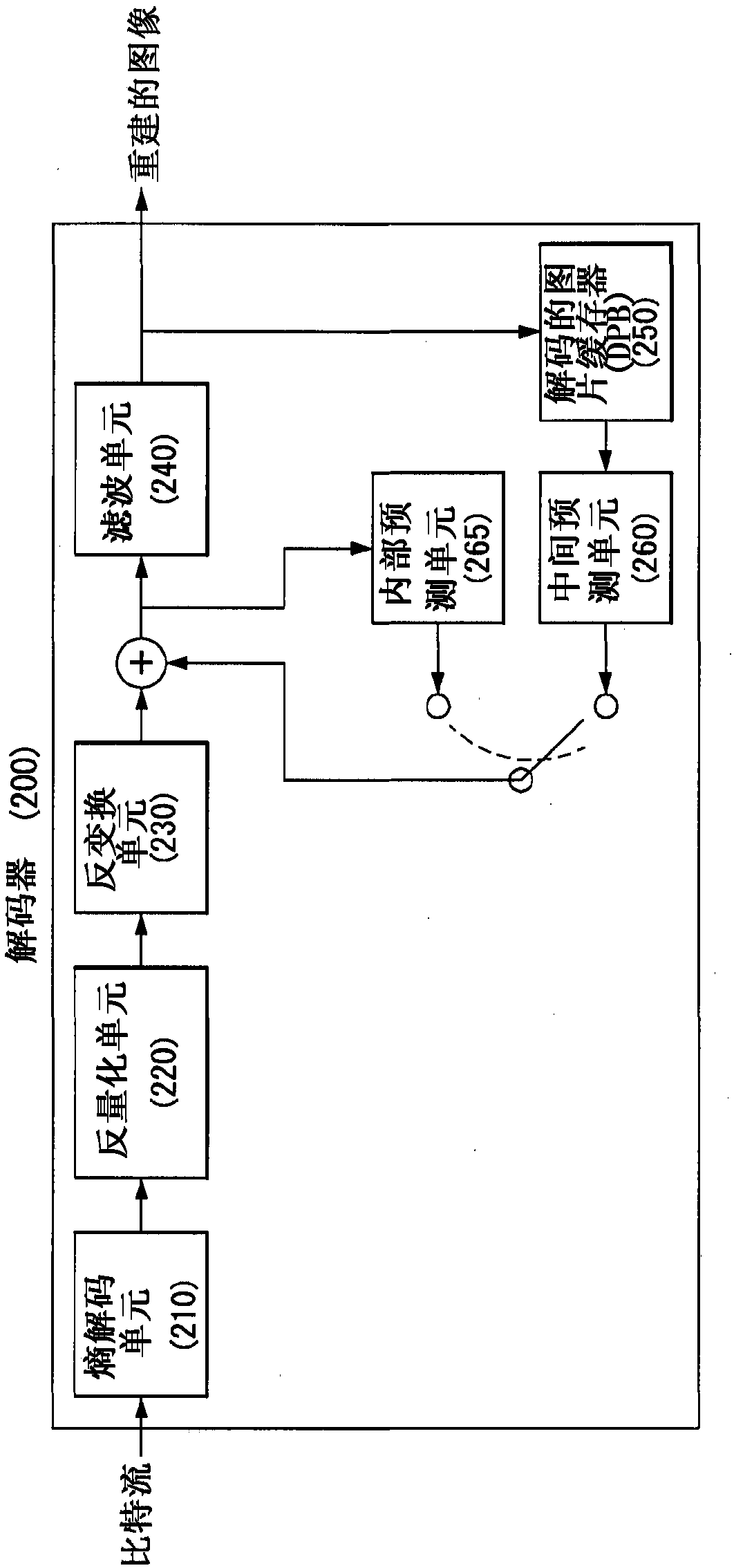

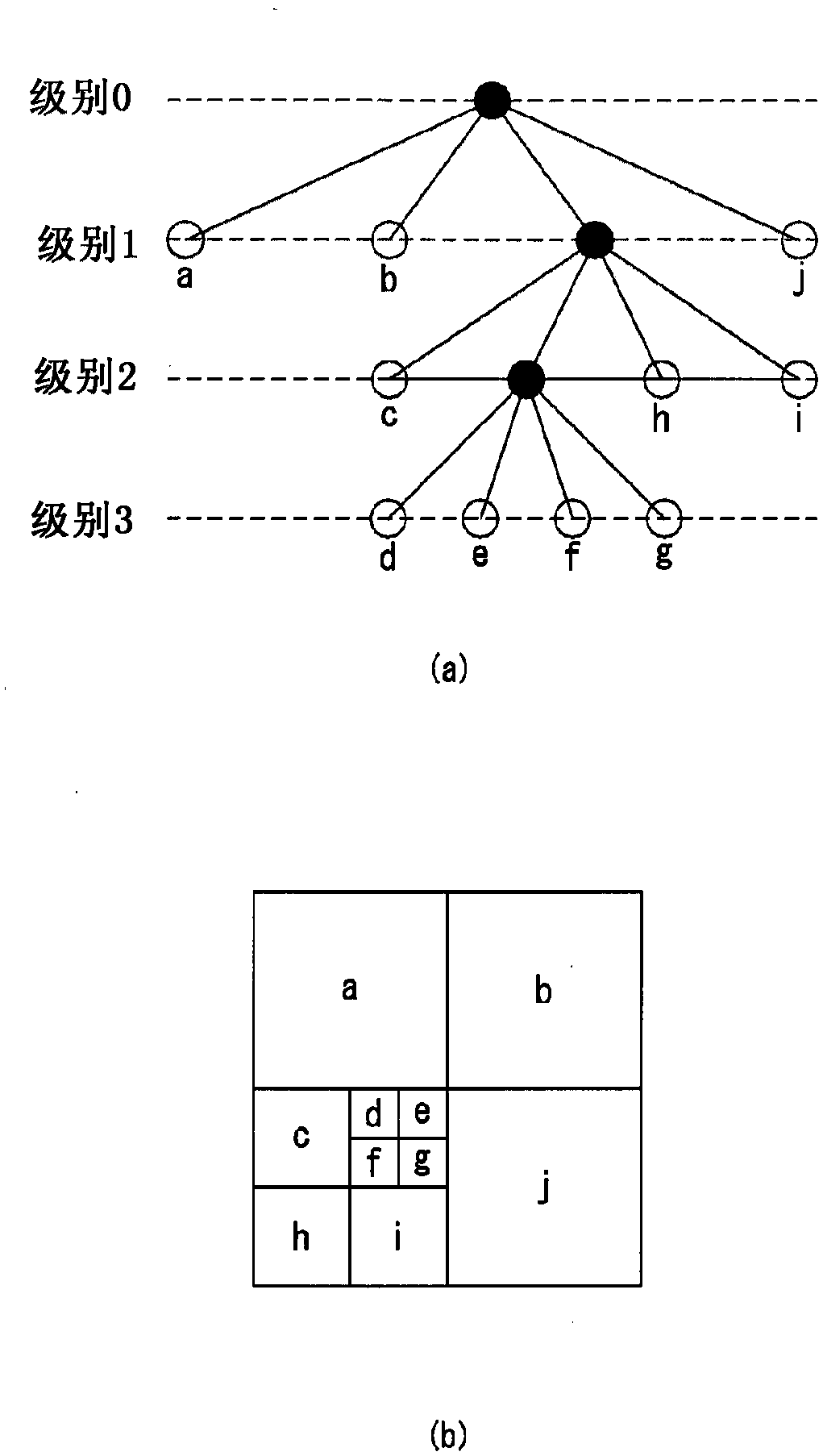

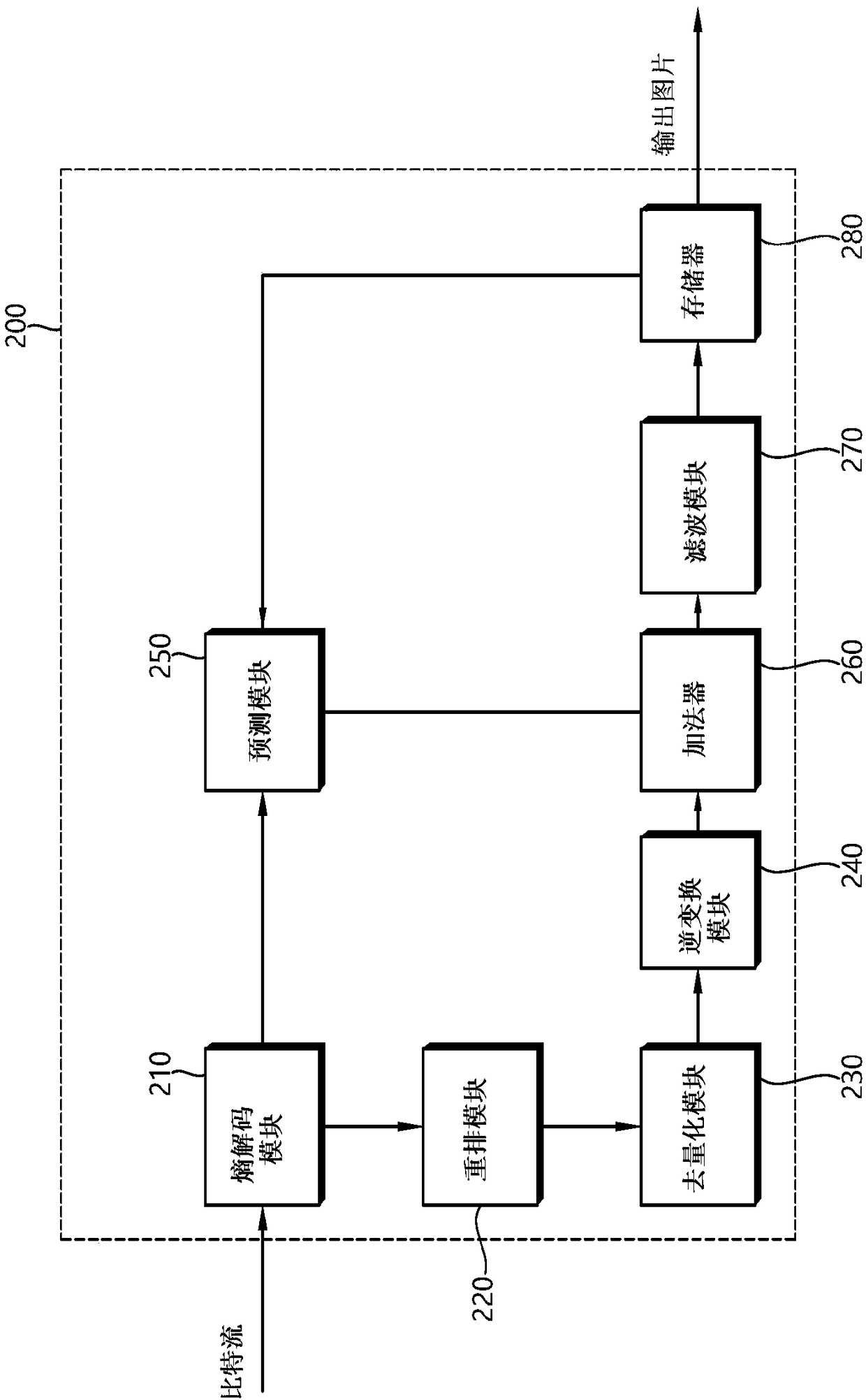

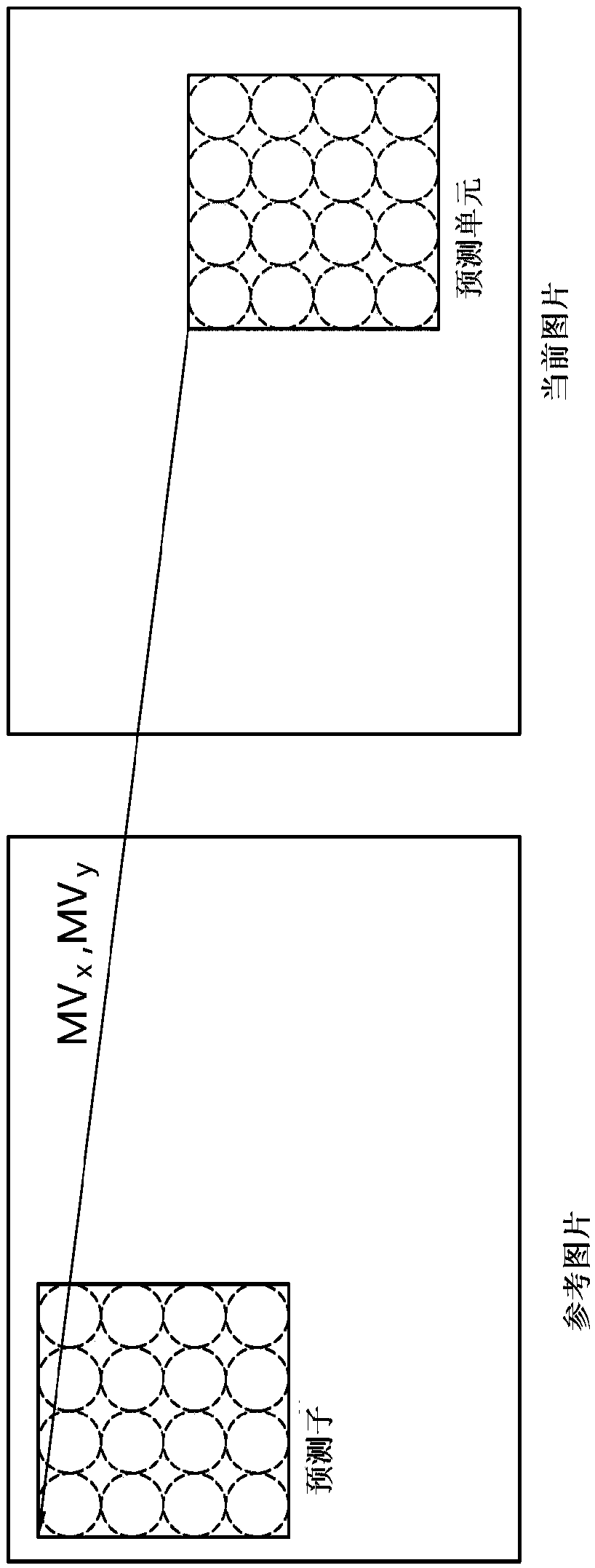

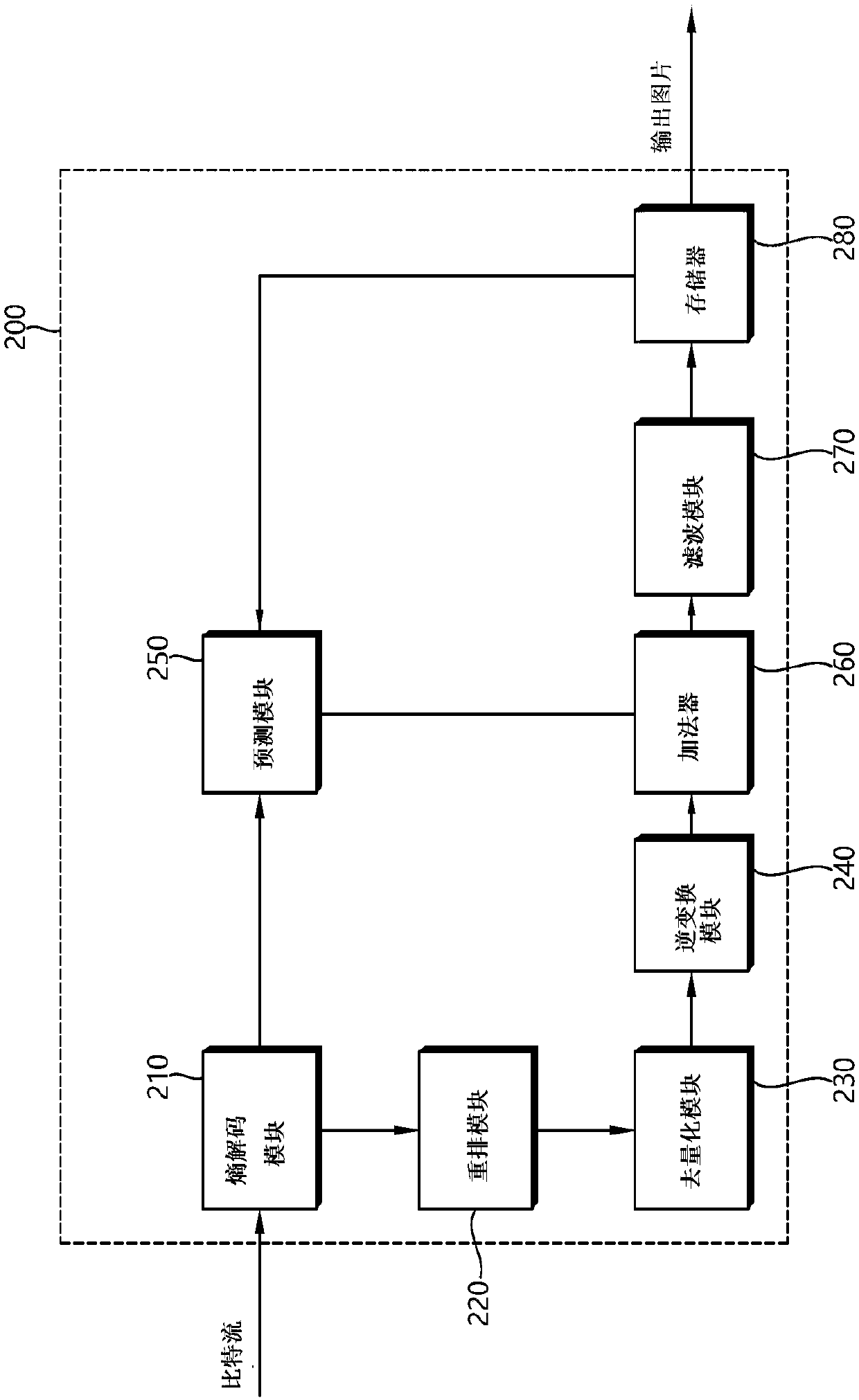

Inter prediction method and apparatus in video coding system

ActiveCN108141582AImprove forecasting efficiencyEfficient derivationDigital video signal modificationMotion vectorInter frame

A video decoding method performed by a decoding apparatus according to the present invention comprises the steps of: deriving control points (CP) for a current block; acquiring movement vectors for the CPs; deriving a sample unit movement vector in the current block on the basis of the acquired movement vectors; and deriving a prediction sample for the current block on the basis of the sample unitmovement vector. According to the present invention, it is possible to effectively perform, through sample unit motion vectors, inter-prediction not only in a case where an image in the current blockis plane-shifted but also in a case where there are various image distortions.

Owner:LG ELECTRONICS INC

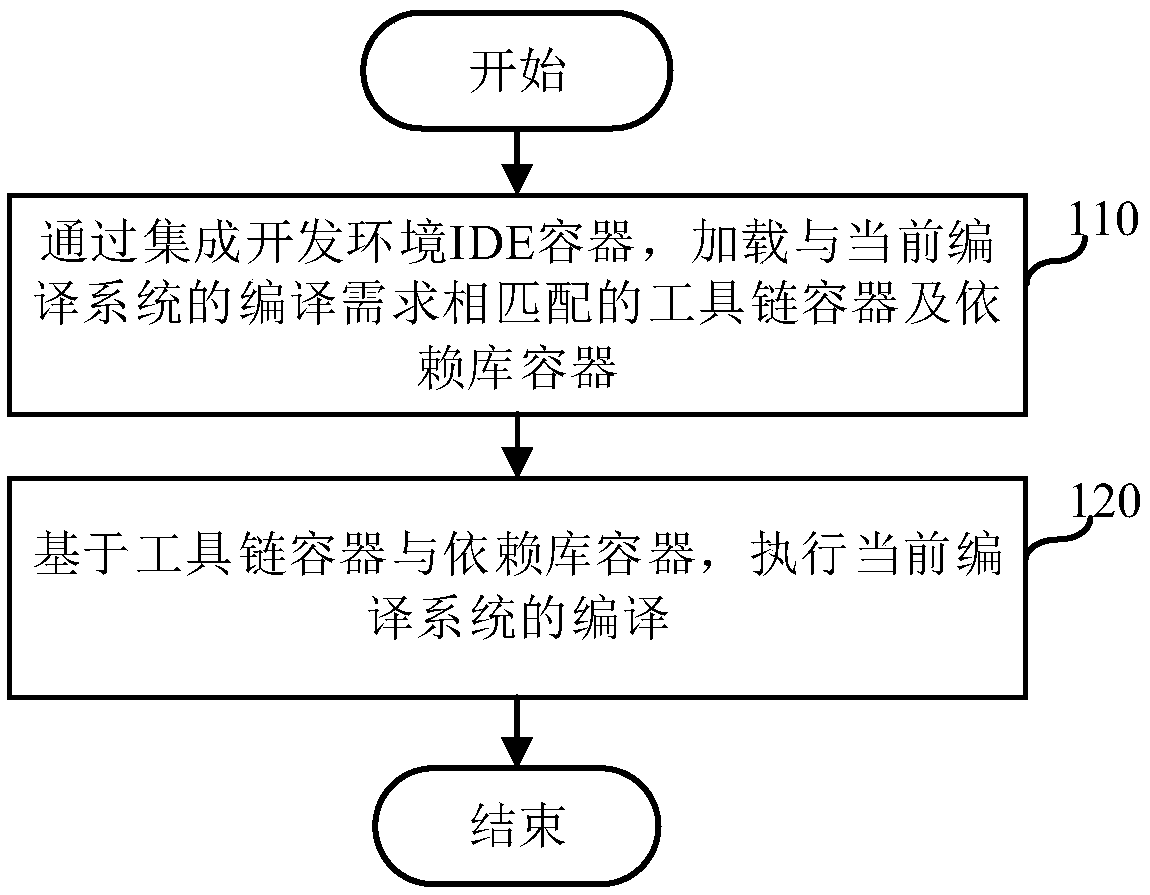

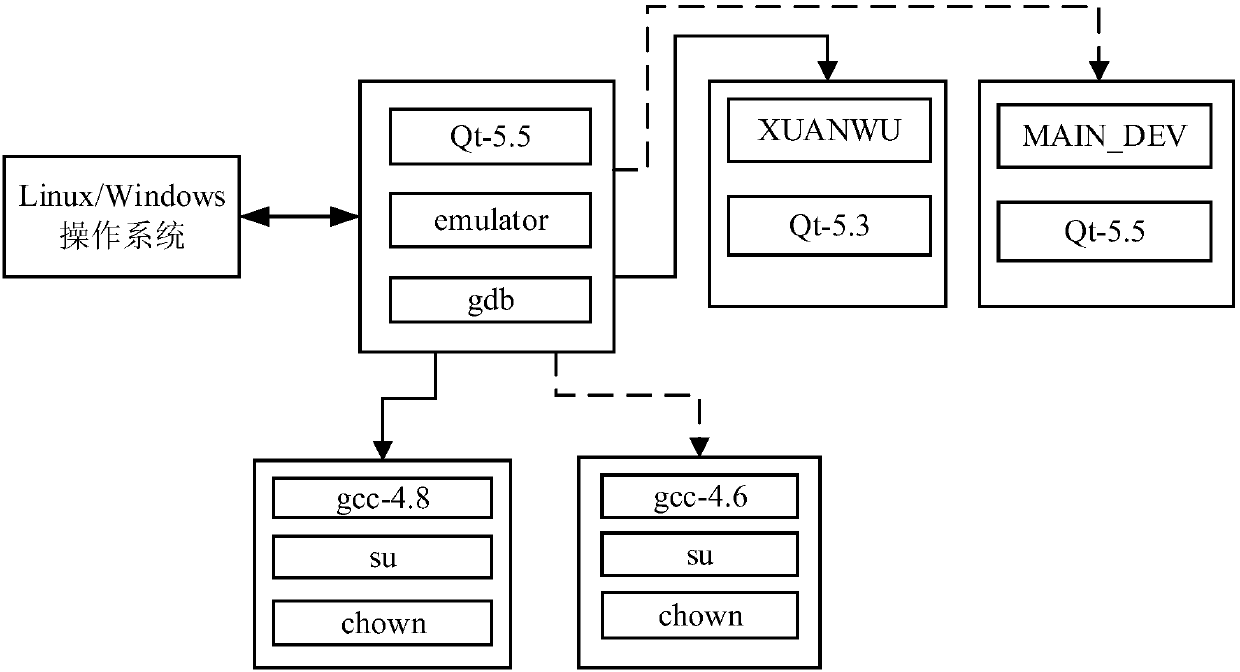

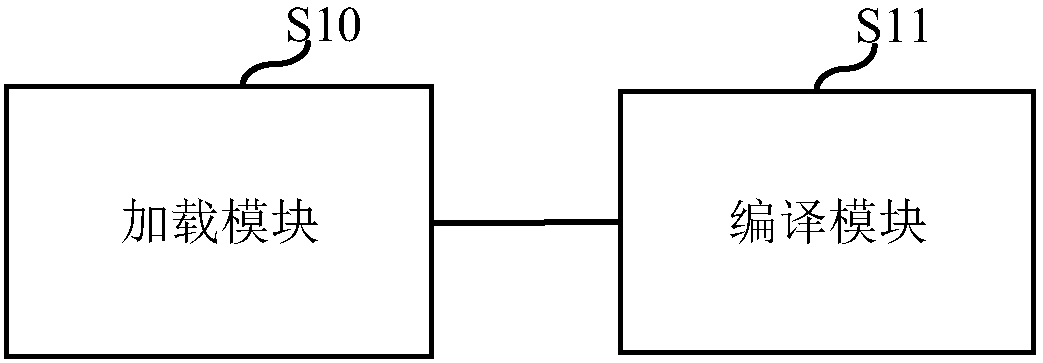

Compiling method and device of compiling system and terminal equipment

ActiveCN107741851AAvoid the problem of extreme dependenceSolve the problem of low efficiency of multi-branch compilationCode compilationOperational systemSoftware engineering

The embodiment of the invention provides a compiling method and device of a compiling system and terminal equipment. The compiling method of the compiling system includes the steps that through an integrated development environment (IDE) container, a tool chain container and a dependent library container which meet the compiling requirements of the current compiling system are loaded; the tool chain container and the dependent library container execute compiling of the current compiling system. By the adoption of the compiling method, the integrated development environment (IDE) container canload the matched tool chain container and dependent library container, then, compiling environments, capable of meeting different compiling requirements, of the current compiling system can be established, not only is extreme dependence on operation system environments effectively avoided when the compiling environments are established by setting environment variables and chroot, but also the compiling environments capable of meeting different compiling requirements are established on the basis of the tool chain container and the dependent library container, separation of the compiling environments is achieved, and the problem is effectively solved that the efficiency of multi-tool-chain and multi-branch compiling is low.

Owner:北京元心君盛科技有限公司

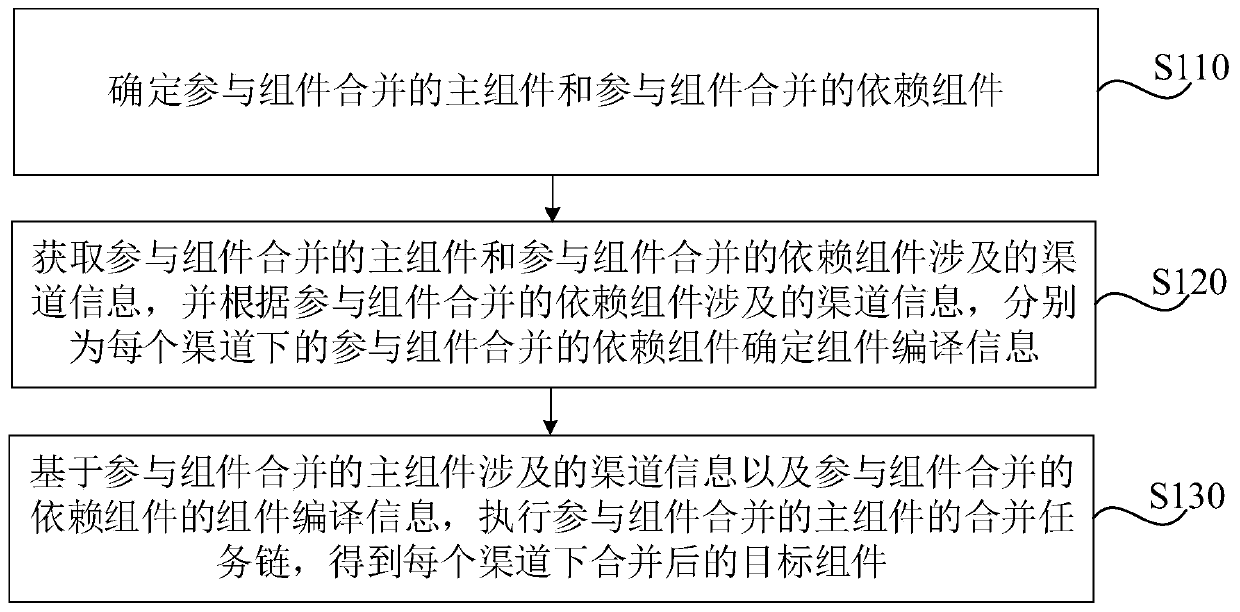

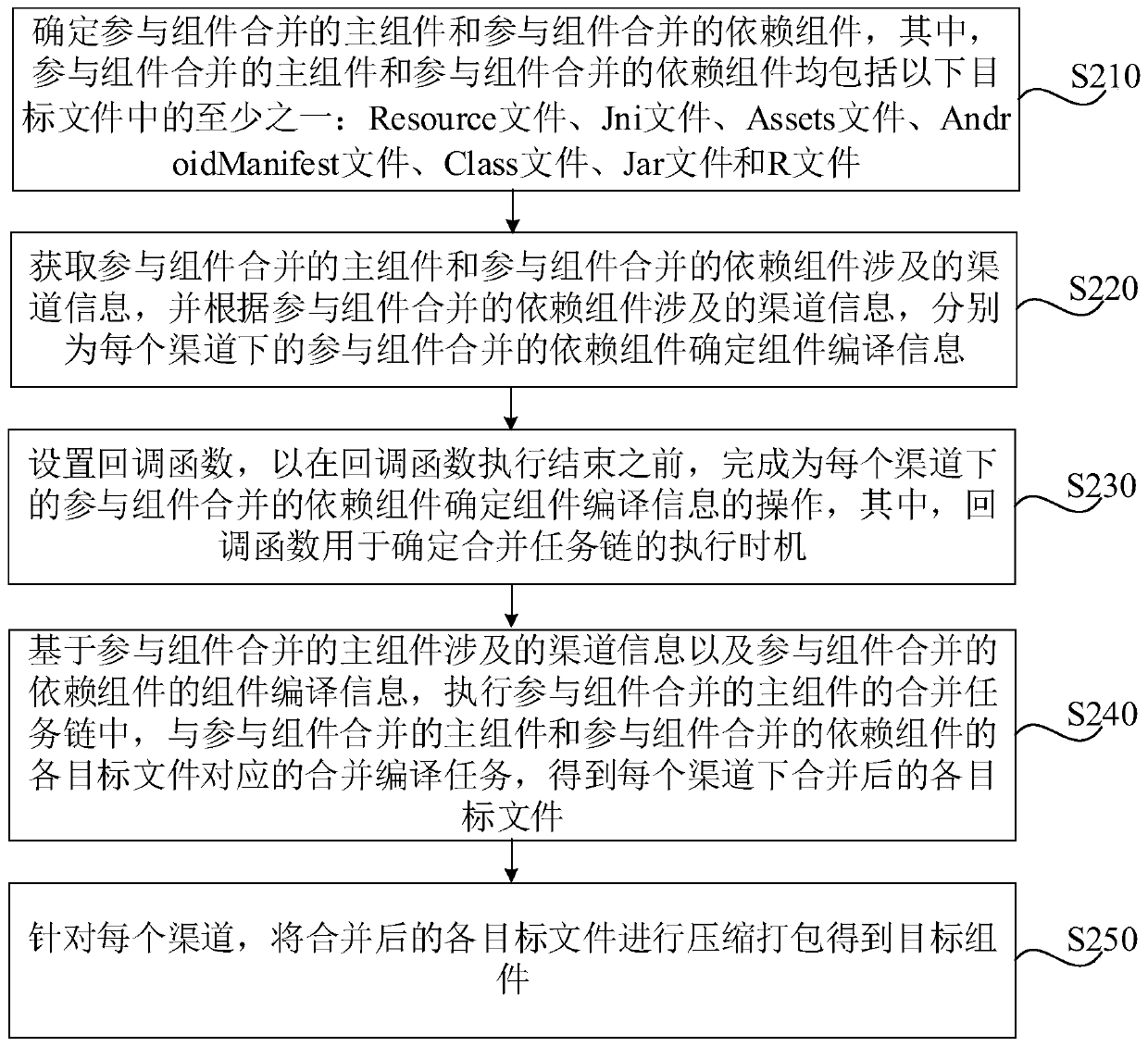

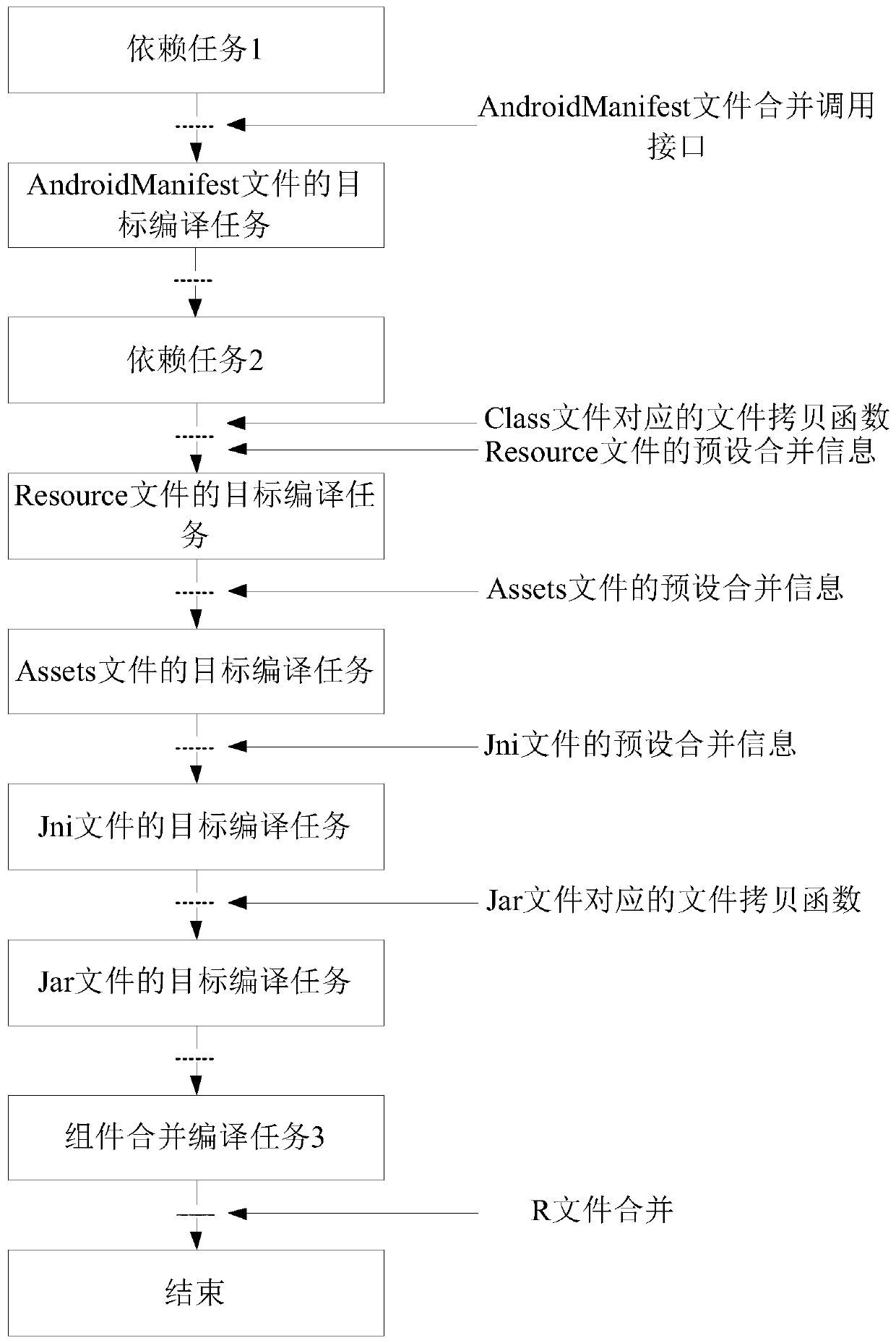

Modularized merge compiling method and device, equipment and storage medium

ActiveCN110457045AImprove compilation efficiencyMeet the needs of component developmentEnergy efficient computingSoftware deploymentSoftware developmentComputer science

The embodiment of the invention discloses a modularization merging and compiling method and device, equipment and a storage medium, and the method comprises the steps: determining a main assembly participating in assembly merging and a dependent assembly participating in assembly merging; obtaining channel information related to the main component participating in component merging and the dependent component participating in component merging, and determining component compiling information for the dependent component participating in component merging under each channel according to the channel information related to the dependent component participating in component merging; and based on the channel information involved in the main component participating in component merging and the component compiling information of the dependent component participating in component merging, executing a merging task chain of the main component participating in component merging to obtain a mergedtarget component under each channel. According to the embodiment of the invention, merging and compiling of related components of the software development kit based on the channel information can be realized, and the engineering compiling efficiency is improved.

Owner:BAIDU ONLINE NETWORK TECH (BEIJIBG) CO LTD

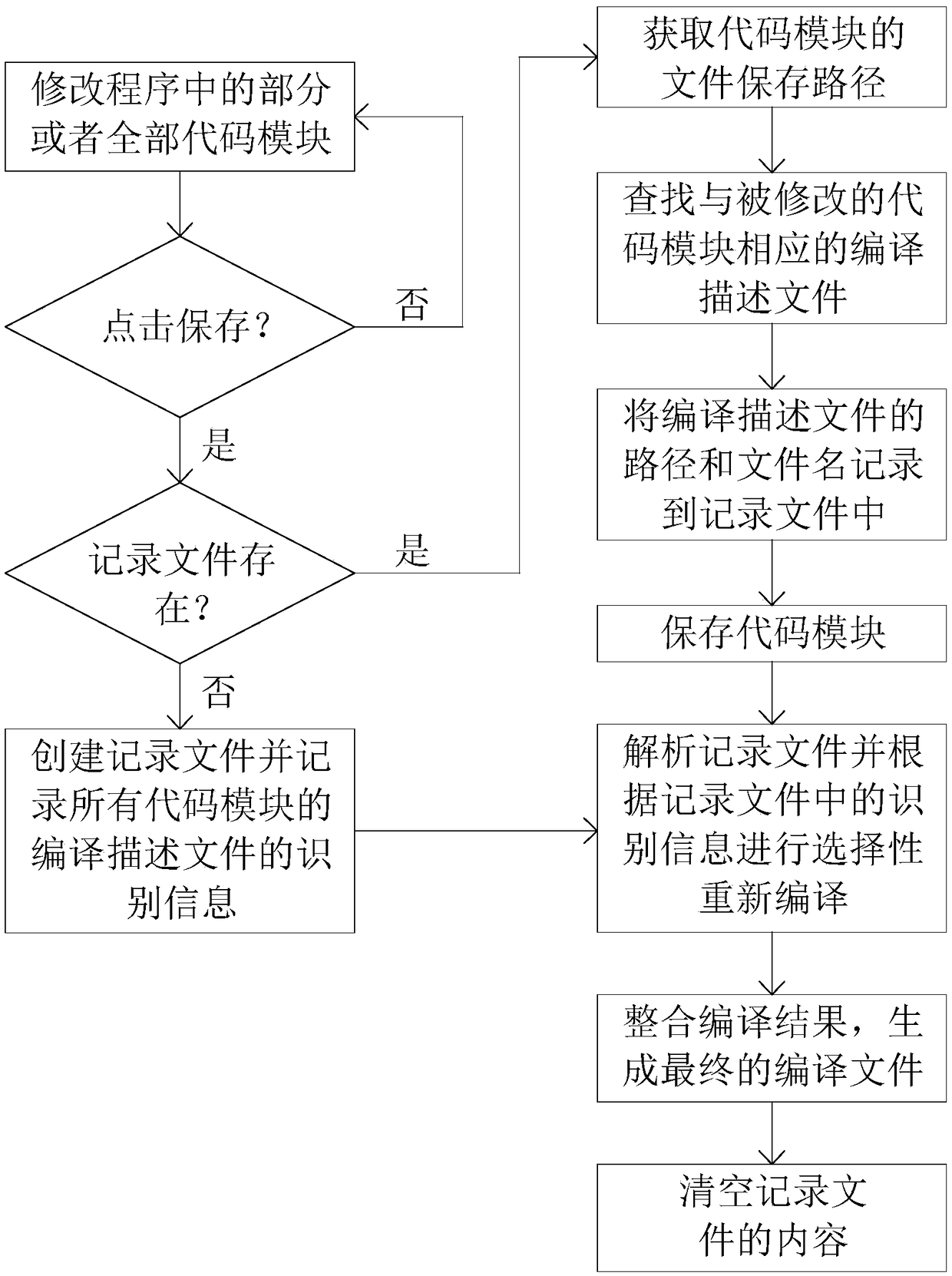

Code compiling method and device

InactiveCN108897545ARealize automatic recordingGuaranteed compilation accuracyCode compilationProgramming languageCode module

The invention relates to the technical field of code compiling and particularly discloses a code compiling method and device, wherein the method includes the following steps: modifying some or all ofthe code modules in a program; recording identifying information of a compiled description file corresponding to the modified code modules in a record file; when compiling the program, recompiling with the code modules corresponding to the compiled description file recorded in the record file, and performing the last compilation result with the code modules corresponding to the compiled description file not recorded in the record file. The code compiling method has the advantages that by setting the record file to record the identifying information of the compiled description file corresponding to the modified code modules, the goal of recording the modified code modules is attained and automatic recording after modifying the codes is achieved; in addition, only the modified code modules are recompiled, which can ensure correct rate of compiling and increase compiling efficiency.

Owner:NANCHANG HUAQIN ELECTRONIC TECH CO LTD

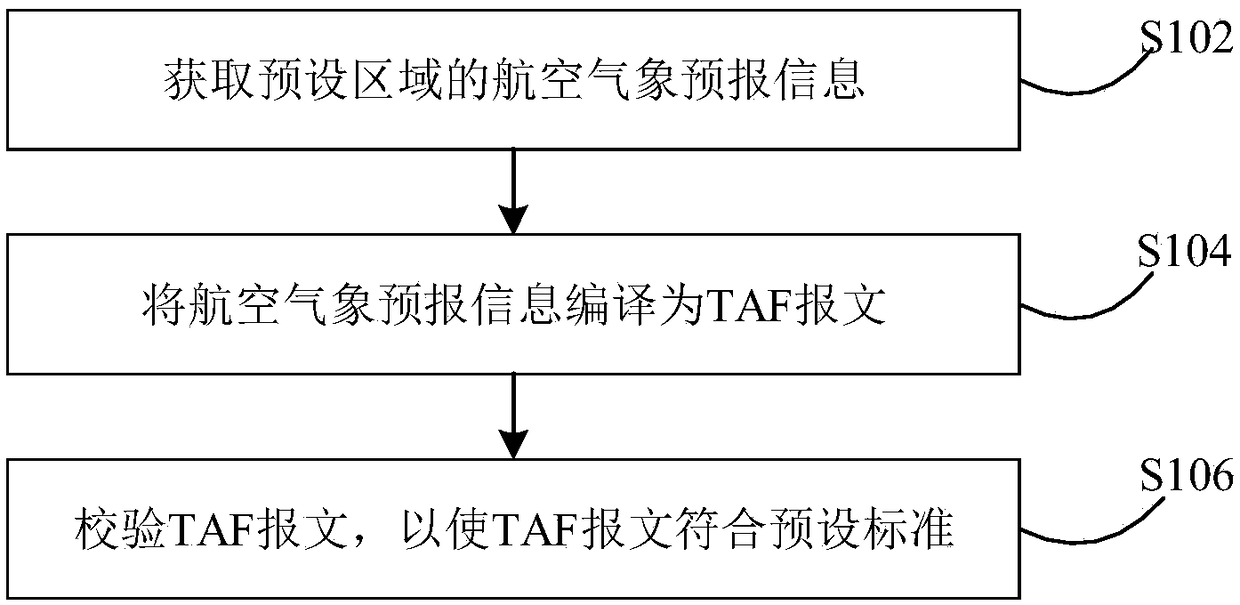

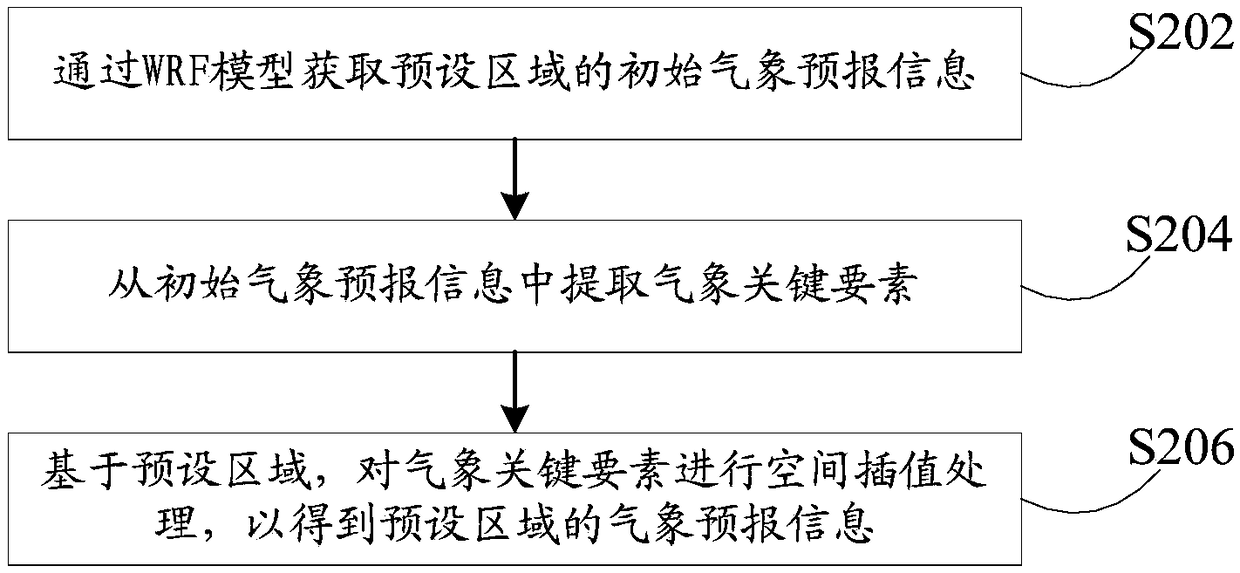

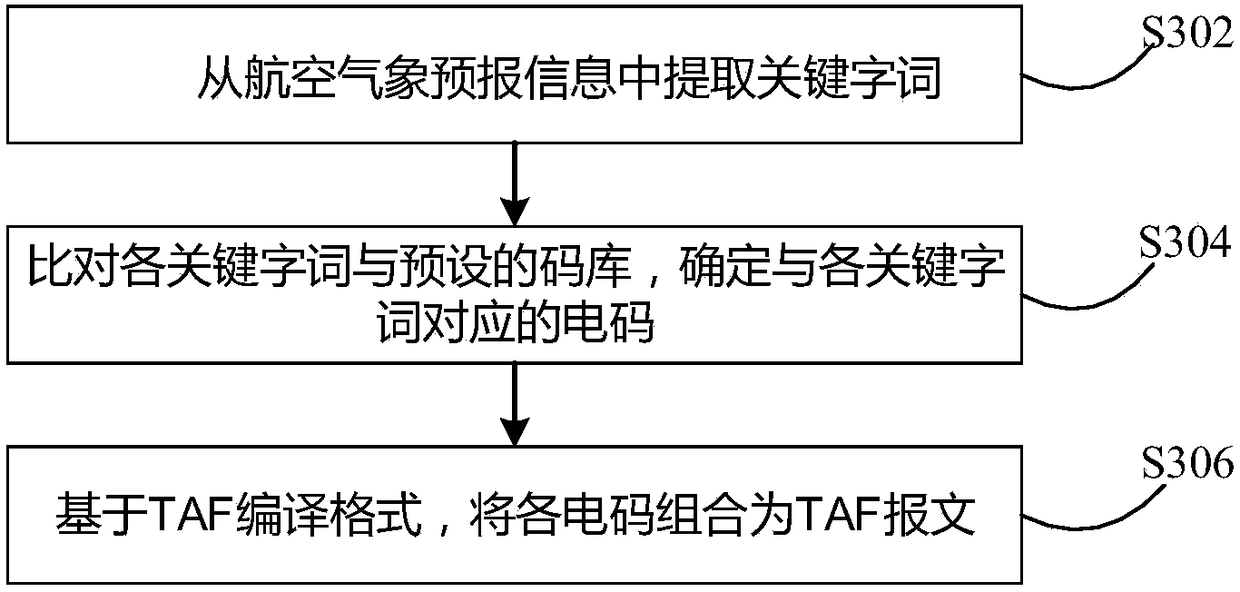

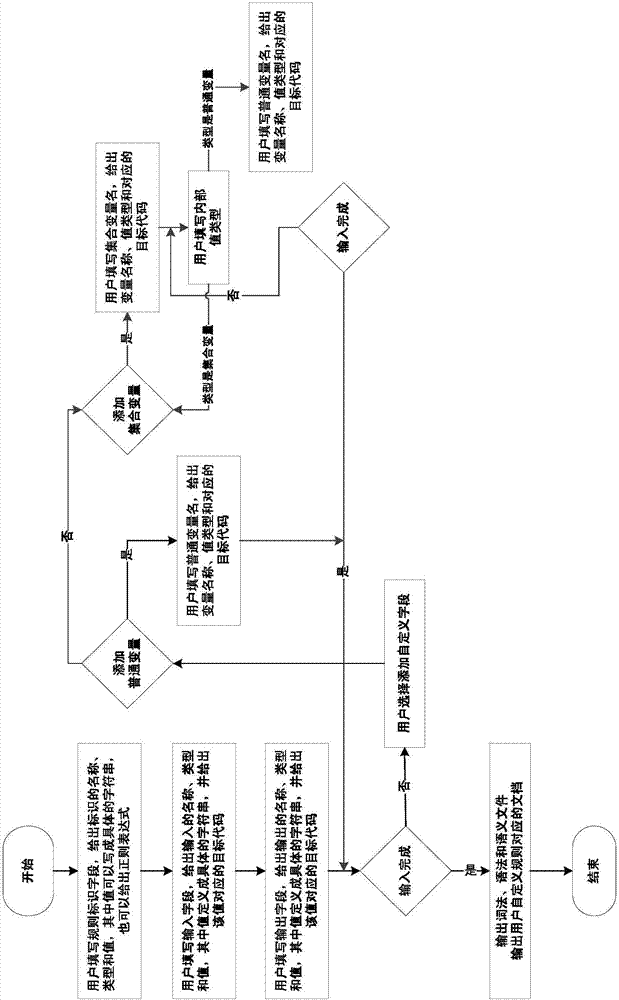

TAF message automatic compilation method and system of aeronautical meteorology, and terminal

InactiveCN108418822AImprove compilation efficiencyLow efficiencyNeural architecturesTransmissionAviationComputer science

The invention provides a TAF message automatic compilation method and system of aeronautical meteorology, and a terminal, and relates to the technical field of the aeronautical meteorology forecast. The method is applied to a smart terminal, and comprises the following steps: acquiring aeronautical meteorology forecast information of a preset region; compiling the aeronautical meteorology forecastinformation into a TAF message; and checking the TAF message to enable the TAF message to meet the preset standard. Through the method provided by the invention, the obtained aeronautical meteorologyforecast information can be automatically compiled as the TAF message meeting the preset standard, thereby effectively improving the compiling efficiency of the TAF message.

Owner:杜刚

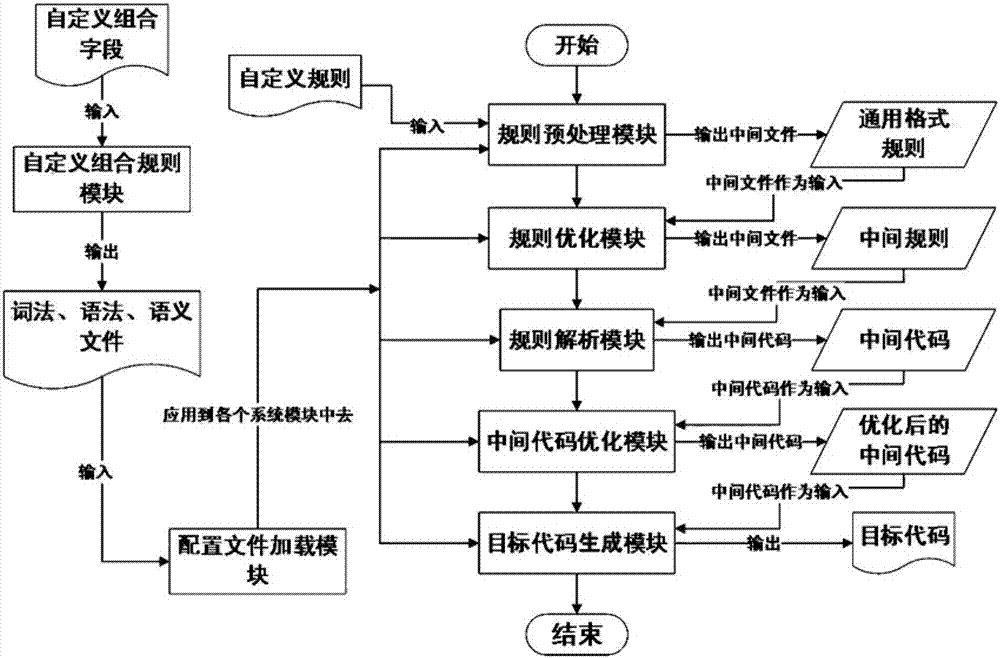

Compiling optimization method and system oriented to customized rule file

ActiveCN107291522AAddress the need for flexible configurationImprove scalabilityProgram controlMemory systemsExtensibilityUser input

The invention discloses a compiling optimization method and system oriented to a customized rule file. All combined fields are uniformly put in a grammar to be processed, a text file is used for storing the result value of the field, so that type judgment only needs to be carried out during compiling, and different requirements are realized for different types. On one hand, physical memory is saved, and on the other hand, a code does not need to be revised. After a corresponding grammar frame is built, user input can be revised to control a compiling process, and the expandability of the system is greatly improved. Since an extensible grammar is used, the rule can be flexibly formed, and requirements that a code generation rule is flexibly configured can be solved. Meanwhile, due to the flexibility and the customized universality of the grammar structure, partial preprocessing optimization is carried out on an aspect of text, and compiling efficiency can be greatly improved.

Owner:INST OF INFORMATION ENG CHINESE ACAD OF SCI

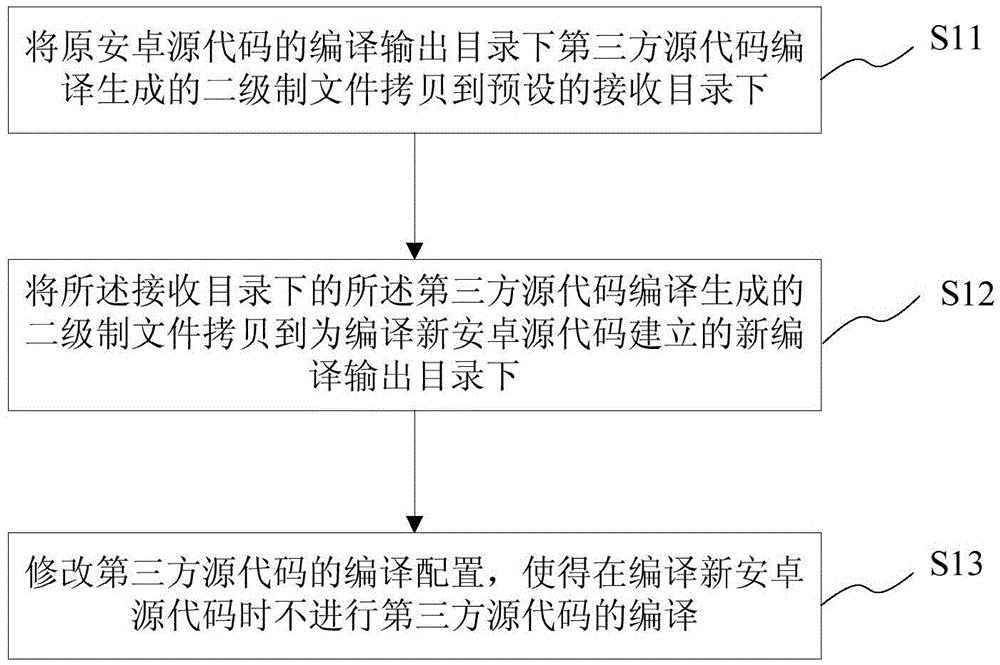

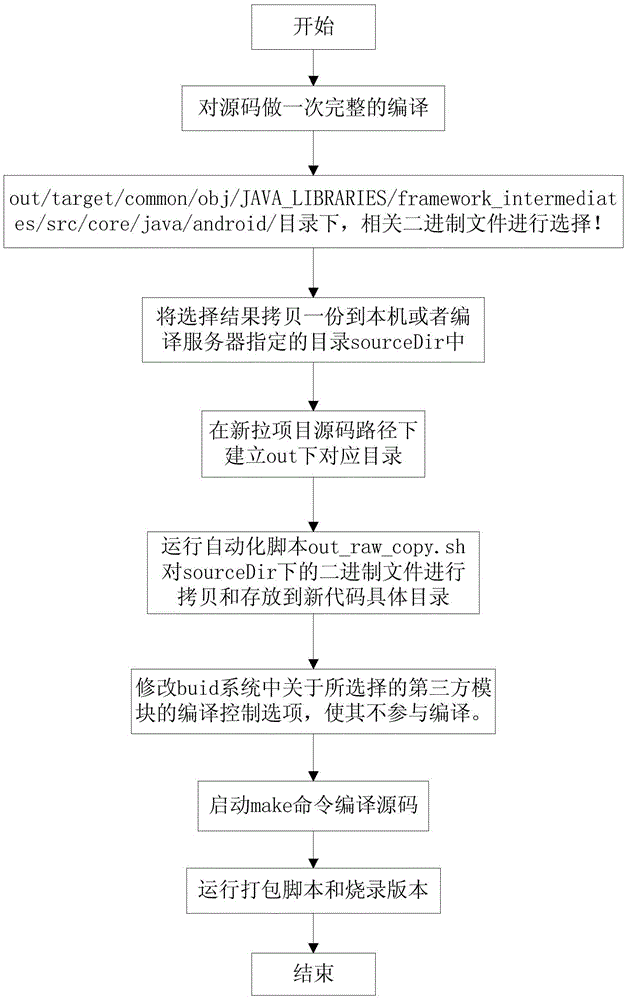

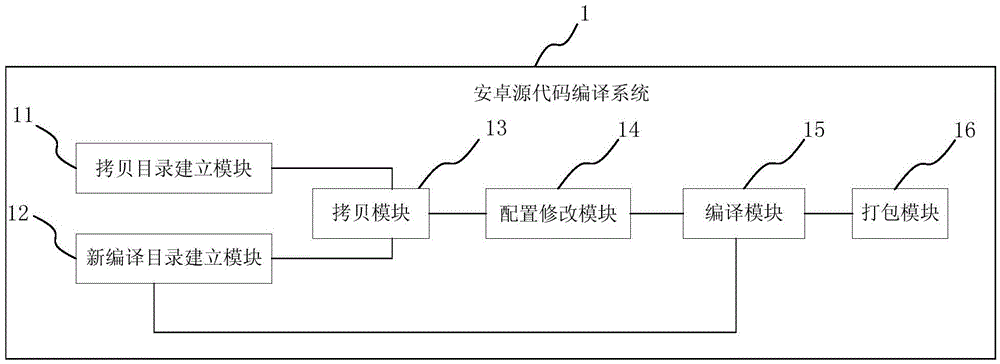

Android source code compiling method and system

ActiveCN105468428ASave compilation timeImprove compilation efficiencySoftware engineeringProgram controlSource codeCompile time

The invention provides an Android source code compiling method and an Android source code compiling system. The Android source code compiling method comprises the steps of copying a binary file generated through compiling a third party source code under the compilation output directory of an original Android source code to a preset receiving directory; copying the binary file generated through compiling the third party source code under the receiving directory to a new compilation output directory established for compiling the new Android source code; and modifying the compilation configuration of the third party source code, thus invalidating the compilation of the third party source code when compiling the new Android source code, and packaging the software version corresponding to the new Android source code after the new Android source code is compiled. The Android source code compiling method can greatly save compiling time and improve compiling efficiency, and is simple to operate and high in practicability.

Owner:台州市吉吉知识产权运营有限公司

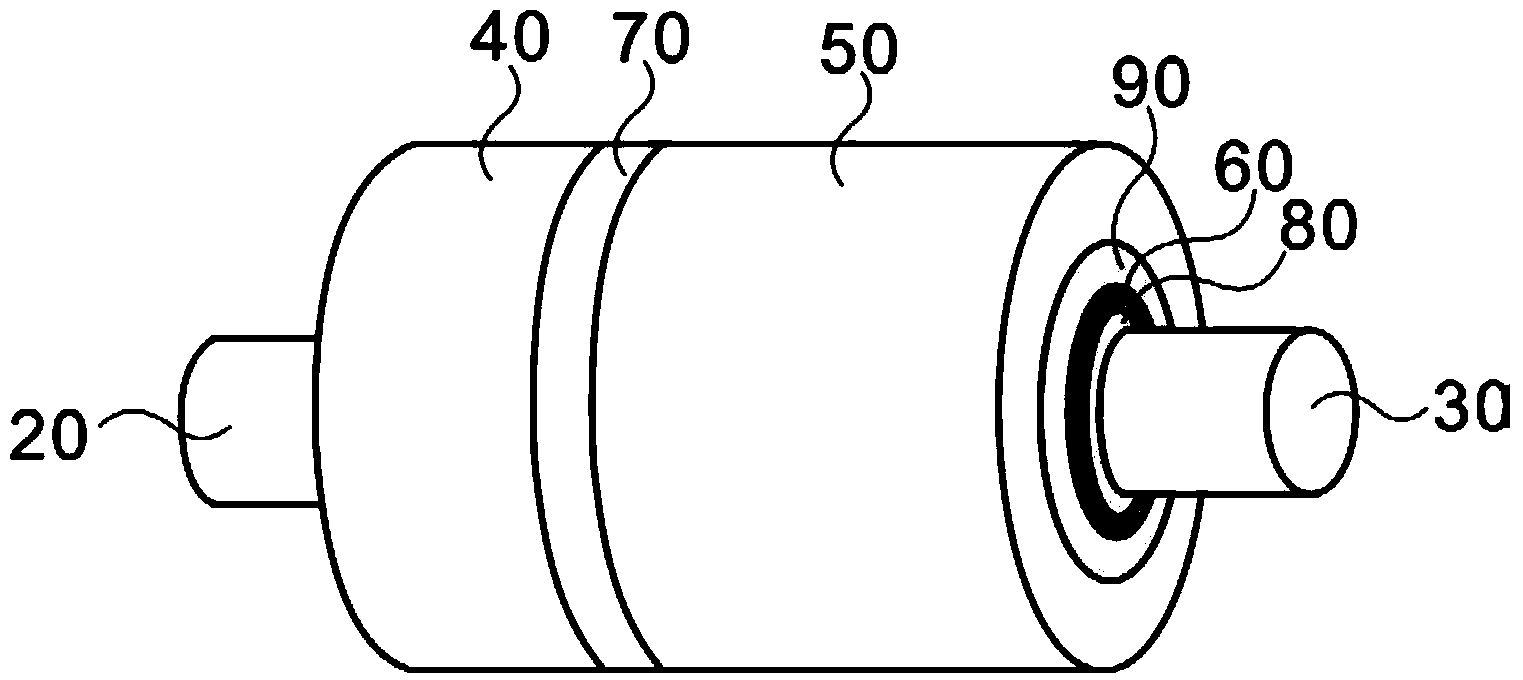

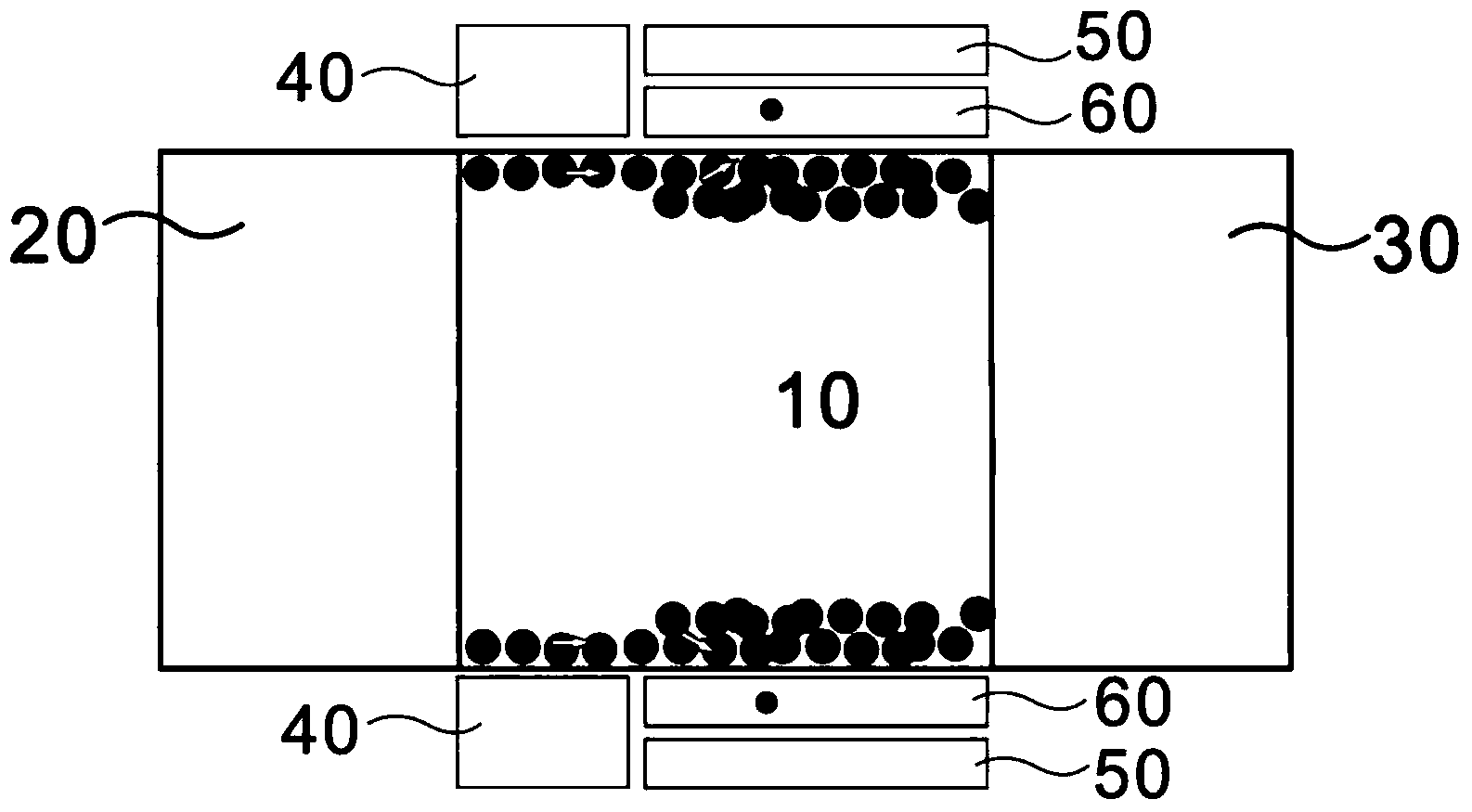

SONOS (silicon oxide nitride oxide silicon) flash memory device and compiling method thereof

ActiveCN104332471AReduce read errorsReduce critical sizeSolid-state devicesSemiconductor/solid-state device manufacturingSilicon oxideNitride

The invention provides an SONOS (silicon oxide nitride oxide silicon) flash memory device and a compiling method thereof. The SONOS flash memory device comprises a substrate of a cylinder structure and a grid electrode which wraps the middle of the substrate, wherein a source terminal and a drain terminal are respectively arranged at two ends of the substrate, the grid electrode comprises a first silicon gate and a second silicon gate which are parallel, a first oxidation layer is arranged between the first silicon gate and the second silicon gate, and a second oxidation layer arranged on the substrate, a silicon nitride layer arranged on the second oxidation layer and used to store electric charges and a third oxidation layer arranged on the silicon nitride layer are sequentially arranged between the second silicon gate and the substrate. The above structure of the SONOS flash memory device can restrain short channel effects and resist threshold voltage drifts, and simultaneously can effectively reduce the critical size of the SONOS flash memory device. The compiling method of the SONOS flash memory device assists in movement of thermion by adjusting voltage of the grid electrode and the drain terminal, provides sufficient oxidation layer crossing energy to complete compiling, improves compiling efficiency of the SONOS flash memory device, and reduces compiling electric current power consumption.

Owner:SHANGHAI HUALI MICROELECTRONICS CORP

Inter prediction method and device in video coding syste

ActiveCN107925758AImprove forecasting efficiencyEfficient derivationDigital video signal modificationMotion vectorInter frame

According to the present invention, a video decoding method performed by a decoding device comprises the steps of: deriving control points (CPs) for a current block; acquiring motion vectors for the CPs; deriving a sample-unit motion vector in the current block on the basis of the acquired motion vectors; deriving a prediction sample for the current block on the basis of the sample-unit motion vector; and generating a restoration sample on the basis of the prediction sample, wherein coordinates of a bottom-right sample position of the current block are (0, 0), and coordinates of CP0 among theCPs are (0, 0). According to the present invention, inter prediction can be effectively performed through sample-unit motion vectors even when an image in a current block is planarly moved and when the image is variously changed, and since motion vectors for CPs can be derived on the basis of already decoded neighboring blocks, a data amount for information on the motion vectors for the CPs and for a residual signal for the current block can be removed or reduced, and overall coding efficiency can be improved.

Owner:LG ELECTRONICS INC