A decoding method for block low-density check code and reconstruction of multi-mode decoder

A low-density check code and low-density check technology, which is applied in the field of high-speed broadband wireless digital communication, can solve the problems of fixed data throughput, large storage resources, and no consideration of requirements, so as to improve data throughput and utilization rate , read and write access control simple effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0059] Such as Figure 7 As shown, the 3 / 4 code rate block low-density parity check matrix in this embodiment.

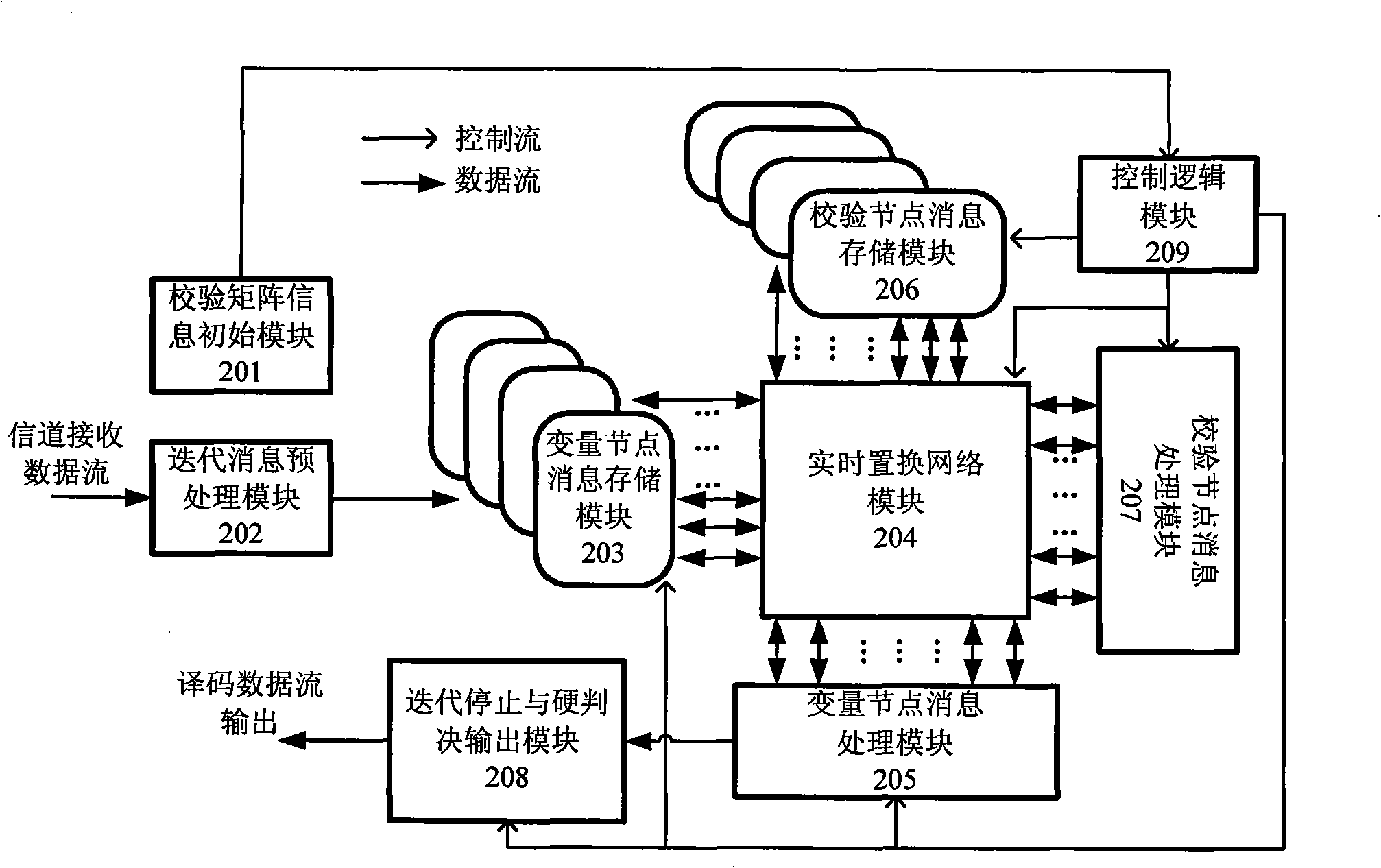

[0060] In the embodiment, the check matrix information initialization module will set the low density check matrix information and the configurable parameters in the decoding process:

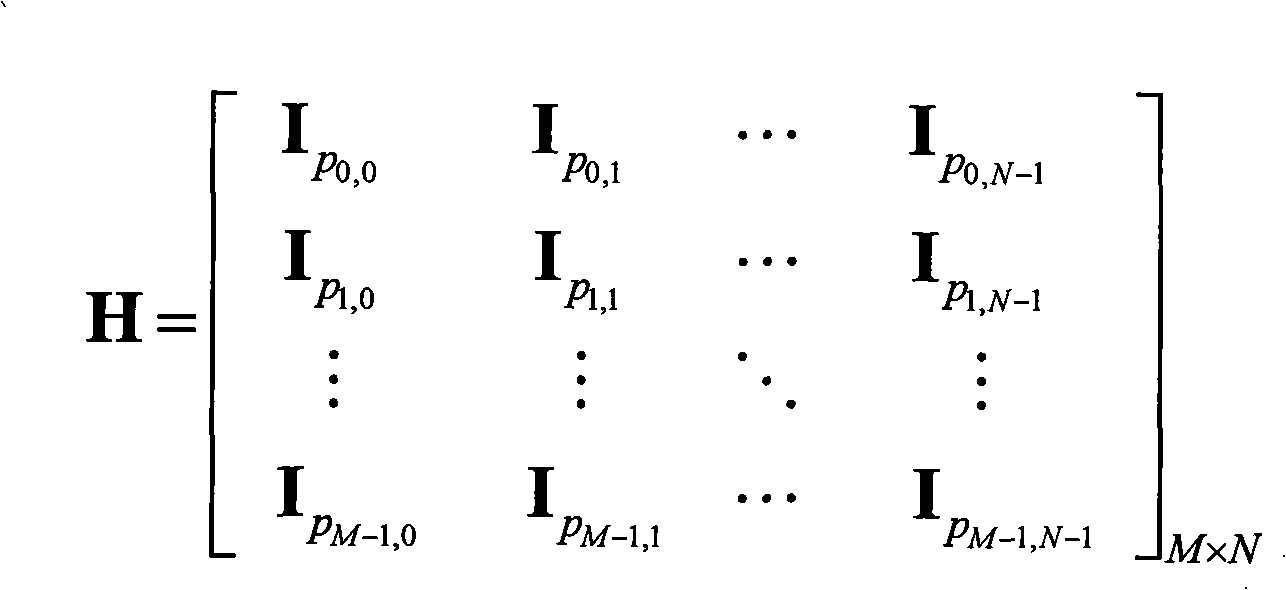

[0061] 1) The number of matrix row blocks is M=8, the number of column blocks is N=32, wherein the size of each sub-block is 256X256, and the element value is P i ;

[0062] 2) Set the maximum number of iterations of decoding ITER max =15; set the parallel factor Zf=32, then the variable node and check node message distributed memory block number is 32; The number of variable node message units is 32;

[0063] Set the variable node degree distribution vector as:

[0064] V → = [ 3,3,3,3,3,3,3,3,3,3,3,3,3,3,3,3,5,5,5,5,5,5,5,3,2,2,2,2,2,2,2,2 ] ;

[0065] Set the check node degree di...

Embodiment 2

[0091] Such as Figure 9 As shown, the 1 / 2 code rate block low-density parity check matrix in this embodiment.

[0092] In the embodiment, the check matrix information initialization module will set the low density check matrix information and the configurable parameters in the decoding process:

[0093] 1) The number of matrix row blocks is M=16, the number of column blocks is N=32, wherein each sub-block size is 256X256, and the element value is P i ;

[0094] 2) Set the maximum number of iterations of decoding ITER max =15; set the parallel factor Zf=64, then the variable node and check node message distributed memory block number is 64, the size of the real-time cycle permutation network is 64, and the number of stages is 6; the check node and check node working in parallel The number of variable node message units is 64;

[0095] Set the variable node degree distribution vector as:

[0096] V → = [ 3...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More