Method for constructing network on three-dimensional chip

An on-chip network and network topology technology, applied in the application field of integrated circuit chips, can solve the problems of large network delay and low throughput, and achieve the effect of small network delay, low average number of hops, and avoidance of congestion.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

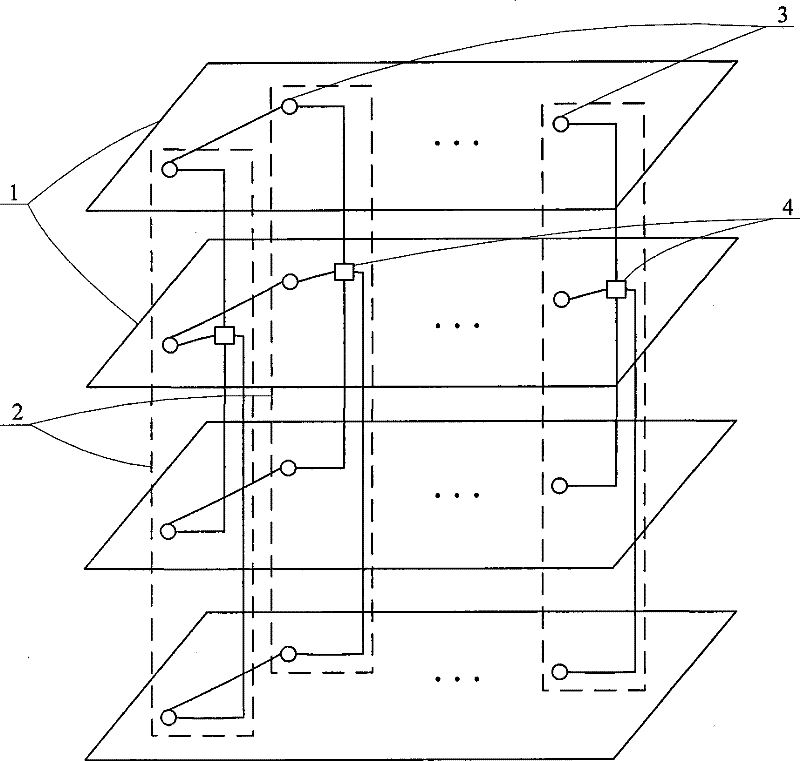

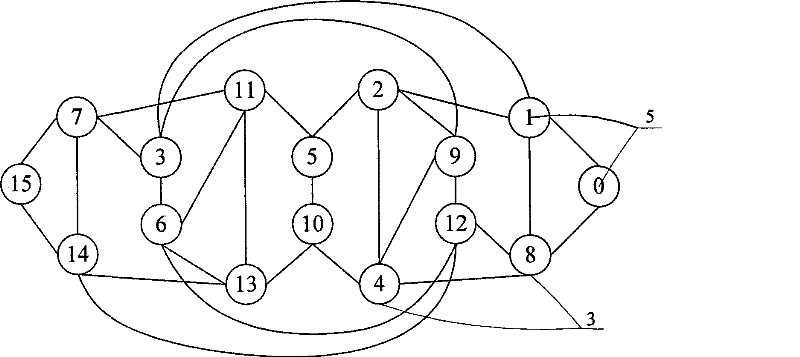

[0064] figure 1 There are 16 nodes in each horizontal layer in the network shown, figure 2 The node numbers of any one of the layers are shown. Nodes numbered 1 on each layer are connected to the same switching unit (type B node), nodes numbered 2 on each layer are connected to the same switching unit (type B node), and so on, each layer is numbered as 16 nodes are all connected to the same switching unit (type B node), in fact, each switching unit can be distributed on any horizontal plane.

[0065] From the source node with the address (1, 3) (the node whose horizontal number is 1 on the third level, the horizontal number starts from 0.) to the target node with the address (15, 2) (the node with the horizontal number on the second level The node numbered 15) transmits data packets as an example to introduce the process of data packet transmission from the network.

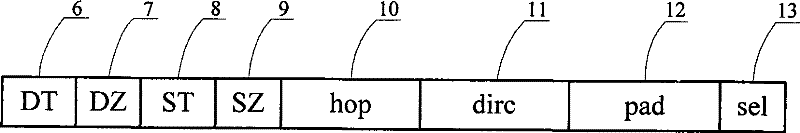

[0066] The data packet sent by the processing unit in the source node (1, 3) is first delivered to the rou...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More